近期基于NXP LS1046调试了两个PHY芯片:YT8521 YT8614。在期间遇到了不少坑。

硬件上LS1046 用了三个8521 一个8614,两路RGMII 一路SGMII,8614用的QSGMII。

首先得确认PHY ID ,方便mdio总线调试寄存器,代理商提供了裕泰得内核驱动,但是也因为这个驱动文件引入了很多问题。

问题1 YT8614的丢包。

在压流测试中,测出YT8614有少量丢包,特别是小字节包传输很容易丢;具体测试使用iperf3 V3.12,它具备TCP retr重传的统计计数。这个问题有一个现象:

PHY自己统计的收发帧数是正确的,但是LS1046 MAC层统计的帧就是少,起初我以为是LS1046硬件设计干扰问题,在经历一番排查后,锁定到是PHY自身引起的。

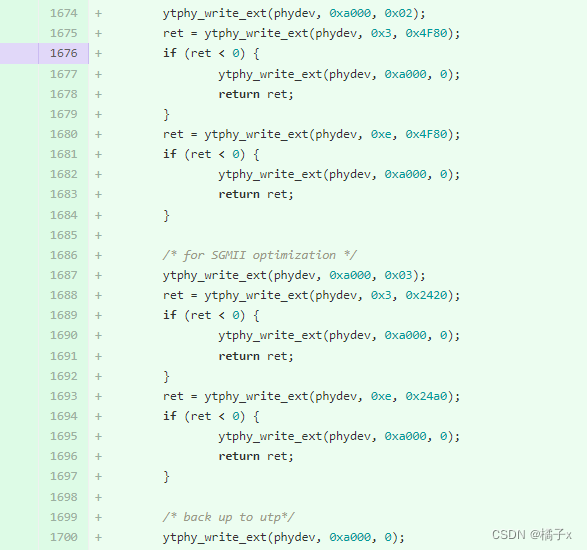

幸运的是我们有其他ARM平台也在使用裕泰芯片,在比对驱动文件后发现代理商给我们的驱动少了些配置:

但是这些配置很无语,写的寄存器在手册上的描述是PHY ID ,还是个只读寄存器;另外还有些寄存器是手册上查不到的。是芯片自己bug还是其它问题 已经不能得知了、毕竟小体量下FAE很难联系到。

同步配置后,问题解决。

问题2 down 网卡 对端链路网口灯不灭

直观问题就是ifconfig down 网口后,连接到对端的网卡link灯是亮的。

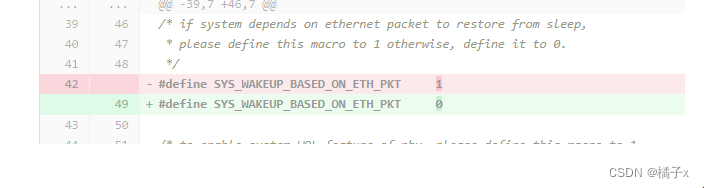

link灯是亮的说明PHY没down掉。在排查后确认需要修改驱动中的宏:

这个宏根据描述的猜测是PHY在kernel休眠时自己不关闭,好根据网络帧唤醒kernel。我们不需要此功能,需要它关闭,也就是对PHY寄存器power位进行更新。

问题3 对端的自协商关闭且强制100M速率时,SGMII 、QSGMII 网口无法link,两路RGMII网口正常。

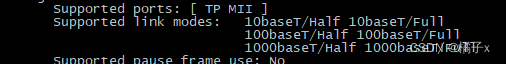

这个当时查起来挺匪夷所思,问题只发生在SRGMII QSGMII上,在使用ethtool观察网卡状态时发现只有RGMII支持100M、10M的半双工,其它网口都没有半双工这个信息。

问题在这个现象上就很好解释了,在IEEE的规范中,如果一端关闭自协商,对方只能探测到它的速率而2不能探测到它的双工模式。所以如果一端配置了100M 自协商关闭、对端自协商打开的情况下会link为:100M 半双工。由于这里SGMII又不支持半双工,所以link失败。

我们一度怀疑SGMII上不支持半双工,咨询了下硬件工程师被狠狠的嘲笑了一番。也就是说问题不出在SGMII上。

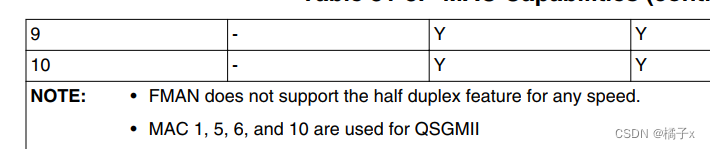

最终问题锁定在LS1046自身上,也在手册上看到了相关信息:

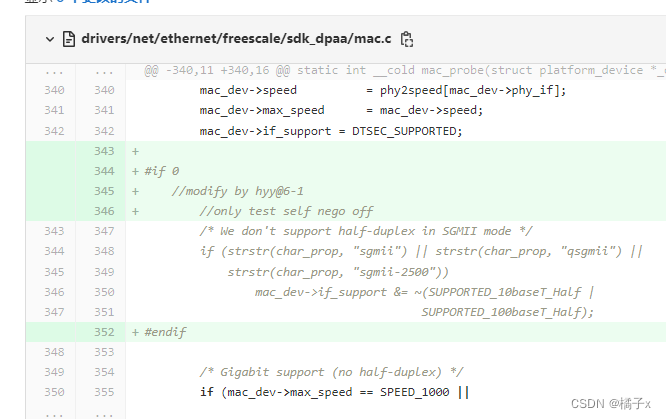

这里提到FMAN不支持所有速率半双工,在它的代码中只屏蔽了SGMII:

我得修改是把这里注释掉,以为在这种情况下半双工到全双工本身就有可能丢包。所以不考虑丢包问题,只要求它能link上。

重新编译kernel,测试问题解决。

问题4 一路RGMII down掉,另一路RGMII也受影响。

这个问题也够离谱的,两路RGMII 网口有牵连。

表现就是ifconfig down一个RGMII网卡,另一个RGMII 能收到帧,但是发不出来。

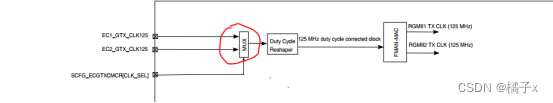

在排查后确认到我们RGMII的125M 两路TX时钟分别来自两路RGMII 8521芯片,这在硬件上看起来是没问题的。

但是在LS1046内部如图有125M TX时钟源整理,会在两个PHY 时钟中选择使用一个。

PHY 8521在正常工作下, 125M时钟输出给1046。如果在PHY down时这路时钟会停掉,停掉后自然就会干扰另一路RGMII发送。

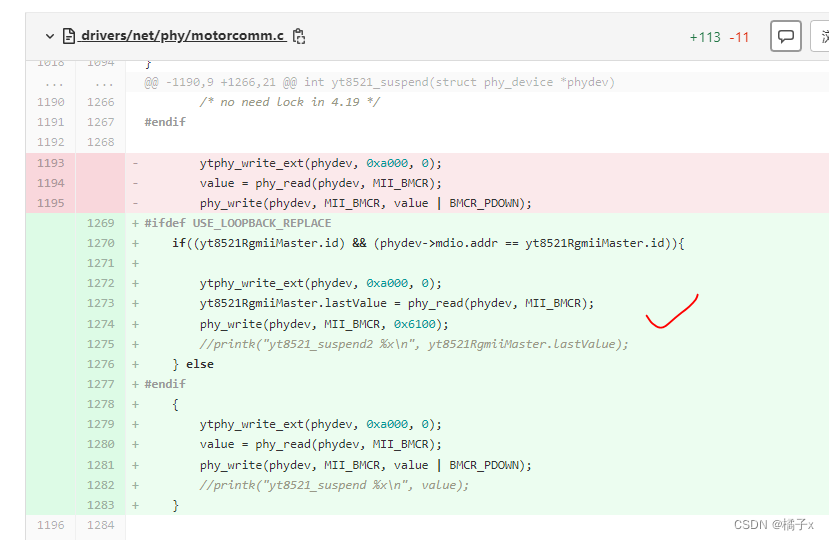

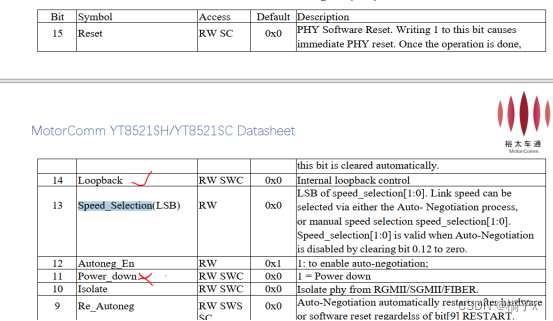

如果8521不停止125M输出 问题也不会发生,这一串的小问题引出了质变。

最终 我的解决措施是

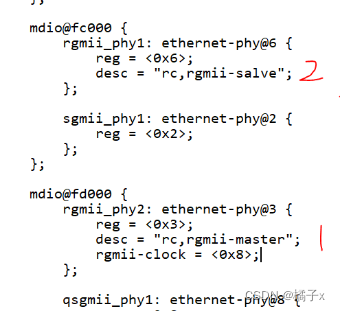

在设备树中指定两路RGMII PHY中的一路为“主要”1标记。

- “主要”节点下附带EC1 EC2 MUX选择寄存器配置,当配置为””0x8使用2路PHY 时钟。

- “主要”节点指定的PHY 在down 流程中使用内部loop back模式替代power down。

loop back模式下PHY 与对端link断开,125M时钟不会停止。

如此设计,将PLL源引至2路时钟,并且2路时钟在down流程中进入loopback模式,不会关闭125M时钟源,进而不会干扰1路。

借此,贴出以上问题作为后续参考。

WX:QNX12138

2009

2009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?