SPI 是 同步、串行、全双工、高速 通讯总线,采用主从模式(Master Slave)架构,一个 SPI 通讯系统必须且只能有一个主设备,提供时钟的为主设备(Master),接收时钟的为从设备(Slave),SPI 接口的读写操作,都是由主设备发起,SPI 只有主模式和从模式之分,没有读和写的说法,外设的读写操作是同步完成的,SPI 主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间

优点:

全双工串行

高速传输

灵活的数据传输单位,不限于 8 位,可以任意大小

简单的软件配置

简单的硬件结构,从站不需要唯一地址(与I2C不同),从机使用主机时钟,不需要精密时钟振荡器/晶振(与UART不同),不需要收发器(与CAN不同)

缺点:

通常仅支持一个主设备

没有硬件从机应答信号

没有定义硬件级别的错误检查协议

与RS-232和CAN总线相比,只能支持非常短的距离

需要更多的引脚(与I2C不同)

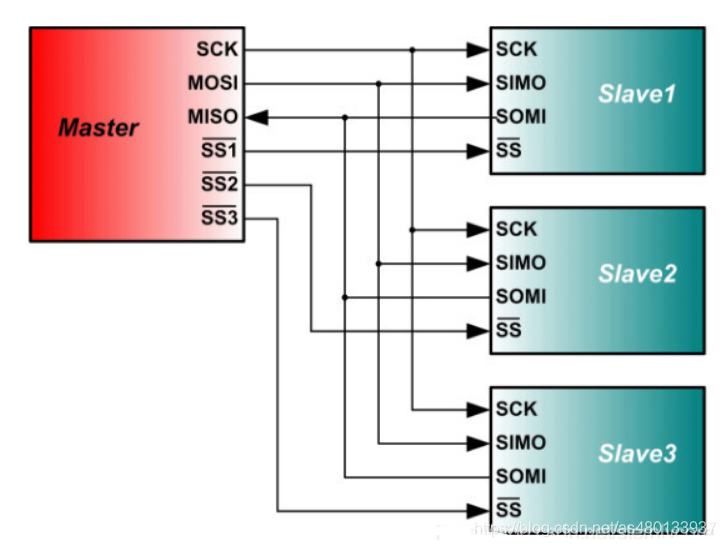

硬件上有 4 条线:SDI 数据输入线,SDO 数据输出线,SCK 时钟线,CS 片选线

芯片管脚占 4 个

MOSI 主设备输出/从设备输入引脚:该引脚在主模式下发数据,从模式下收数据

MISO 主设备输入/从设备输出引脚:该引脚在主模式下收数据,从模式下发数据

SCK 时钟引脚:由主设备产生 SCLK 串行时钟信号

SS 片选引脚:由主设备控制 CS/SS 从设备片选信号,选取指定从设备进行通讯(上横杠表示低电平有效)

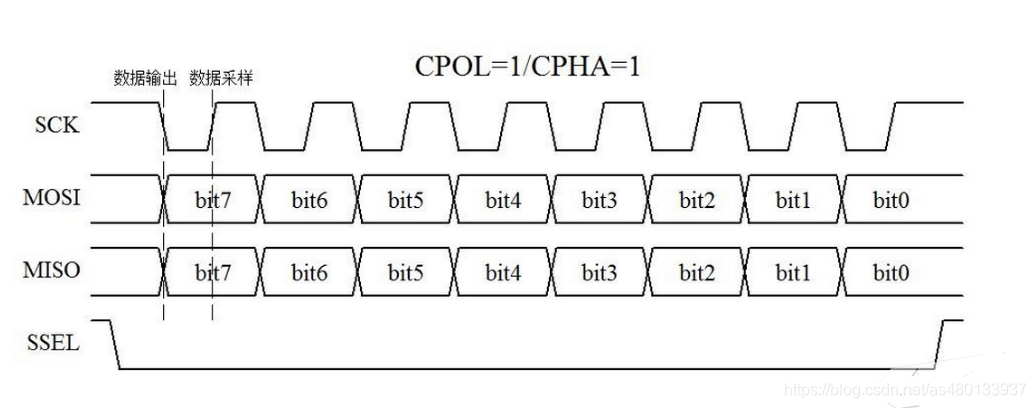

起始信号:主设备操控片选线电平由高变低,持续整个通讯过程,并开始在时钟线上发送工作脉冲

数据传输:在时钟线前个跳变沿期间,主机从机都 发/收 数据,在时钟线后个跳变沿期间,主机和从机都 收/发 数据

终止信号:主设备操控片选线电平由低变高

SPI 每个时钟周期收发 1 bit 数据,数据单位可以是 8 bit(1字节)或 16 bit(2字节)

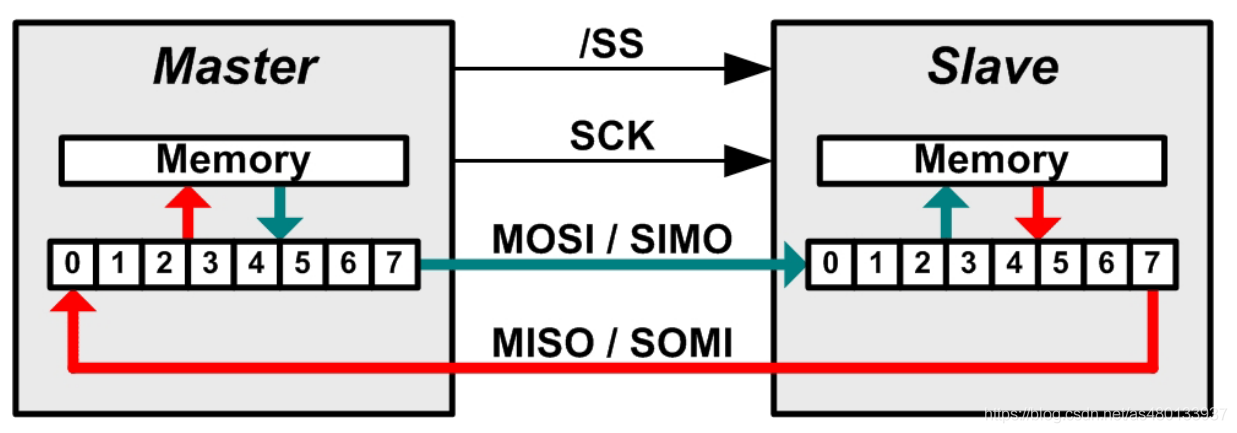

主设备和从设备都有一个串行的移位寄存器,主机(Master)将要发送的数据写入发送缓存区(Menory),缓存区将数据写入移位寄存器(0~7),移位寄存器通过MOSI接口一位一位的传给从机的移位寄存器,同时MISO接口接收到从机的数据并放入移位寄存器,再写入接收缓存区,从机也是如此。即要发一个数据必然会收到一个数据,而想收一个数据也必须要先发一个数据

SPI 的 4 种通讯模式

通过 CPOL(时钟极性)和 CPHA(时钟相位)确定通讯模式

CPOL(时钟极性):时钟空闲时的电平

CPOL = 0,SCK 时钟引脚在空闲时保持低电平

CPOL = 1,SCK 时钟引脚在空闲时保持高电平

CPHA(时钟相位):数据采集时机

CPHA = 0,在 SCLK 时钟信号的第一个跳变沿读,第二个跳变沿写

CPH

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1911

1911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?