基于FPGA的以太网TCP数据回环设计 vivado工程

ID:93500694384733842

jianfanzy

基于FPGA的以太网TCP数据回环设计Vivado工程

在现代通信领域,以太网TCP协议一直扮演着重要角色。为了提高网络性能和减少延迟,许多研究人员和工程师开始关注如何在硬件层面上实现以太网TCP数据回环。本文将介绍一种基于FPGA的以太网TCP数据回环设计,并详细阐述其在Vivado工程中的实现。

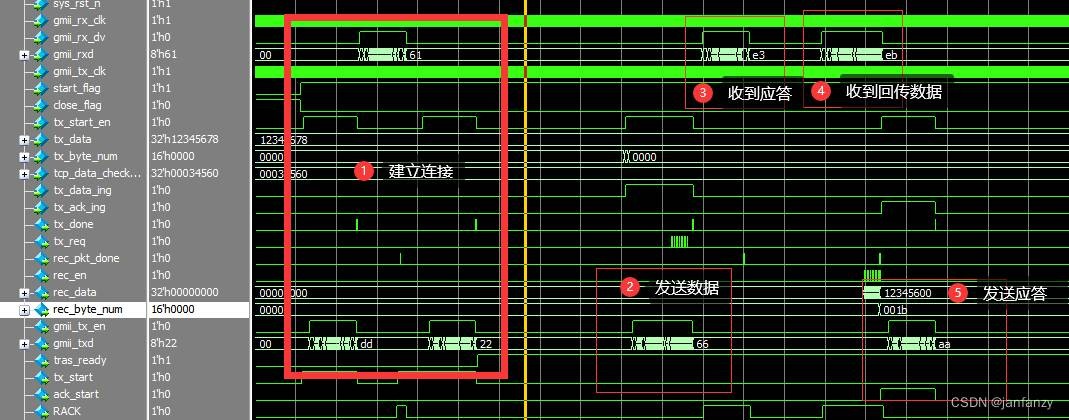

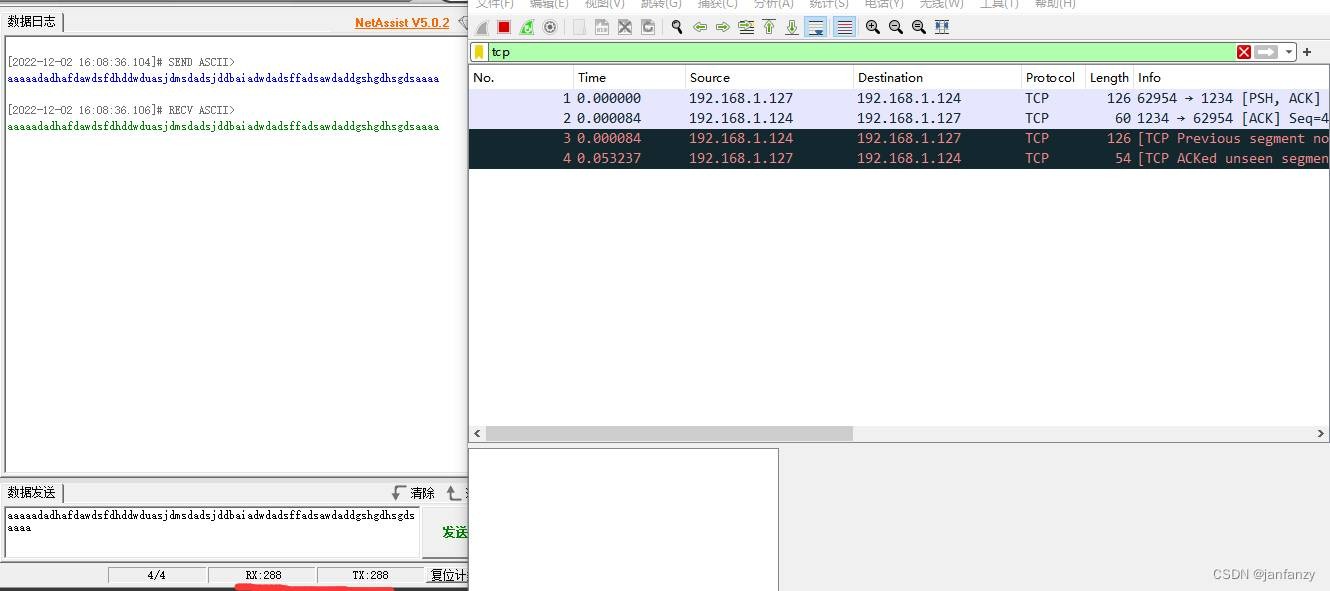

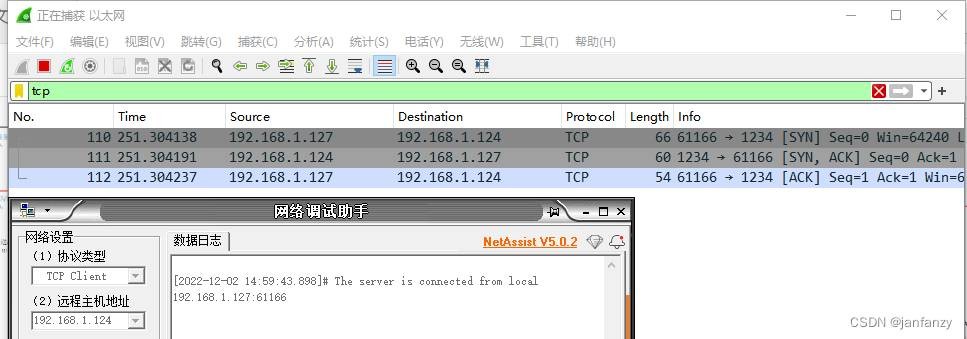

首先,我们需要了解以太网TCP数据回环的原理。以太网是一种常用的局域网通信协议,它使用以太帧作为数据传输的基本单位。而TCP协议则是一种可靠的传输协议,它提供了数据分段、流量控制、拥塞控制等功能。回环则意味着将发送的数据包重新接收回来,实现数据的循环测试。

在FPGA设计中,我们可以使用Vivado工具来实现以太网TCP数据回环。Vivado是Xilinx公司开发的一套集成设计环境,可以用于FPGA设计、仿真和综合。

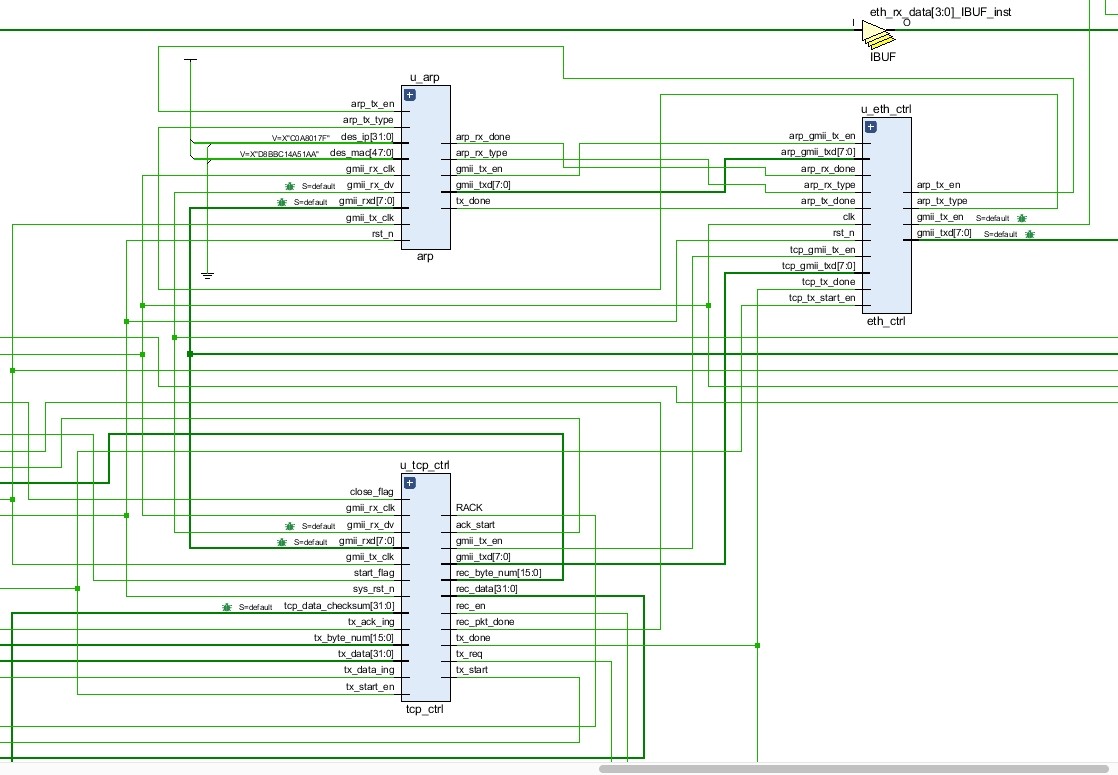

首先,我们需要创建一个Vivado工程,并添加相关IP核。IP核是一种预先设计好的模块,可以在FPGA设计中复用。为了实现以太网TCP数据回环,我们需要添加以太网IP核和TCP协议栈IP核。以太网IP核负责处理以太网数据帧的发送和接收,而TCP协议栈IP核负责实现TCP协议的各项功能。

接下来,我们需要对这些IP核进行配置。以太网IP核需要配置MAC地址、IP地址等参数,以确保数据正确传输。TCP协议栈IP核需要配置端口号、窗口大小等参数,以满足实际需求。

一旦IP核配置完成,我们可以开始设计数据回环逻辑。在设计中,我们需要将接收到的以太网数据帧送入TCP协议栈IP核进行解析和处理,然后再将处理后的数据帧发送回去。这样就实现了数据的循环反馈。

在Vivado工程中,我们可以使用Verilog或VHDL语言来描述这些逻辑。Verilog是一种硬件描述语言,它可以描述电路的结构和行为。VHDL则是一种硬件描述和仿真语言,它可以描述电路的结构、行为和时序。

设计完成后,我们可以使用Vivado工具进行逻辑综合、布局和时序优化。逻辑综合将Verilog或VHDL代码转化为逻辑门级网表,布局和时序优化将这些逻辑门放置在FPGA芯片的逻辑单元和时序电

【相关代码,程序地址】:http://fansik.cn/694384733842.html

945

945

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?