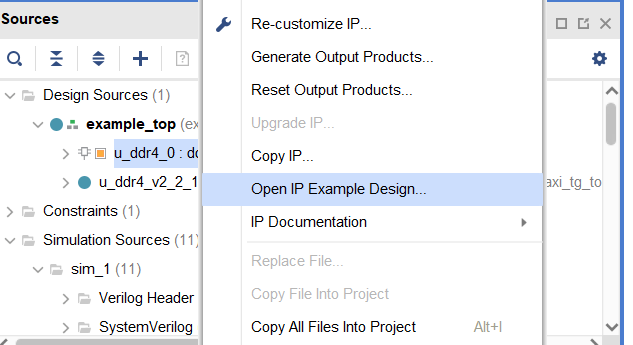

本次实验使用了AXI4接口协议,生成好IP核后右击Open IP Example Design,会自动根据用户配置的IP核生成对应的例程以及仿真文件。

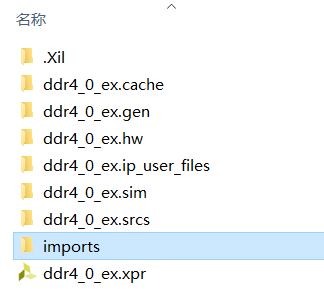

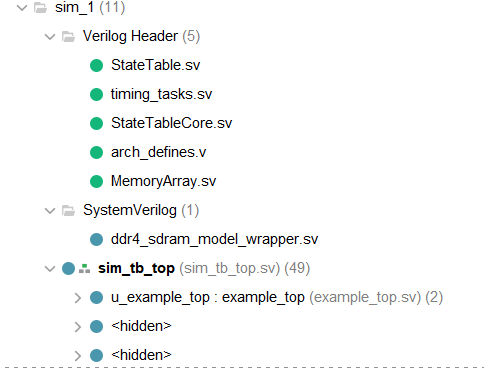

我们需要把例程中imports文件夹如图所示拷贝到工程中,里面的mem和txt文件可以删掉。还要把5个文件更改成Verilog Header,如图所示。文件夹里面的文件有些没有用,由于我仿真时报错,一直没找到原因,所以把里面的文件都添加到仿真工程中了。本次实验目的是DDR4成功初始化,细节后面再了解。

测试文件直接使用例程提供的就可以,把例化的可综合top替换成自己的,再修改时钟、例化的引脚等几处细节就可以开始仿真了。

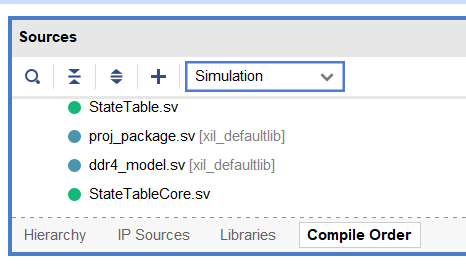

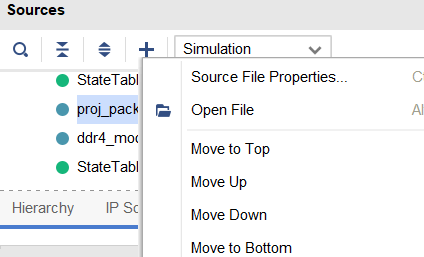

仿真时报错,查看xvlog.log文件说是线型没有定义,报错的都是Verilog Header文件。后面查找资料,是因为compile order的顺序问题。工程的compile order文件顺序如图所示,对比生成的例程,右击文件Move to Top,移动一下顺序(不知道为什么Verilog Header文件一直移不了顶层,可能因为它是Verilog Header文件,所以只把Verilog Header之间的顺序跟尽量和例程一致),然后仿真top文件.sv文件放在Verilog Heade后面。

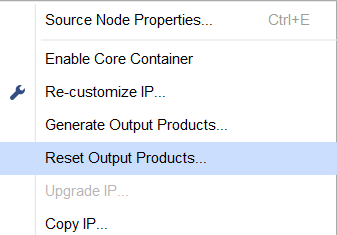

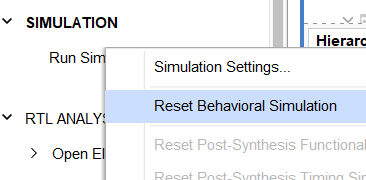

Ps:后面又报错,IP核、仿真都reset了,还是不行,就胡乱移,后面找不到原因就关机了,第二天开机再点仿真不知道为什么就可以了。如果一直仿真不成功,可以右击IP核,reset一下,同时仿真也reset一下,然后再试试,还可以重启一下试试。DDR3仿真时只需要加Verilog Header 和一个.v文件,DDR4复杂了许多,不过初始化速度快了,点击仿真就初始化好了。

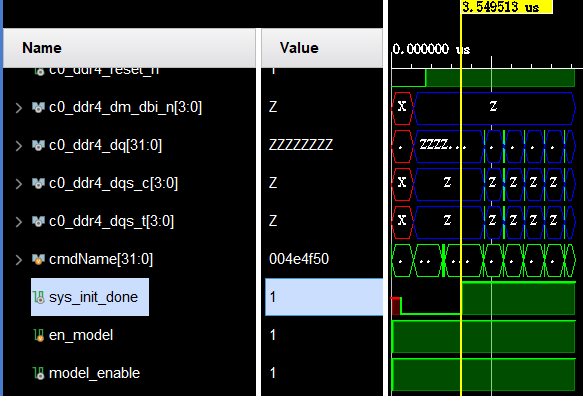

3.5us就初始化完成了

(本文档用于学习交流,欢迎指正)

3324

3324

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?