本节目录

一、DDR4 MIG的时钟框架

二、DDR4 MIG的时钟频率计算

三、DDR4 MIG的IP中时钟设置

四、往期文章链接

本节内容

一、DDR4 MIG的时钟框架

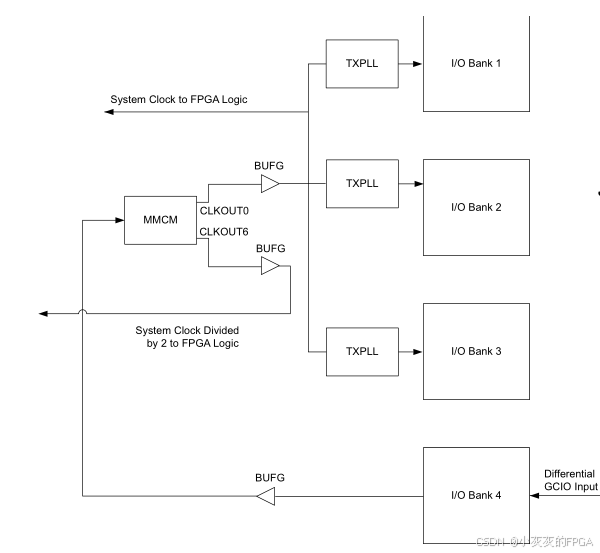

DDR4控制器中,包括一个MMCM和两个bufg,并且每个I/O Bank需要配置一个TXPLL。

Differential GCIO的输入时钟,差分转单端后,再通过BUFG输入到MMCM4_ADV原语中。经过MMCM的两路时钟输出,一路用于TXPLL和用户侧的时钟(300M),另一路生成2分频的时钟(150M)。

二、DDR4 MIG的时钟频率计算

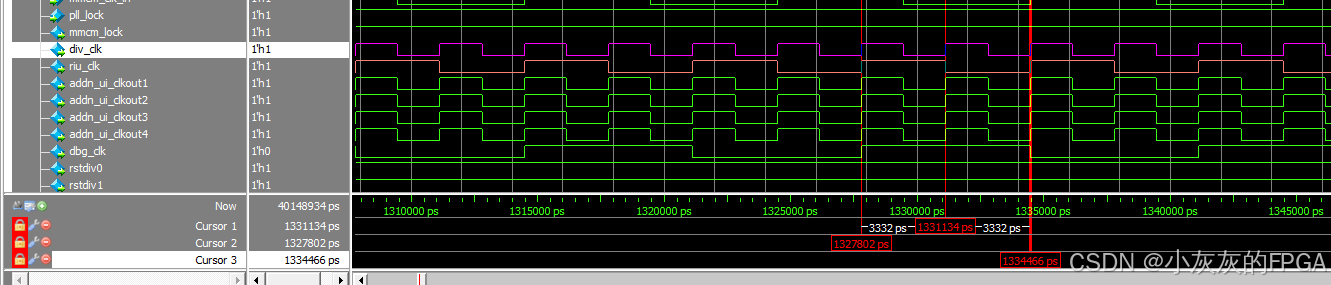

从代码底层来看,ddr4_phy_v2_2_0_pll和ddr4_v2_2_17_infrastructure这两个模块实现了DDR4控制的所有时钟的产生,下面的仿真中表示的div_clk表示CLKOUT0,riu_clk表示CLKOUT6。

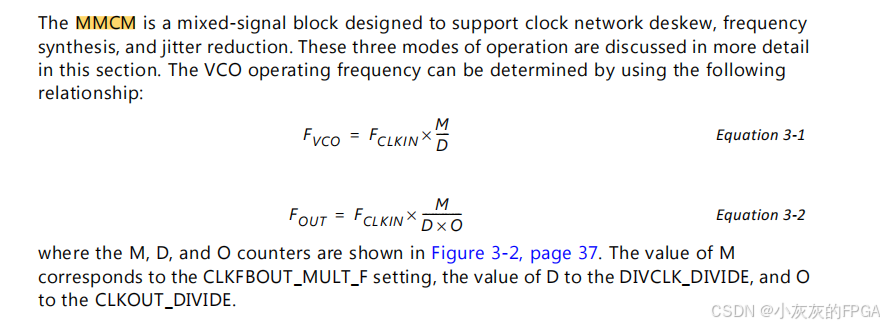

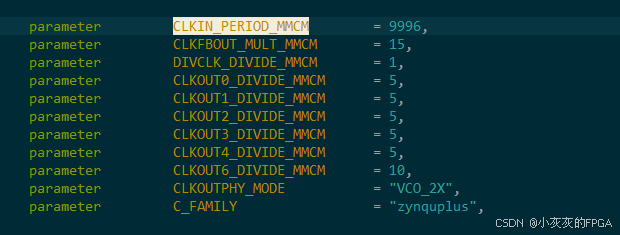

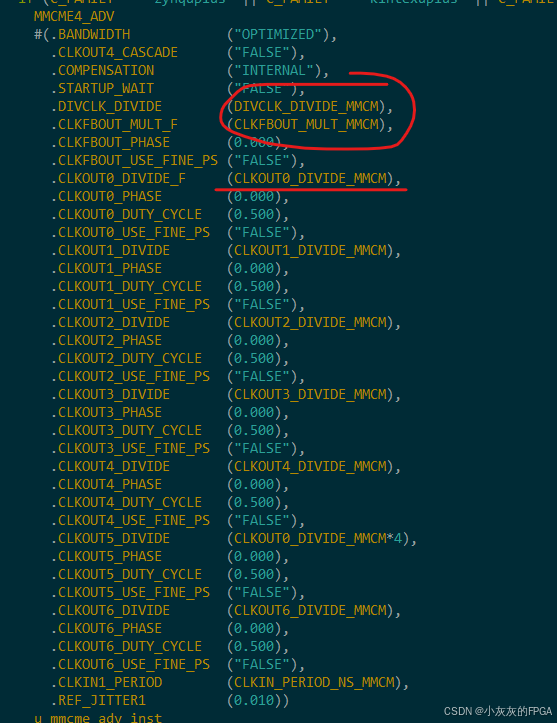

ddr4_v2_2_17_infrastructure模块中包含了一个MMCM4_ADV,将输入的100M的时钟,通过倍频分频从而产生所需要的时钟,计算公式如下:

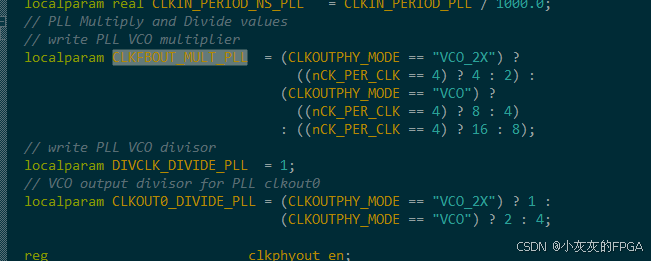

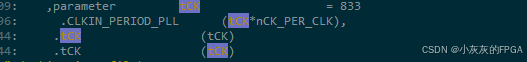

对应原语中的数值一一对应进行计算,以CLKOUT0为标准来计算,CLKIN_PERIOD_NS_MMCM数值表示的是输入时钟的周期,单位NS,9996ps,这个是通过DDR4的IP的用户界面设置的,也就是100M的差分时钟输入,外部硬件需要提供100M的差分时钟。M数值,也就是CLKFBOUT_MULT_MMCM的数值为15。D数值,也就是DIVCLK_DIVIDE_MMCM的数值为5。O数值,也就是CLKOUT0_DIVIDE_MMCM的数值为5。那么计算出CLKOUT0的频率为10015/(51)=300M。这个适用于MMCM的原语,FPGA开发者可以自己去计算验证下,后期可以直接调用原语进行例化。

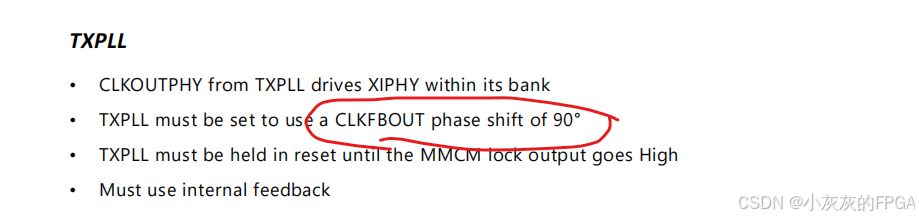

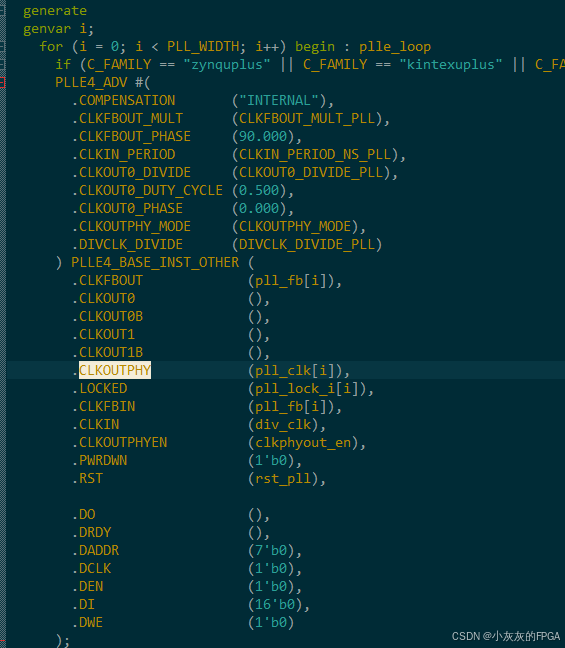

TXPLL中进行计算pll_clk的数值, CLKOUTPHY_MODE为"VCO_2X",表示输出时钟频率为VCO频率的2倍。VCO的计算公式,输入时钟频率CLKFBOUT_MULT_PLL/DIVCLK_DIVIDE_PLL=300M4=1200M,PHY芯片时钟双边沿采样,故DDR4的运行频率为2400MHz。对于TXPLL的输出PHY时钟,还需要有90°的相位调整。

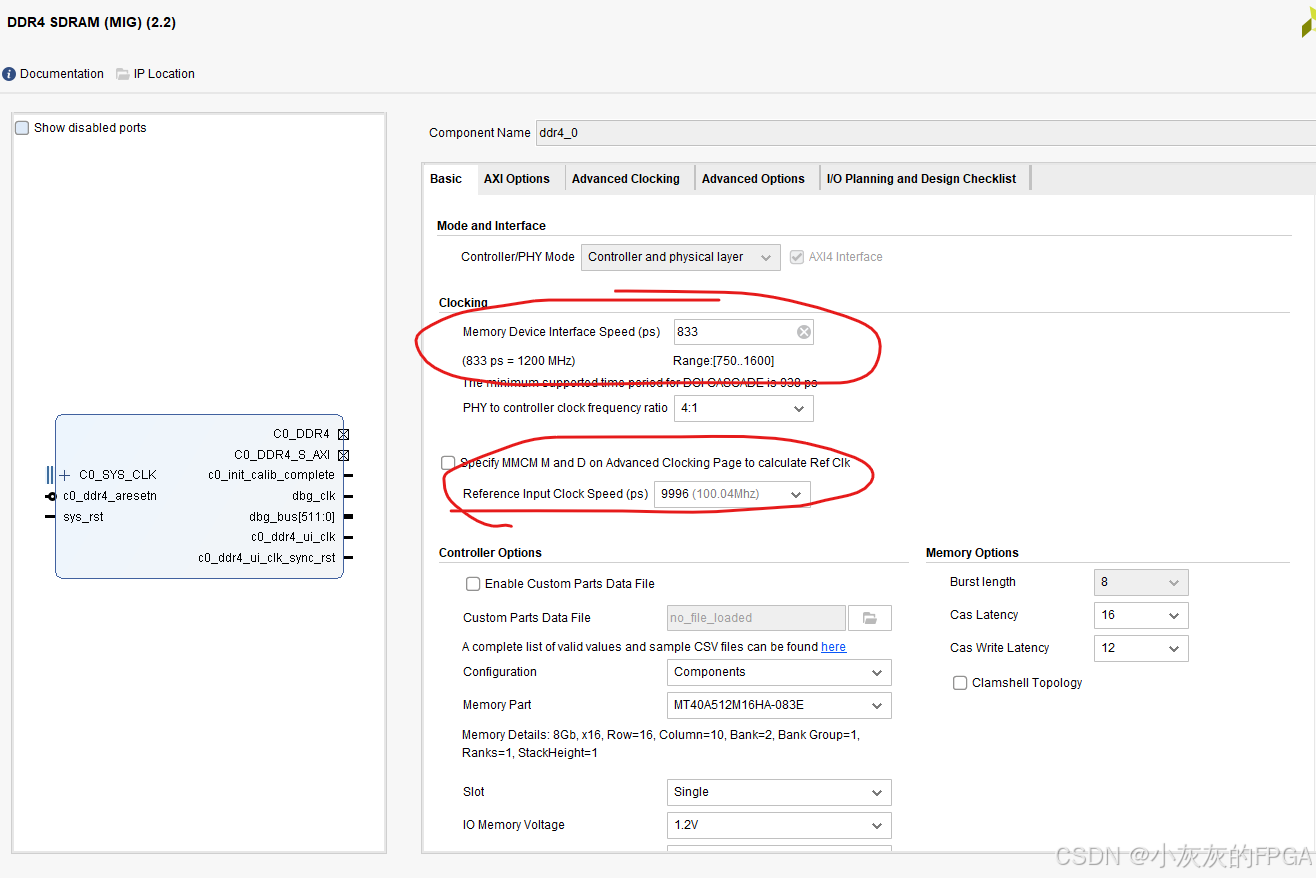

三、DDR4 MIG的IP中时钟设置

DDR4 MIG的IP中关于时钟的设置有四处,一是tck,也就是833ps,1200M,输入给TXPLL的时钟为300M,也就是1200M/4=300M;二是输入参考时钟频率选择,9996ps,100M;三是输入差分或者No buffer;四是用户侧时钟的生成,与100M输入差分是同源的,支持自定义输出指定的时钟频率。

四、往期文章链接

UltraScale+FPGA中Serdes的多lane对齐异常解决方案

vivado时序报告中slack是如何计算的?如何优化时序?

UltraScale+FPGA中GTY的TX路径时钟详解——以40G的ETH MAC IP为例

vivado时序优化——约束异步时钟组set_clock_groups

基于FDMA和AXI4接口的DDR4遍历读写测试

基于fpga的图像处理之3x3_5x5算子模板设计

基于fpga的图像处理之3x3_5x5算子模板中值排序

基于fpga的图像处理之图像灰度化处理(Vivado+Modelsim+Matlab联合仿真验证)

AXI协议之AXILite开发设计(一)

AXI协议之AXILite开发设计(二)

AXI协议之AXILite开发设计(三)

AXI协议之AXILite开发设计(四)

AXI协议之AXILite开发设计(五)

FPGA和Matlab的FFT功能验证(一)

FPGA和Matlab的FFT功能验证(二)

FPGA和Matlab的FFT功能验证(三)

跟小灰灰一起学vivado:7系列FPGA的MultiBoot和Fallback功能更新固件

跟小灰灰一起学vivado:7系列FPGA配置模式之配置数据文件格式和配置时序步骤

跟小灰灰一起学vivado:7系列FPGA配置模式之主SPI四路(x4)

跟小灰灰一起学vivado:PCIe XDMA实现远程更新FPGA固件

Xilinx UltraScale+DDR4项目开发(一)——DDR4 MIG的ip接口信号

Xilinx UltraScale+DDR4项目开发(二)——DDR4 MIG的时钟网络

Xilinx UltraScale+DDR4项目开发(三)——DDR4器件选型与MIG IP的配置

低速接口项目之串口Uart开发(一)——串口UART

低速接口项目之串口Uart开发(二)——FIFO实现串口数据的收发回环测试

低速接口项目之串口Uart开发(三)——串口发送模块和接收模块

低速接口项目之串口Uart开发(四)——UART串口实现FPGA内部AXILITE寄存器的读写控制

低速接口项目之串口Uart开发(五)——QT实现Uart串口寄存器读写工具

低速接口项目之串口Uart开发(六)——zynq系列ps-pl端uart实现共享Axilite内部寄存器的读写

低速接口项目之串口Uart开发(七)——如何在FPGA项目中实现自适应波特率串口功能

低速接口项目之串口Uart开发(八)——如何通过ps侧的串口实现zynq的在线升级(一)

低速接口项目之串口Uart开发(九)——如何通过ps侧的串口实现zynq的在线升级(二)

低速接口项目之串口Uart开发(十)——基于EMIO的自定义PL串口实现zynq的在线升级

302

302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?