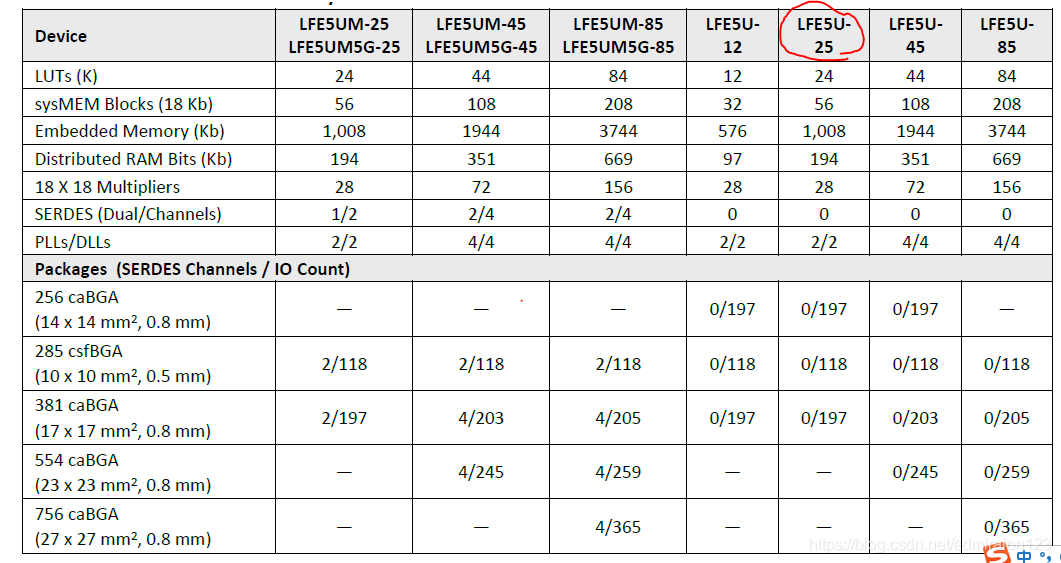

在这里记录一下,也是对学习的一个简单总结吧,也方便自己以后查询。项目中用到的是Lattice LFE5U-25F-6BG381C这款芯片,该芯片采用40nm工艺,相比以前有更多的dsp,性价比高。先看看这块芯片的资源吧,如下图所示。有197个PIO口,2个锁相环PLL,56个ebr(每个ebr18kb,相当于1个18x1024的dpram)或者1008kb嵌入式内存,28个18x18乘法器,24k的lut。

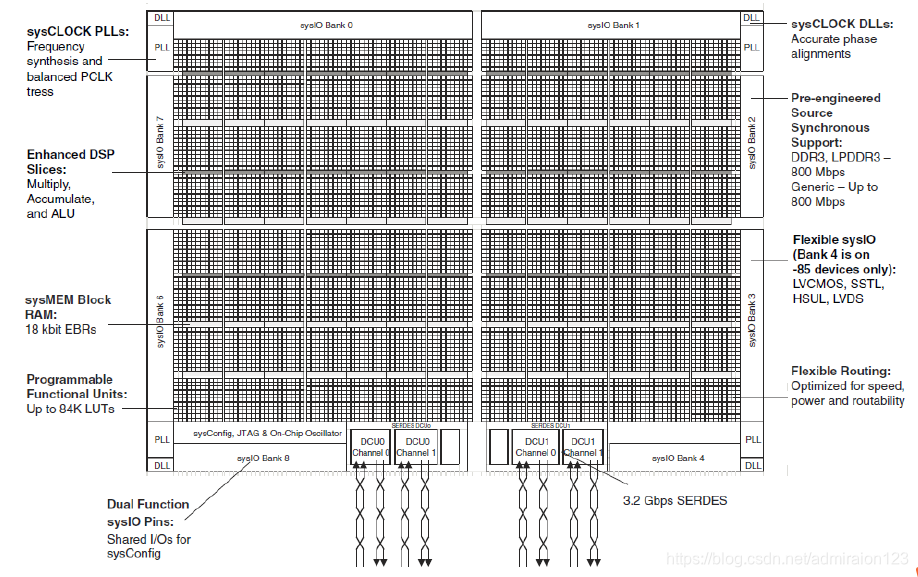

接下来,我们来看看该芯片的平面图。

先来讲讲PFU(programmable functional unit)单元,lattice里这个是基本功能单元,由4片slice组成,一片slice又是由2个lut4&carry chain(进位链,用于加快算术运算)、2个触发器以及一些其他控制逻辑(用于复位、使能、扩展等)。slice可配置为4种运行模式:1,logic模式,即用于正常的逻辑;2,ripple模式,主要用于低位数运算时加快速度;3,ram模式,该模式使用lut搭建distributed ram,一个16x4的单口ram需要一个pfu,slice0和slice1构成ram,slcie2用于地址和控制信号;4,rom模式。

接下来讲讲时钟。ECP5-25时钟网络分为主时钟网络PCLK和边沿时钟网络ECLK,主时钟网络具有低时钟偏移、高扇出特点,通过一个叫center mux的模块分部到各fpga构造中;边沿时钟网络主要是用于高速I/O接口用,如用于ddr memory、generic ddr等,值得注意的是要上边沿时钟网络,需要ECLKSYNC模块或者ECLKBRIDGE。ECP5-25有两个PLL,位于bottom 左和右;每个PLL有4个输出,clkop、clkos、clkos2、clkos3,每个输出都可以route到主时钟网络,但是只有clkop和clkos可以route到eclk;每个PLL输入源有4个,专用pll引脚、pclk的route、eclk的route、fpga fabric,外部时钟引入作为主时钟强烈推荐使用专用pll引脚,ecp5-25中为<LOC>_GPLL0T_IN,网口的输入时钟一般选用带有pclk属性的时钟,ecp5-25PCLKT<Bank>_<0/1>。在我的设计中,涉及的时钟,晶振输入、网口时钟输入与输出、sdram时钟。

接下来讲讲EBR。ebr内容较多,SPR、True-Dual Port RAM、Pseudo Dual-Port RAM、ROM、FIFO,这里主要讲ram(单口和真双口ram)的三种模式:a,normal模式,写就是写,只有当读信号来到时,输出端口数据才会变;b,writethrough模式,写的数据会在下一拍或两拍(取决于是否有输出寄存)自动输出;c,readbeforewrite模式,写地址中的原始数据会在下一拍或者两拍后自动输出。另外,仿真中经常需要初始化memory,可以用<file_name>.mem文件来配置,该文件有bit、hex和addressed hex三种形式,addressed hex用来初始化memory中特定地址的内容,未初始化的部分默认为0。

DSP没怎么看过,对其原理也了解很少。只是项目中代码优化的时候,用到了syn_mulstyle这个原语,解决乘法器不够的问题。当然,对于实时性不高的输出,时分复用也是常用的优化手段。另外,乘法器延时与配置有关,输入寄存、输出寄存、pipeline。

接下来讲讲PIC,PIC由4个PIO构成,而1个PIO又是由输入寄存模块、输出寄存模块、三态模块构成。位于FPGA左右两边的PIO的输入寄存模块具有内嵌fifo,专门为ddr memory设计,可将ddr时钟域转到eclk时钟域。ECP5-25中,位于左右两边的PIO,每16个PIO构成一个DQS组,一个DQS组中有两个引脚已提前配置,用于DQS和DQS#信号,其余引脚可用于DQ、DM信号;DQSBUF模块则是专门用于调整DQS信号相位;左右两边的PIO也可以组成信号对,用于传输差分信号。PIO的直接与sysIObuffer相连,bank4的I/O是没有sysIObuffer的,bank8的I/O与系统配置口复用,bank的I/O参考电压都可以单独配置。

接下来讲讲serdes,serdes主要作用就是将并行数据转换成串行数据,加快数据传输速率。ecp5-25没有serdes。lattice ecp5系列芯片serdes是按dual存在的,ecp5um-45有两个dual,每个dual包含两个通道的serdes,每个通道都是全双工的,一组收,一组发。原则上,只要参考时钟兼容,那么一个dual里可以支持两种协议。diamond提供pcs ip核,用于连接serdes和fpga core。在之前的一个项目中,用到了ecp3-150,其中光纤数据传递时用到了serdes。ecp3-150有4 quads的serdes,每quad包含4通道全双工serdes,项目中,用2 quads用于接收主板传过来的数据,这种用途的pcs配置成全接收,协议为G8B10B。每通道serdes最大传输速率为3.2G,我们设为2.5G,4个通道总共10G,由于8b10b编码,实际传输为8G,这样1 quad正好带8个 1G网口数据(3.125G下可带10G);参考时钟选为内部,用125M的系统时钟,倍率为20x;数据位宽设置为16;采用full模式接收;在lpf文件里使用LOCATE COMP "pcs_inst_name" SITE "PCSx"可将pcs约束在相应的quad上;lsm(link state machine)用于表示链接同步,规定comma符之间必须包含奇数个数据,否则认为链接错误,4个连续的错误会造成lsm失锁,lsm_status_ch[3:0]_s拉低;rx_los_low_ch[3:0]_s表示信号丢失,高有效;rx_cdr_lol_ch[3:0]_s表示恢复时钟信号丢失,高有效。项目中,剩余2 quads用于收发光纤收发器数据,这种用途的pcs配置成收发模式,协议为xaui。前面主板传过来的数据经过数据解包、对齐、跨时钟域(pcs接收时钟到系统时钟)等处理解析出网口数据,然后再打包成xaui需要的数据格式(系统时钟到pcs发送时钟,64bit),经过xaui IP发送给pcs IP,完成发送;收光纤收发器数据过程类似,只是pcs到xaui时需要先将4个通道的接收时钟都转换为第1个通道的时钟,同时xaui IP出来的数据也需要进过调整后才能进行解包。每通道传输速率设为3.125G,参考时钟选用外部156.25M晶振;数据位宽为16。

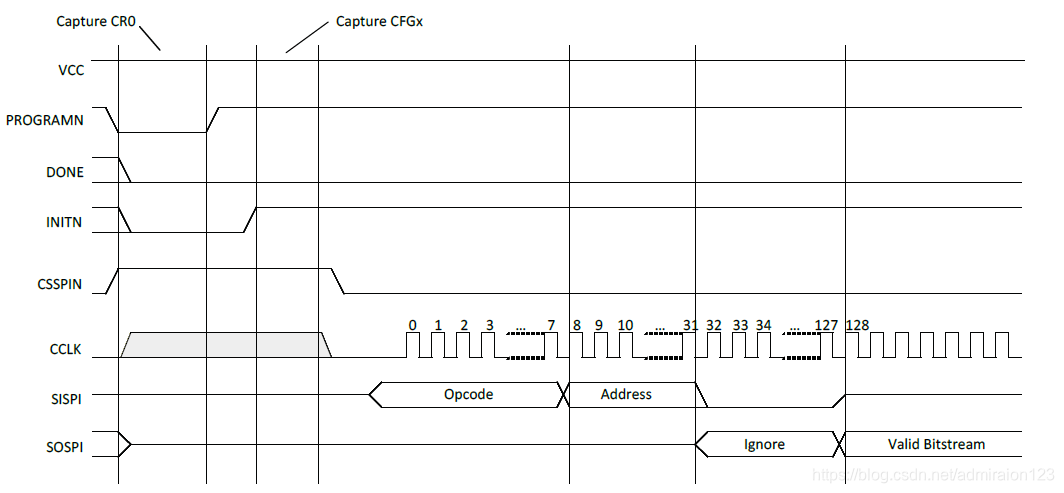

最后讲讲FPGA配置吧。ecp5-25有两种配置方式,一种是通过TAP(test access port),一种是通过sysConfig口。FPGA是基于sram结构的,其上电配置文件需要存储在外部flash,配置文件大小与使用逻辑资源以及初始化ebr个数有关。项目中用到的是sysConfig口配置,采用MSPI模式,即CFGMDN为“010”。需要注意的是上电配置完成过后,MSPI模式下的sysConfig口都会变为高阻态,这时miso、mosi、csspin都可以用作I/O口,但是MCLK必须要经过不行,且MCLK用作时钟口时必须经过USRMCLK原语调用,而后才能继续读写slave flash。lattice芯片上电配置的流程大体如下:上电,检测电源是否稳定(具体指标可参考芯片的ac参数,主要是Vcc、Vccio8、Vccaux)。当电源条件满足要求时,POR(power on reset)电路会释放rest strobe,done、initn信号被拉低,进入初始化状态,清除之前配置的sram。当初始化完成(1,program信号被拉高;2,initn信号被拉高(初始化出问题则会被拉低);3,tINITL初始化时间到;三个条件同时满足)则进入配置阶段,配置阶段有问题,initn信号也会被拉低。配置完成,则进入唤醒状态:1,global output enable信号拉高,I/O口退出高组态,2,global set/reset信号被释放;3,global write disable信号被拉低,ram可以被操作; 4,done信号被拉高,配置完成,进入用户模式。对于双启动模式,如果加载数据超时或者crc校验错误,设备就会进入golden取加载。Diamond Deployment Tool工具用于生成双启动或者多启动文件。

1017

1017

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?