实验二

1. 2-4译码器

top.v

module decode24(x,en,y);

input [1:0] x;

input en;

output reg [3:0]y;

always @(x or en)

if (en)

begin

case (x)

2'd0 : y = 4'b0001;

2'd1 : y = 4'b0010;

2'd2 : y = 4'b0100;

2'd3 : y = 4'b1000;

endcase

end

else y = 4'b0000;

endmodule

sim_main.cpp

int main() {

sim_init();

top->en = 0b0; top->x = 0b00; step_and_dump_wave();

top->x = 0b01; step_and_dump_wave();

top->x = 0b10; step_and_dump_wave();

top->x = 0b11; step_and_dump_wave();

top->en = 0b1; top->x = 0b00; step_and_dump_wave();

top->x = 0b01; step_and_dump_wave();

top->x = 0b10; step_and_dump_wave();

top->x = 0b11; step_and_dump_wave();

sim_exit();

}

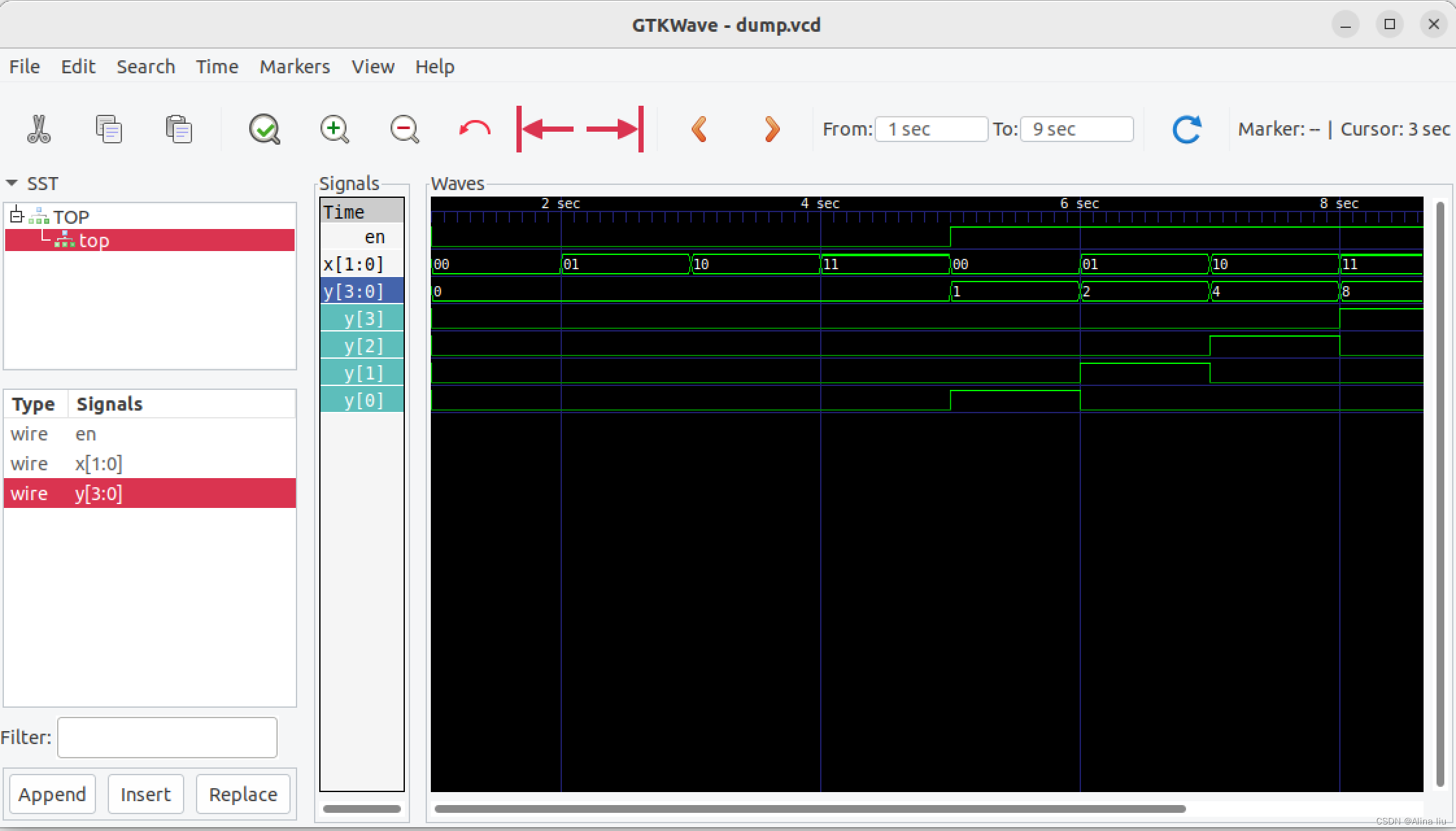

仿真结果

2. 4-2编码器

top.v

module encode42(x,en,y);

input [3:0] x;

input en;

output reg [1:0]y;

always @(x or en) begin

if (en) begin

case (x)

4'b0001 : y = 2'b00;

4'b0010 : y = 2'b01;

4'b0100 : y = 2'b10;

4'b1000 : y = 2'b11;

default: y = 2'b00;

endcase

end

else y = 2'b00;

end

endmodule

sim_main.cpp

int main() {

sim_init();

top->en=0b0; top->x =0b0000; step_and_dump_wave();

top->x =0b0001; step_and_dump_wave();

top->x =0b0010; step_and_dump_wave();

top->x =0b0100; step_and_dump_wave();

top->x =0b1000; step_and_dump_wave();

top->en=0b1; top->x =0b0000; step_and_dump_wave();

top->x =0b0001; step_and_dump_wave();

top->x =0b0010; step_and_dump_wave();

top->x =0b0100; step_and_dump_wave();

top->x =0b1000; step_and_dump_wave();

sim_exit();

}

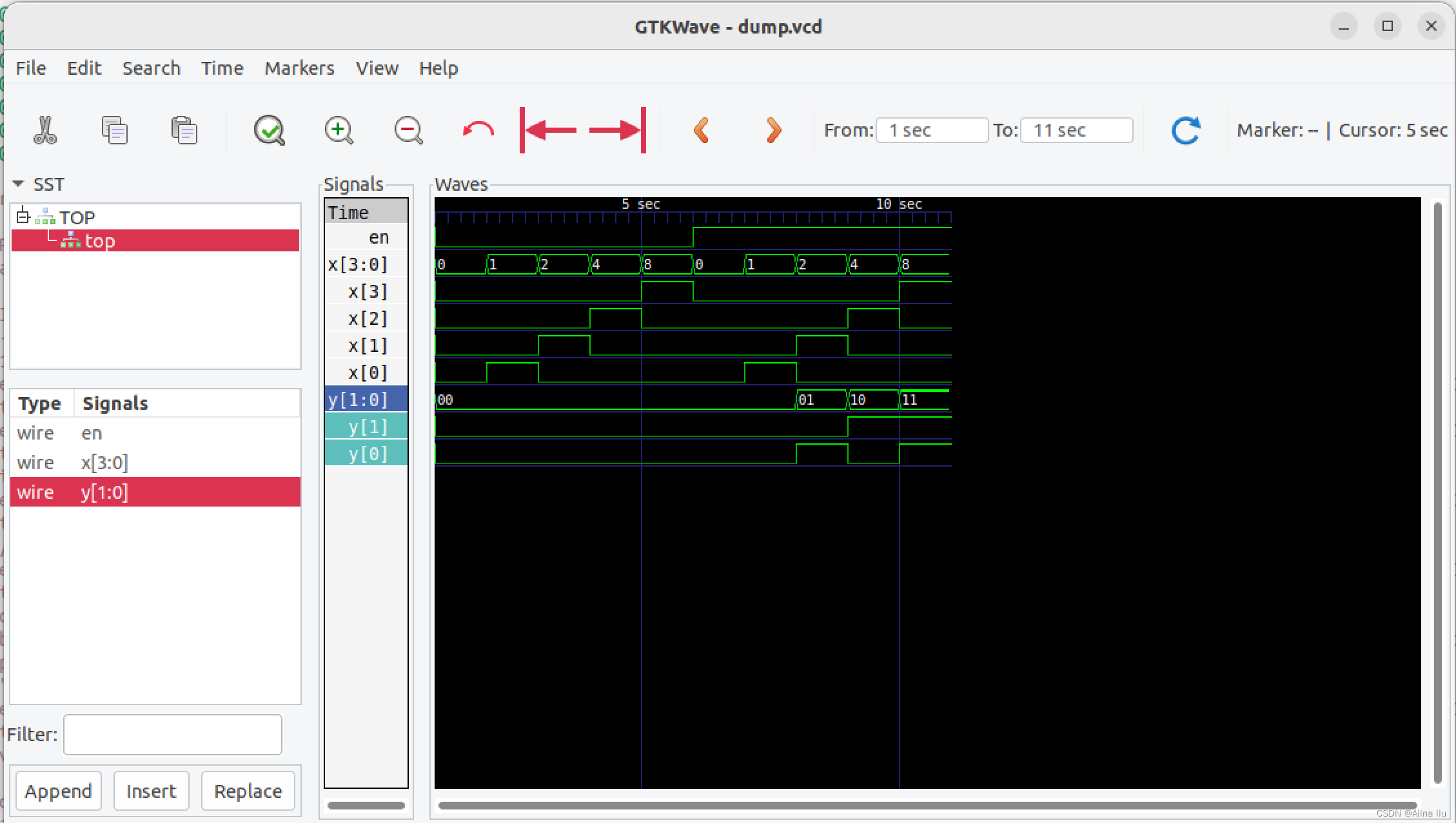

仿真结果

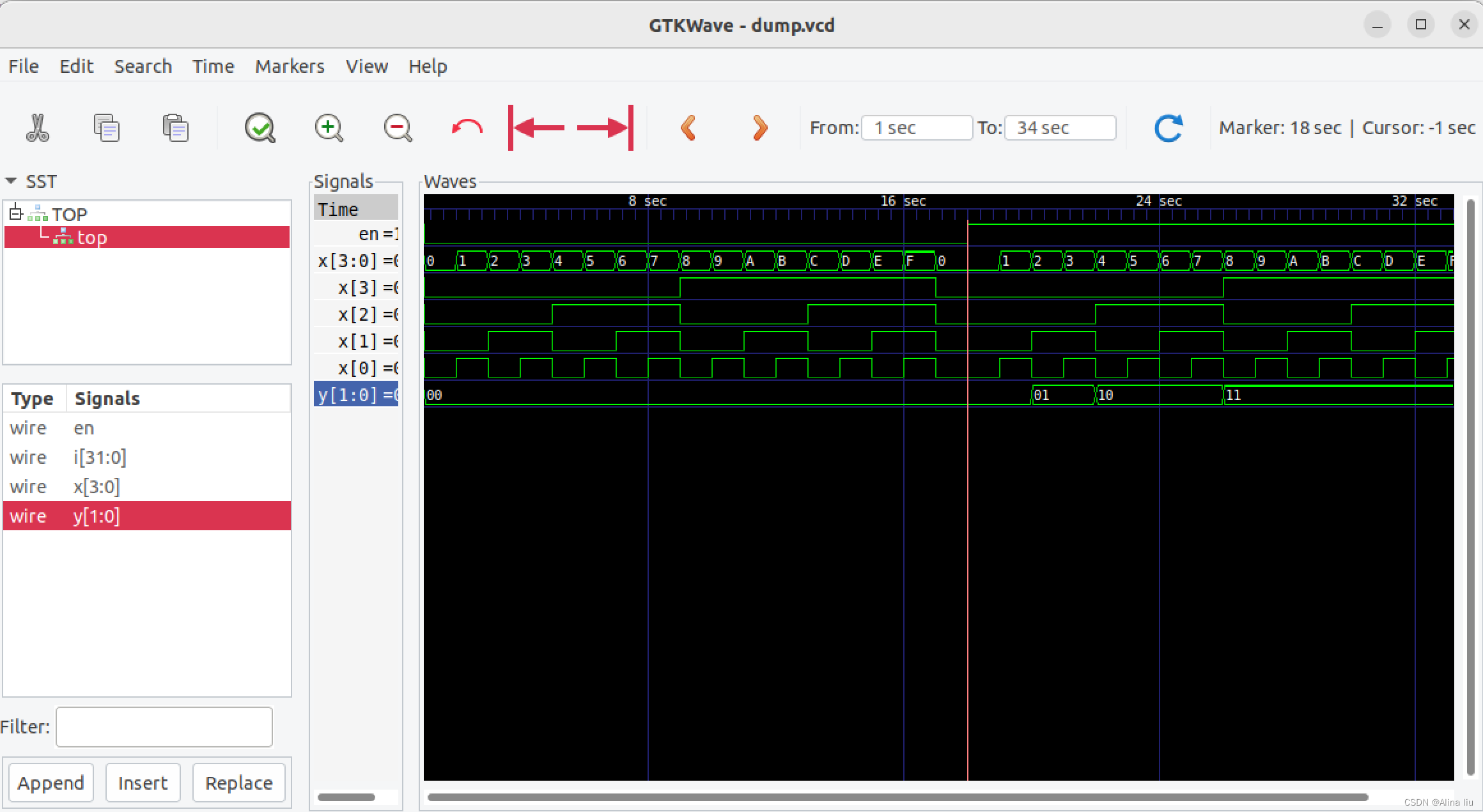

3. 优先编码器

3. 优先编码器

top.v

module encode42(x,en,y);

input [3:0] x;

input en;

output reg [1:0]y;

integer i;

always @(x or en) begin

if (en) begin

y = 0;

for( i = 0; i <= 3; i = i+1)

if(x[i] == 1) y = i[1:0];

end

else y = 0;

end

endmodule

sim_main.cpp

int main(){

sim_init();

int i;

top->en = 0;

top->x = 0b0000;

for(i=0;i<=15;i++){

step_and_dump_wave();

top->x = top->x+1;

}

step_and_dump_wave();

top->en = 1;

top->x = 0;

for(i=0;i<=15;i++){

step_and_dump_wave();

top->x = top->x+1;

}

sim_exit();

}

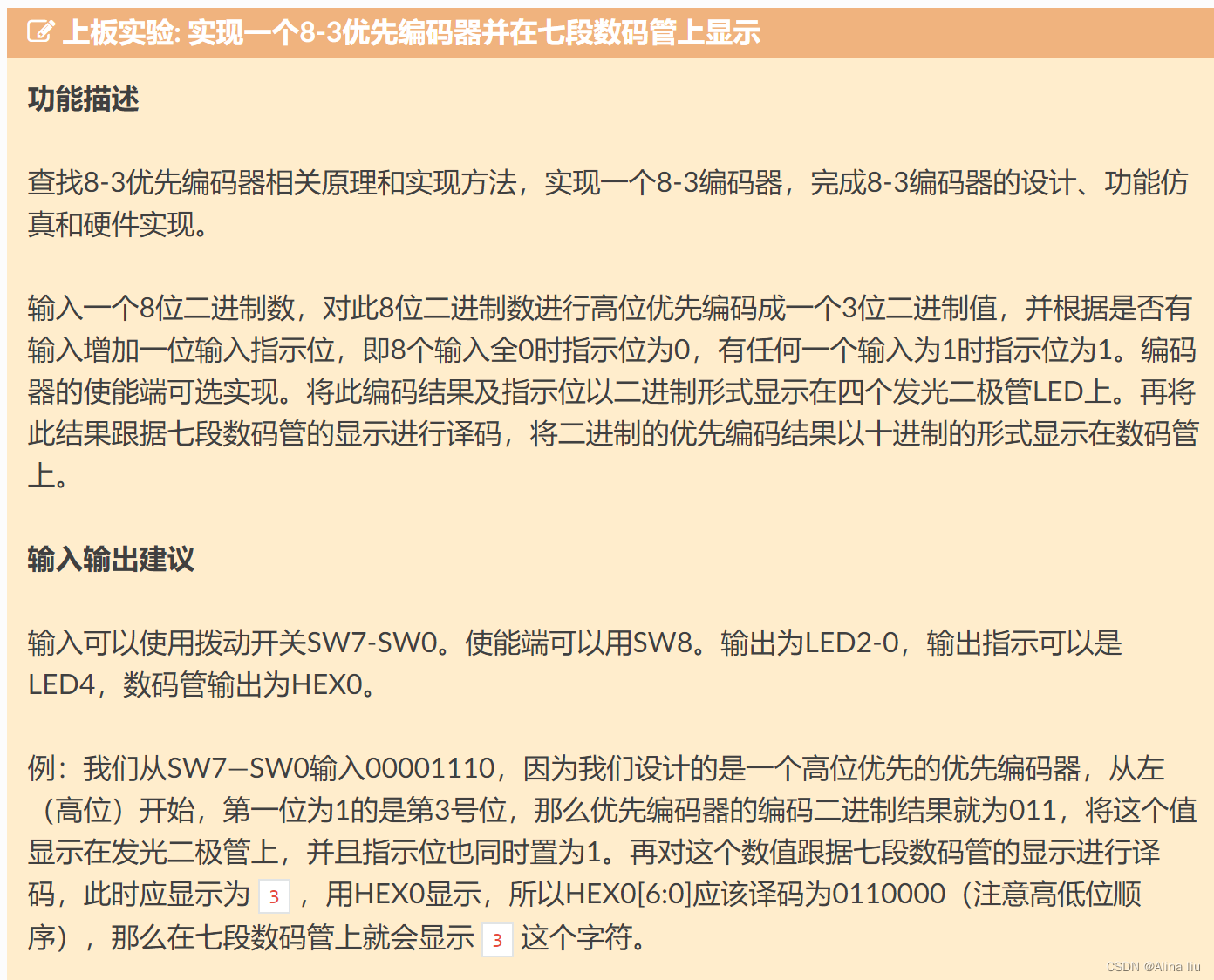

4. 8-3优先编码器

top.v

module top (x,y,en,lb,seg0);

input [7:0] x;

input en;

output reg lb;

output reg [6:0] seg0;

output reg [2:0] y;

always@(*)

begin

if(en)

begin

lb = 1;

casez(x) //此处用casex会warning,因为casex不可综合

8'b0000_0000: begin y = 3'b000;lb = 0; end

8'b0000_0001: y = 3'b000;

8'b0000_001?: y = 3'b001;

8'b0000_01??: y = 3'b010;

8'b0000_1???: y = 3'b011;

8'b0001_????: y = 3'b100;

8'b001?_????: y = 3'b101;

8'b01??_????: y = 3'b110;

8'b1???_????: y = 3'b111;

default: y = 3'b000;

endcase

end

else y = 0;

end

bcd7seg sg0({1'b0,y},seg0);

endmodule

bcd7seg.v

module bcd7seg(

input [3:0] b,

output reg [6:0] h

);

always@(*)

begin

case(b)

4'b0000: h=7'b0000_001;

4'b0001: h=7'b1001_111;

4'b0010: h=7'b0010_010;

4'b0011: h=7'b0000_110;

4'b0100: h=7'b0110_011;

4'b0101: h=7'b0100_100;

4'b0110: h=7'b0100_000;

4'b0111: h=7'b0001_111;

4'b1000: h=7'b0000_000;

4'b1001: h=7'b0000_100;

4'b1010: h=7'b0001_000;

4'b1011: h=7'b1100_000;

4'b1100: h=7'b0110_001;

4'b1101: h=7'b1000_010;

4'b1110: h=7'b0110_000;

4'b1111: h=7'b0111_000;

endcase

end

endmodule

sim_main.cpp

#include <verilated.h>

#include "Vtop.h"

#include <nvboard.h>

static TOP_NAME dut;

void nvboard_bind_all_pins(Vtop* top);

void single_cycle(){

dut.eval();

}

int main(){

nvboard_bind_all_pins(&dut);

nvboard_init();

while(1){

single_cycle();

nvboard_update();

}

}

nvboard约束文件 top.nxdc

top = top

y(LD2,LD1,LD0)

x(SW7,SW6,SW5,SW4,SW3,SW2,SW1,SW0)

en(SW8)

seg0(SEG0A,SEG0B,SEG0C,SEG0D,SEG0E,SEG0F,SEG0G)

lb(LD4)

Makefile文件

TOPNAME = top

NXDC_FILES = constr/top.nxdc #约束文件路径

INC_PATH ?= #?=的意义是,INC_PATH如果被未被定义,则为?=后的值,如果被定义过,则保持原来的值

VERILATOR = verilator

VERILATOR_CFLAGS += -MMD --build --cc -O3 \

--x-assgin fast --x-initial fast --noassert --trace

BUILD_DIR = ./build

OBJ_DIR = $(BUILD_DIR)/obj_dir

#OBJ_DIR = ./build/obj_dir

BIN = $(BUILD_DIR)/$(TOPNAME)

#BIN = ./build/top

default: $(BIN) #终极目标为default,依赖./build/top

$(shell mkdir -p $(BUILD_DIR)) #建立./build目录

SRC_AUTO_BIND = $(abspath $(BUILD_DIR)/auto_bind.cpp) #abspath:返回文件的绝对路径

#SRC_AUTO_BIND = ~/vtest/ex2/part4/build/auto_bind.cpp 此为约束文件

$(SRC_AUTO_BIND): $(NXDC_FILES) # 目标文件(约束文件SRC_AUTO_BIND)的建立依赖于constr/top.nxdc

python3 $(NVBOARD_HOME)/scripts/auto_pin_bind.py $^ $@

# python3 $(NVBOARD_HOME)/scripts/auto_pin_bind.py constr/top.nxdc auto_bin.cpp

#此命令用来生成auto_bin.cpp文件

VSRCS = $(shell find $(abspath ./vsrc) -name "*.v")

#在~/vtest/ex2/part4/vsrc目录中寻找所有的.v文件

#VSRCS = top.v bcd7seg.v

CSRCS = $(shell find $(abspath ./csrc) -name "*.c" -or -name "*.cc" -or -name "*.cpp")

#CSRCS = sim_main.cpp

CSRCS += $(SRC_AUTO_BIND)

#CSRCS = sim_main.cpp auto_bind.cpp

include $(NVBOARD_HOME)/scripts/nvboard.mk

#在该Makefile中引用其他Makefile

INCFLAGS = $(addprefix -I, $(INC_PATH))

#INCFLAGS = -I

CFLAGS += $(INCFLAGS) -DTOP_NAME="\"V$(TOPNAME)\""

#CFLAGS = -I -DTOP_NAME="\"Vtop\""

LDFLAGS += -lSDL2 -lSDL2_image

$(BIN): $(VSRCS) $(CSRCS) $(NVBOARD_ARCHIVE)

#./build/top文件的建立依赖于 top.v bcd7seg.v sim_main.cpp auto_bind.cpp 以及verilator仿真可执行文件

@rm -rf $(OBJ_DIR)

$(VERILATOR) $(VERILATOR_CFLAGS)\

--top-module $(TOPNAME) $^\

$(addprefix -CFLAGS , $(CFLAGS)) $(addprefix -LDFLAGS , $(LDFLAGS)) \

--Mdir $(OBJ_DIR) --exe -o $(abspath $(BIN))

# verilator -MMD --build --cc -O3 --x-assgin fast --x-initial fast --noassert --trace \

#--top-module top top.v bcd7seg.v sim_main.cpp auto_bind.cpp \

#-CFLAGS -I -DTOP_NAME="\"VTOP\"" -LDFLAGS -lSDL2 -lSDL2_image \

#--Mdir ./build/obj_dir --exe -o ./build/top

#--top-module top 指定顶层文件名 --Mdir 将生成的文件都放入obj_dir目录中 --exe -o ./build/top 产生可执行文件并指定名字为./build/top

all: default

run:$(BIN)

@$^

#make run 执行可执行文件 ./build/top

clean:

rm -rf $(BUILD_DIR)

.PHONY: default all clean run

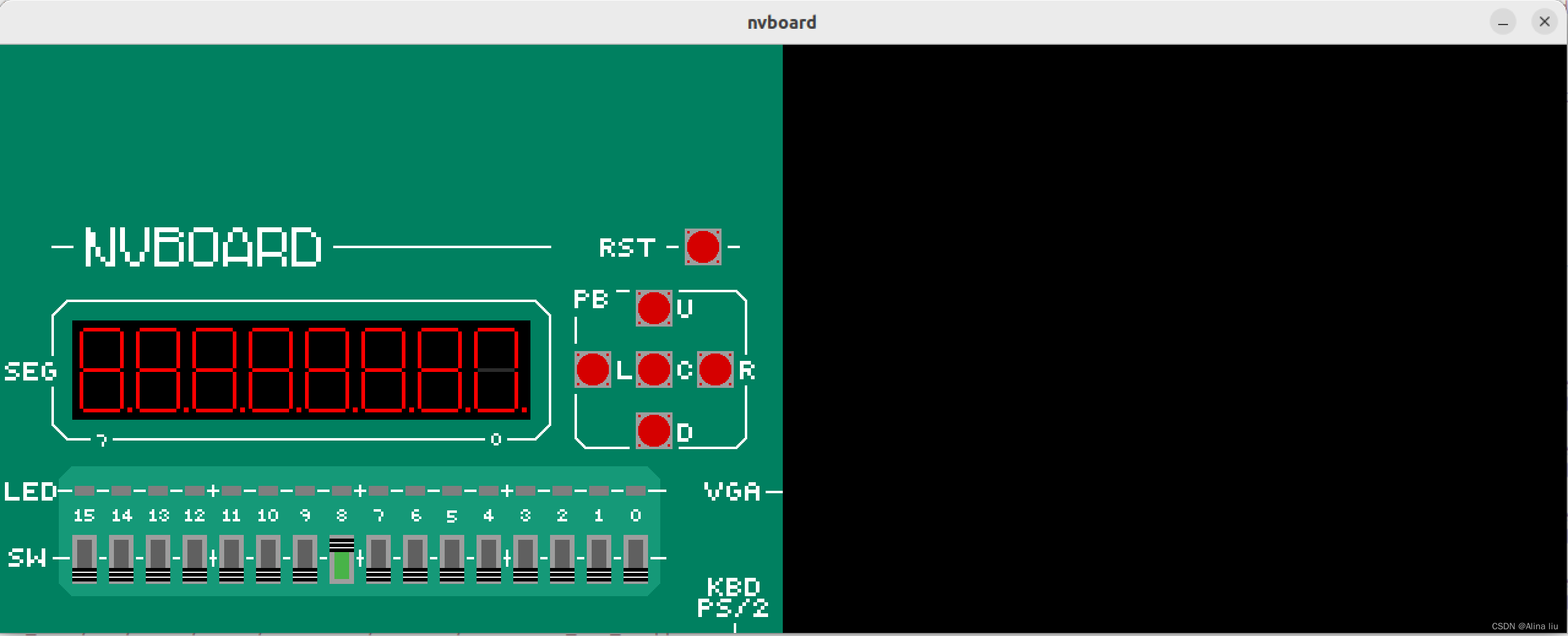

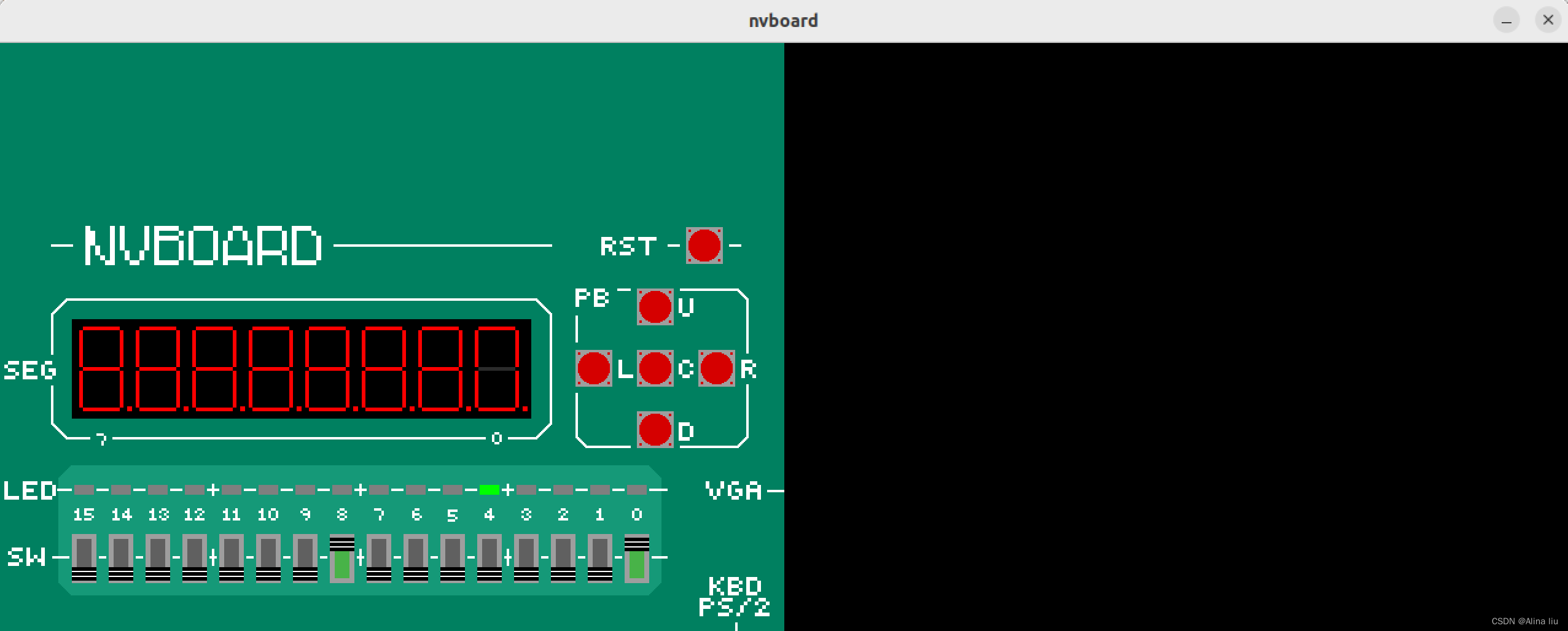

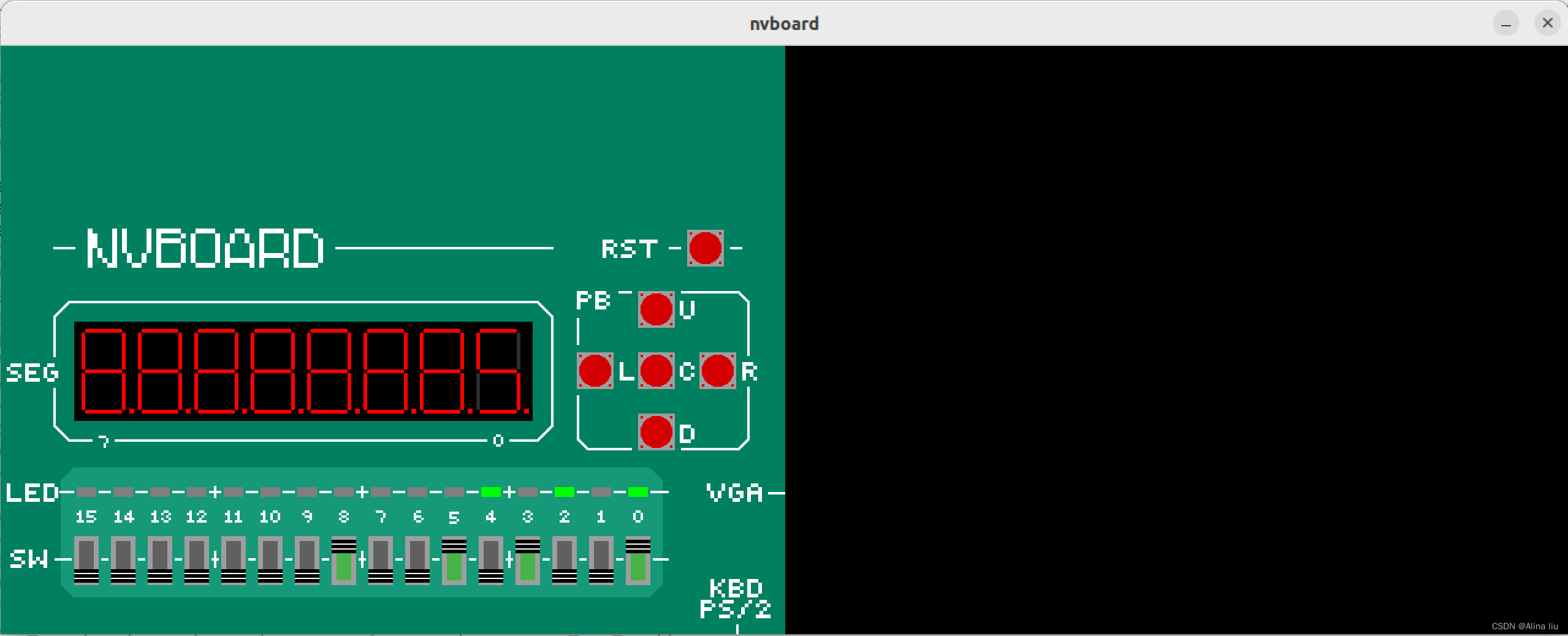

结果展示

1653

1653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?