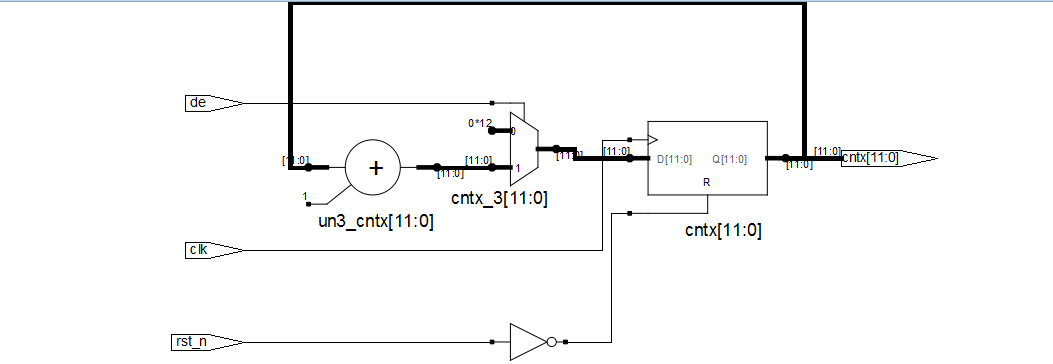

写verilog 好多时候,应该知道自己写的代码电路结构是什么样子, 下面分析一下:

module tb(

input clk,

input rst_n,

input de,

output [11: 0] cntx

);

reg [11: 0] cntx;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

cntx <= 12'h0;

else if(~de)

cntx <= 12'h0;

else

cntx <= cntx + 12'h1;

end

endmodule

3125

3125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?