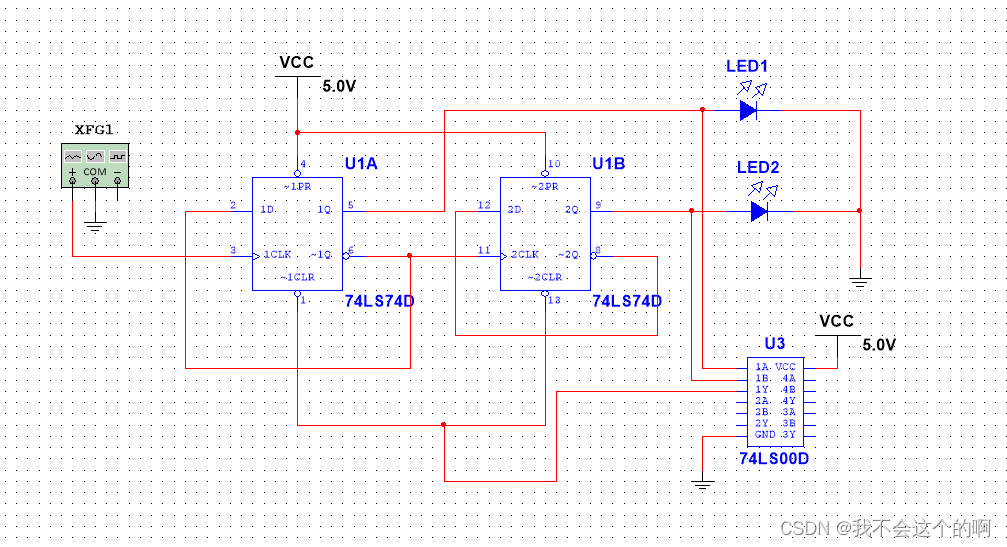

电路设计

三进制加法器在四进制的基础上改进

要求00>01>10>00循环

需要在11的时候恢复00状态,考虑用CLR(Rd)清零位来实现。

清零端低电位有效 ,当输出11时加一个与非门正好可以实现为清零位提供低电平

而当输出是00 01 10 三种状态时,清零位都是高电平,不影响原来四进制的要求

因此可以将两个清零位接入与非门的输出端 Q1与Q2 接入与非门的输入端

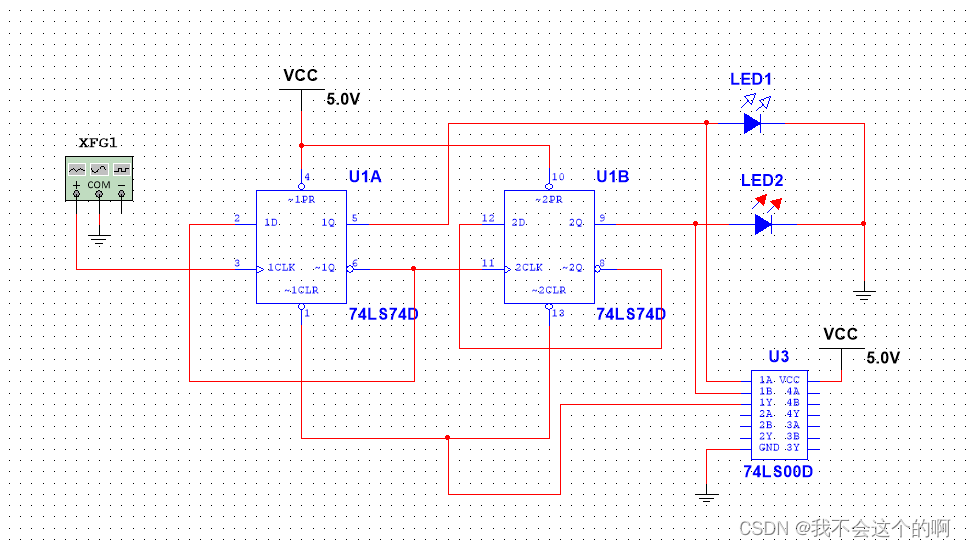

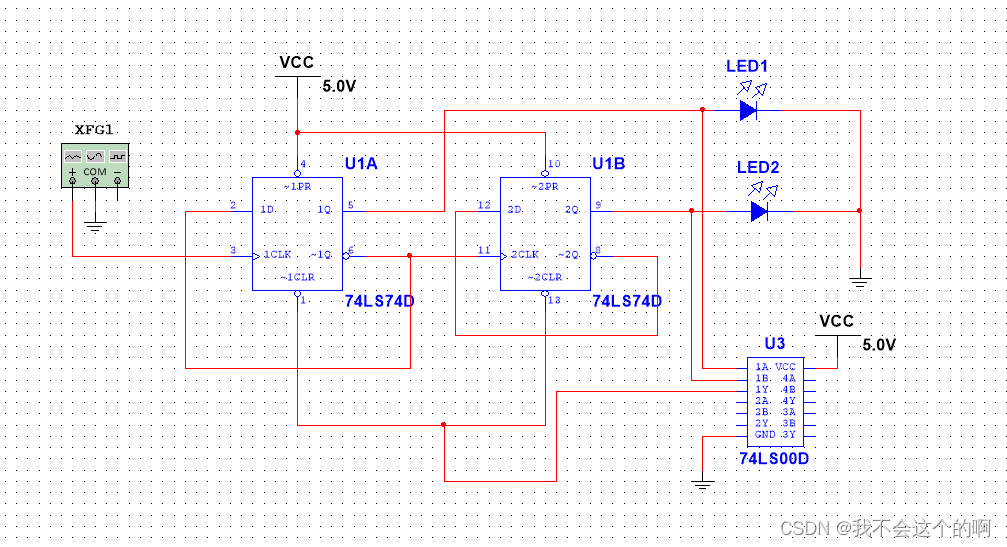

仿真观察三种输出状态

问题:当Q1 Q2是1 1时,会有一瞬间输出11 便马上会被清零,仿真可以看到一瞬间两个led全亮

实际搭建电路不知道是否会观察到。

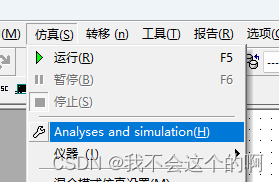

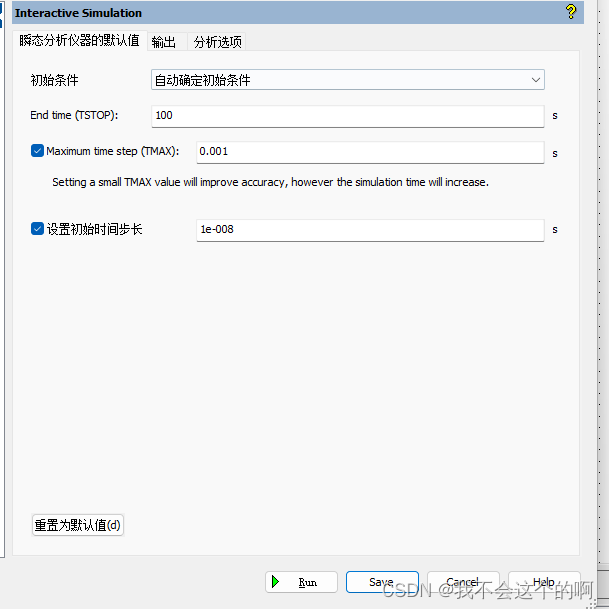

想自己仿真遇到这个(Transient time point calculation did not converge)错误提示时,可以这样修改。

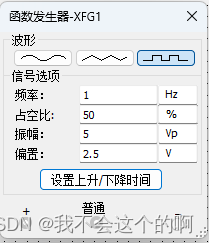

函数发生器参数。

函数发生器参数。

3644

3644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?