reg与wire

wire型数据常用来表示用于以assign关键字指定的组合逻辑信号。Verilog程序模块中输入输出信号类型缺省时自动定义为wire型。wire型信号可以用作任何方程式的输入,也可以用作“assign”语句或实例元件的输出。

reg型数据常用来表示用于“always”模块内表示时序逻辑电路,常代表触发器。通常,在设计中要由“always”块通过使用行为描述语句来表达逻辑关系。在“always”块内被赋值的每一个信号都必须定义成reg型。注意,always中的reg不一定只表示时序逻辑电路,也可以表达组合逻辑电路,取决于具体情况。

以上内容不过多介绍,书本上都有。下面介绍构建module和使用例化好的module时输入输出信号的类型要求。

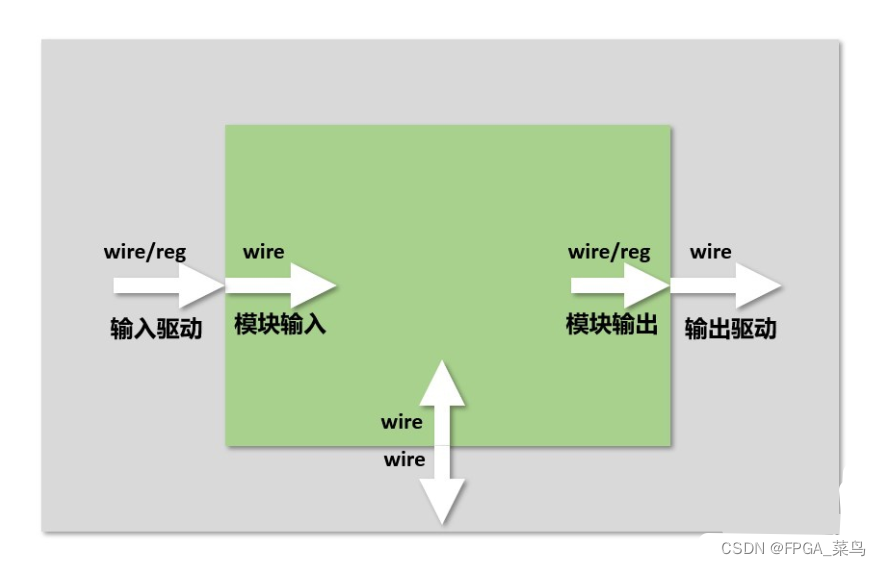

如上图,构建一个模块module时,

input必须是wire;(输入不定义默认就是wire)

output可以是wire也可以是reg;(输出不用赋值就默认wire,要赋值就定义reg)

inout必须是wire;

注:INOUT类型一般信号线用做总线等双向数据传输的时候。就是一个端口同时做输入和输出。 inout 在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻’Z’。当 inout 端口不输出时,将三态门置高阻。

使用例化好的模块时,

外部连接input端口的可以是wire也可以是reg;(比如写testbench时,与输入连接的通常定义为reg,但也可以是wire)

外部连接output端口的必须是wire;(参考test bench)

外部连接inout端口的必须是wire;

以上内容参考自下文:

链接: Verilog语法之三:变量

329

329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?