本文有很多地方的介绍做了简化,比如结构,浮栅晶体管如何充电,如何放电……但是不影响你理解它,记住它。

1 NOR Flash

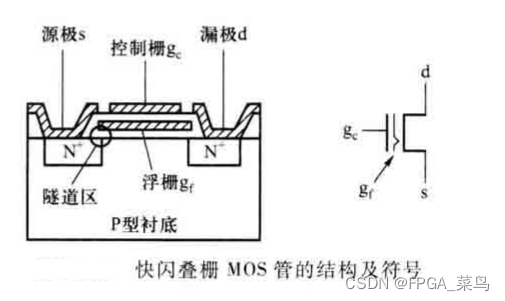

1.1 NOR Flash的浮栅晶体管

NOR Flash中的浮栅晶体管又叫快闪叠栅MOS管。其区分0、1的方式与EPROM、EEPROM并无区别,有区别的是它们充放电的方式以及原理。

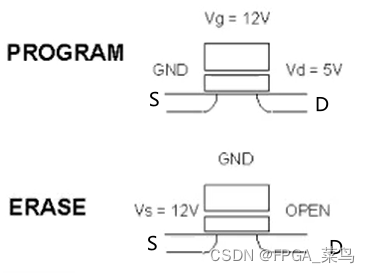

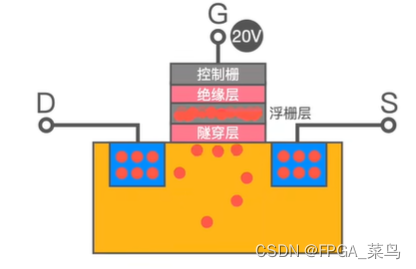

编程时,是1变为0的过程。此时,在DS之间加一个大电压使得漏极和衬底之间雪崩(能雪崩一是因为工艺尺寸的变化,二是设计上有意而为之),产生高能沟道热电子。此时在控制栅加高电压,雪崩的热电子就能被吸引到浮栅。所以,编程使用的是沟道热电子注人(CHE)( Channel HotElectron Injection)效应。这也是为什么NOR Flash相比于 NAND Flash写入速率较低,不适用于频繁擦除/写入场合。

擦除时,是0变为1的过程。此时在源极加一个大电压,由于隧道区很薄,电子就能从隧道区回到衬底。与编程不同,擦除用的是F-N隧道效应(FowlerNordheim tunneling)

1.2 NOR Flash名字的由来

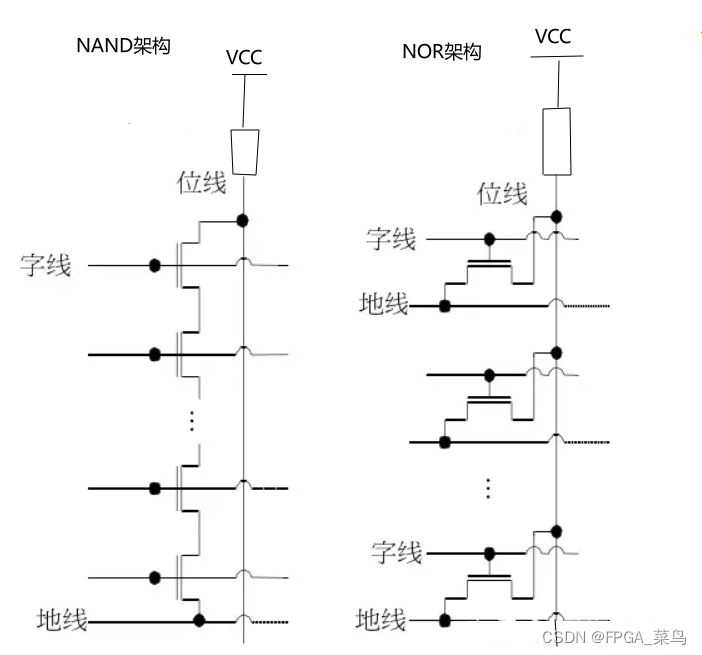

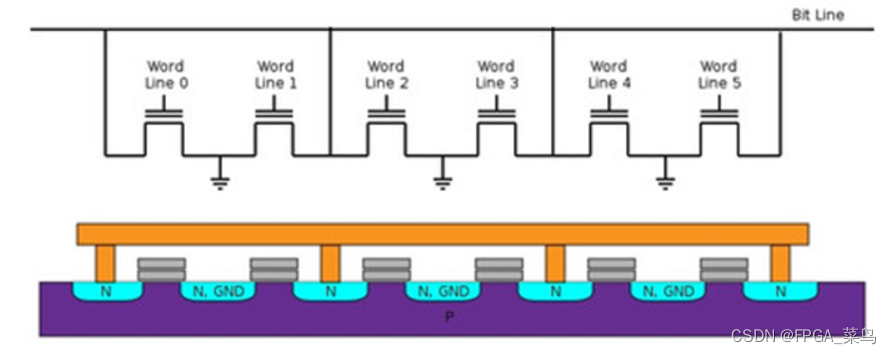

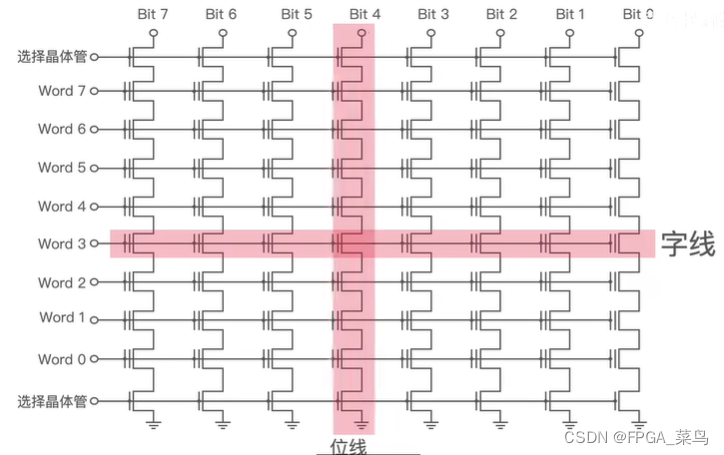

NOR Flash的NOR为NOT OR(或非)之意,NAND Flash的NAND则为NOT AND(与非)之意,而该名称的命名是与两种FLAHS的架构有关的,如图所示:

可以看到,NAND Flash的浮栅晶体管是串联在位线上的,而NOR Flash的浮栅晶体管则是并联在位线上的。如果假设字线上加逻辑电平1时导通,0时截止,则NAND架构必须全1才能在位线顶端读到0,即与非逻辑;NOR架构则是字线上全0才能在位线上读到1,即或非逻辑。

1.3 NOR Flash的结构

NOR Flash的结构原理图如下。每个位线下的基本存储单元是并联的,当某个字线被选中后,就可以实现对该4位的读取。左侧加个译码器,上方加个输入输出缓冲器,组成的就是最经典的存储器结构。

1.4 NOR Flash结构上的遗憾

由于NOR Flash采用并联在位线上的方式,其需要大量的空间存放金属位线,因此NOR Flash的存储密度较低,无法适用于需要大容量存储的应用场合。

2 NAND Flash

1.1 NAND Flash的浮栅晶体管

NAND Flash的浮栅晶体管与NOR Flash的浮栅晶体管在充电方式上也有区别。

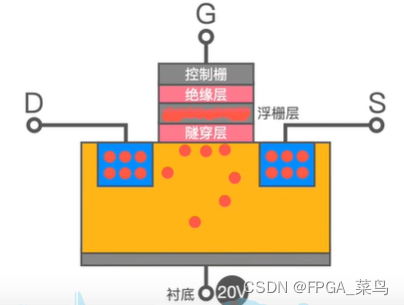

编程时,是1变为0 的过程。此时,只需在控制栅加高电压,就能吸引衬底电子到浮栅。所以,编程用的是F-N隧道效应(FowlerNordheim tunneling)。

擦除时,是0变为1的过程。此时在源极加一个大电压,由于隧穿层很薄,电子就能被电场吸回衬底。与编程一样,擦除用的是F-N隧道效应(FowlerNordheim tunneling)。

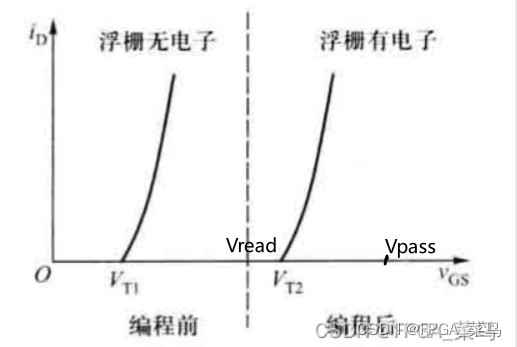

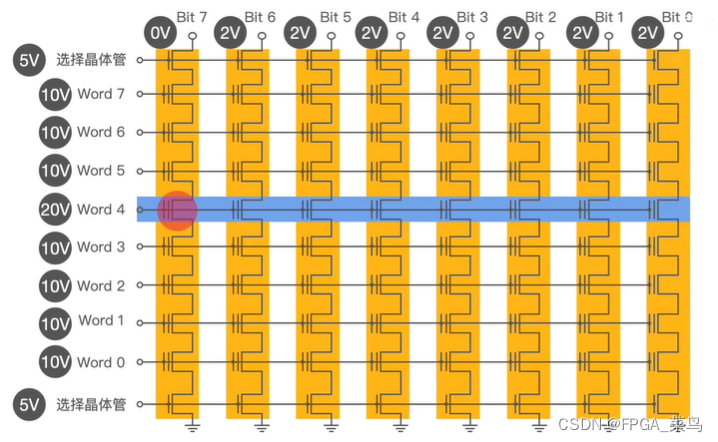

最终的结果,就是导通电压的变化。vth小于Vread的即读到1,大于Vread即读到0。大于两种导通电压的电压叫Vpass,这里设定为10V。

2.2 NAND Flash的结构

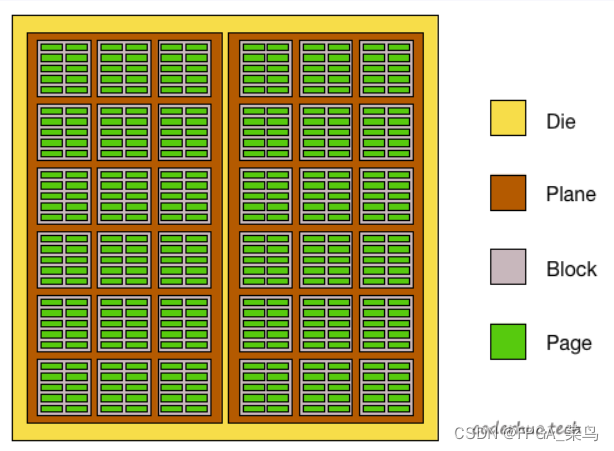

NAND Flash中存在下面几个基本概念:die、plane、block、page(page对应于普通硬盘或NOR Flash中的sector,即常说的扇区)。

每个芯片包含一个或多个die。

每个die包含一个或多个plane(通常是1个或2个)。

每个plane包含多block,block是最小擦除单元。

每个block包含多个page, page是最小的读写单元。

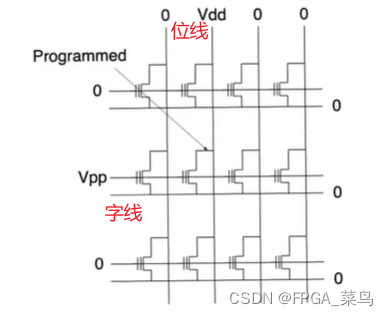

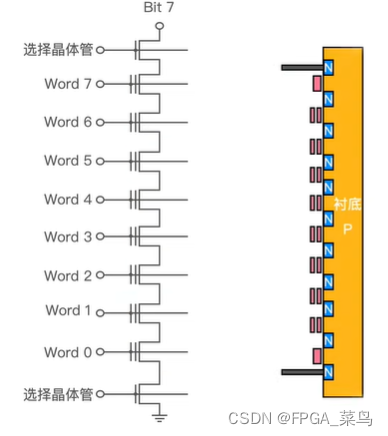

下图是一个block的结构,每根字线连接的浮栅晶体管构成一个page ,整个面构成一个block。前面提到,NAND Flash采用并联的结构。这种结构与以往介绍的存储器结构都不同,其读擦写的方法也差别很大。

每个block的浮栅晶体管都制造在同一个P衬底上,擦除时只需要在衬底上接高电压即可。这也是为什么擦除的最小单位是block。

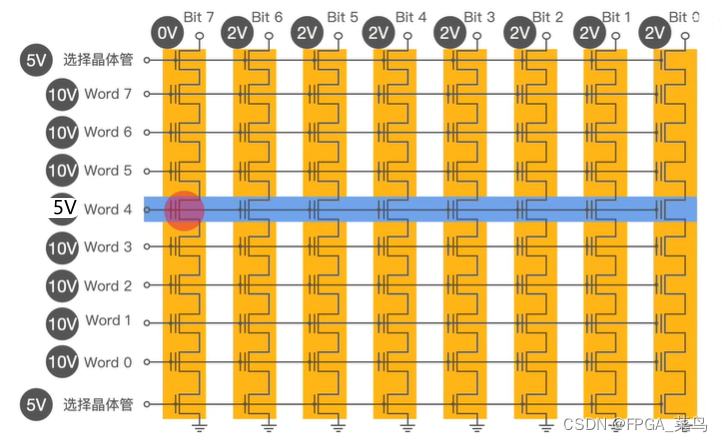

编程时,给需要编程的字线上施加20V的编程高压,其他字线上施加10V的Vpass,使它们导通。在位线的处理上,我们将要写0的位位线接0V,其他接2V。由于沟道效应的影响,这些位不会被写入0。这样,我们就写入了11111110。

读取时,在要读取的位线上施加5V Vread。如果此时该位线上有电流,说明该bit位为1;如果没有电流,说明该位经过编程,提高了浮栅晶体管的导通电压,导致5V不能使其导通。

实际上,为了增大NAND Flash的容量,一行(字线)上有成千上万个晶体管,这就是为什么一次编程的最小单位是page;一面也不可能只有八行;整个存储器也有上千个这样的block。

2.2 拓展:SLC、MLC和TLC

实际上,浮栅晶体管并不存在绝对的空和满状态,其中的电子数目可以处于空和满之间的任一个状态。

由此可见,可以根据晶体管中电子的数目来指示二进制的0和1。比如在SLC(Single Level Cell)中,晶体管中电子数目小于50%的时候代表1,大于50%的时候代表0。

SLC是对电子数目做的一阶量化,所以一个晶体管可以代表两个状态:0和1。如果我们对晶体管中的电子数目做二阶量化,一个晶体管就可以代表四个状态:少于25%代表00,25% ~ 50%代表01,50% ~ 75%代表10、大于75%代表11。这就是MCL(Multi Level Cell)的做法。

当然我们还可以对晶体管中的电子数目做三阶量化,一个晶体管就可以代表八个状态:000、001、010、011、100、101、110、111。这是TLC(Three Level Cell)的做法。

也就是说,量化等级越高,一个晶体管可以表示的状态越多,存储密度就越大,同等数量的存储单元组成的存储介质,存储容量也越大。

这样,原本一个bit的浮栅晶体管现在能存储3bit数据。这也是为什么如今的SSD容量如此之大的原因。

借鉴资料:

1: 固态硬盘的缓存是干什么的?

3: SSD是如何存储数据的?

3065

3065

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?