本次更新内容为STM32CubeMX生成STM32H7 工程项目应用中Pinout&Configuration关于Analog(ADC)部分说明,文中Tips是比较易出错的点,多多关注。欢迎关注本公众“硬件开发不完全攻略”,上传可能中可能有些图片可能分辨率有降低,后台回复“STM32”,获取源文档。

1Pinout&Configuration

1.1System Core

1.2Analog

1.2.1ADC1/2/3

1.2.1.1功能要点

1)硬件TIMER直接触发

可以触发ADC起动的TIMER有:TIM1、TIM2、TIM3、TIM4、TIM6、TIM8、TIM15、HRTIM1、LPTIM1.

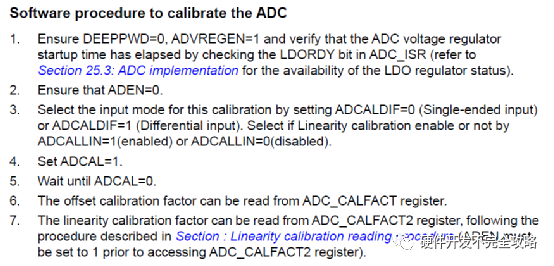

2)ADC校准功能

此功能需落实对比是否有作用,这个模块是怎么用的。之前在某设备评估时,OFFSET校准还可以,但是LINEARITY校准后,精度反而变差了。

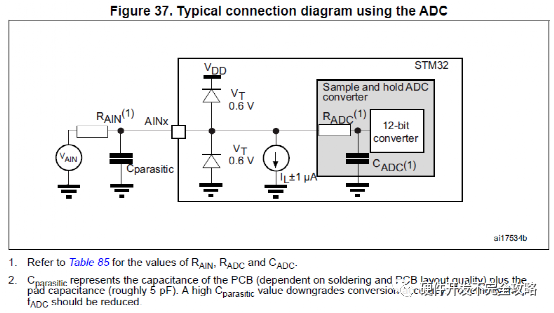

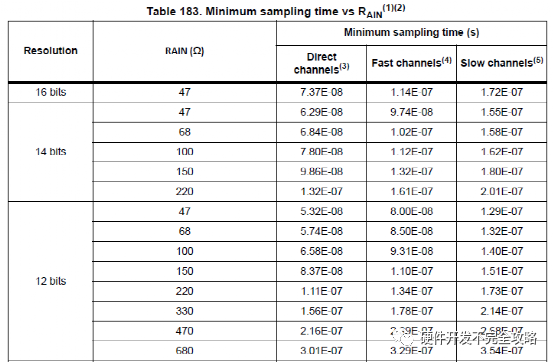

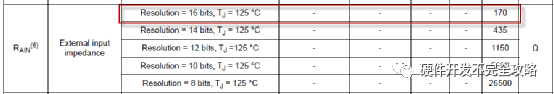

3)ADC负载能力及转换频率

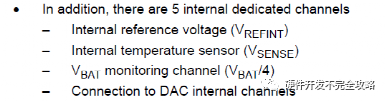

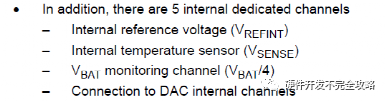

4)ADC有5个内置的通道可选

5)三个ADC应用配合方案

为了保证三路AD+DMA的同步,三路DMA的优先级要有调整,ADC3的DMA中断优先级设置为最低,ADC3-DMA完成中断,作为AD采样完成中断。

暂时先采用三路DMA都产生中断,每个中断读取自己的采样结果,同时FLG++。正常情况下,ADC3-DMA完成中断时,三个FLG应该是相同的,这样才说明三路都采样完成了。

另外,为了避免偶然的结果导致某一路没有采完,除了正常的采样外,最后再增加一路,这样即使最后一路没采完,也不会导致实际应用的错误。在FLG不等时,ADC3-DMA中断中要再重新读取有异常的ADC路的转换结果。

也可以在ADC3-DMA,相比于ADC1/2增加一路(例如:采内部温度),这样更能保证ADC3-DMA完成时,ADC1/2也完成了。

配置要求:ADC3-DMA的优先级 <<低于ADC2-DMA的优先级 <<低于adc1-dma的优先级。如果三个adc均配置,则使用adc3-dma的dma完成中断作为整个的采样完成中断。< span="">

使用DMA时,不需要使能ADC模块的中断

1.2.1.2ADC采样转换时间及过采样配置设计方法

ADC模块的详细应用分析,见文档《STM32H730--AD性能评估—20210513》

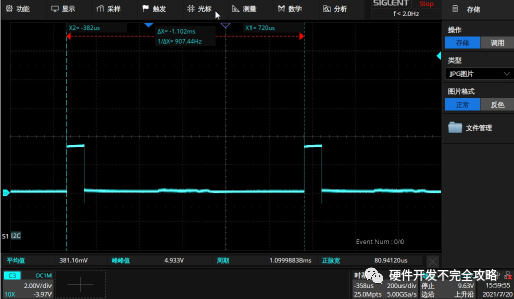

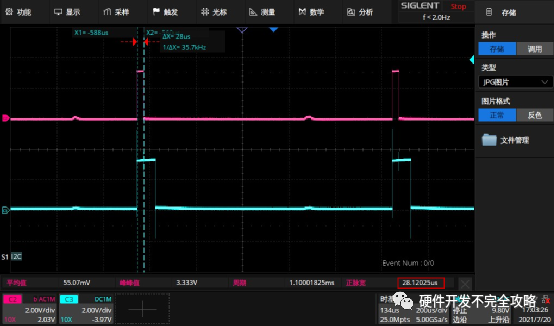

1)ADC1采样转换时间分析及测试

ADC时钟输入:40M,2分频,过采样次数:16,采样时间:16.5 CYCLES,4个通道,

只使用ADC1,ADC1采样时间:81US,每通道时间:81/4=20.25US

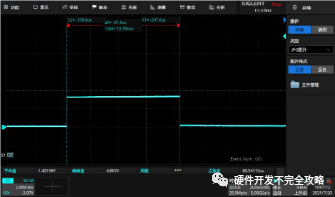

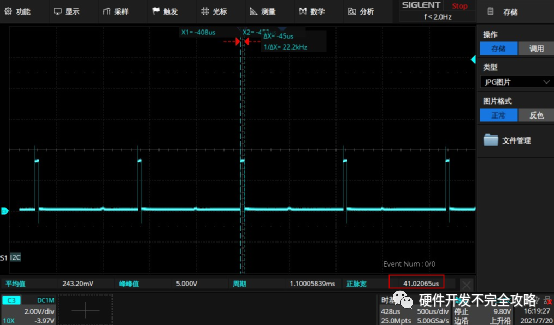

ADC时钟输入:40M,2分频,过采样次数:8,采样时间:16.5 CYCLES,4个通道,

只使用ADC1,ADC1采样时间:41US,每通道时间:41/4=10.25US

注:直接看ΔX是45US,是因为示波器的原因,在调大时间间隔时,这个ΔX的值也会变,根据分辨来变化,所以,不准,右下角的正脉宽是对的。

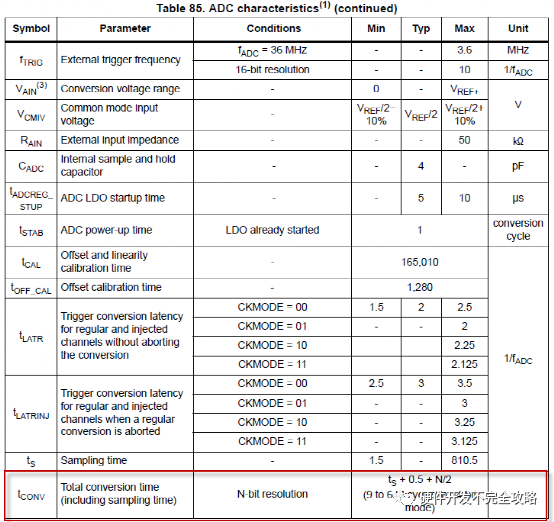

根据上面的数据,每通道的采样转换时间:10.25/8=1.28125US,ADC工作频率20M,Tcyc=0.05us.每通道采样转换所需的CYC数:1.28125/0.05=25.625 CYC

根据手册的计算公式:Tconv =( ts + 0.5 +N/2) CYCs = 16.5+0.5+16/2 = 25

与理论计算基本一致。

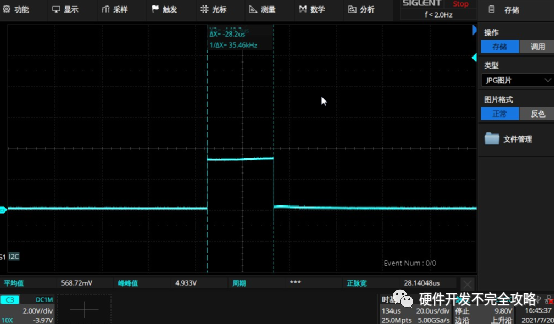

ADC时钟输入:40M,2分频,过采样次数:8,采样时间:8.5 CYCLES,4个通道,

只使用ADC1,ADC1采样时间:28.2US,每通道时间:28.2/4=7.05US

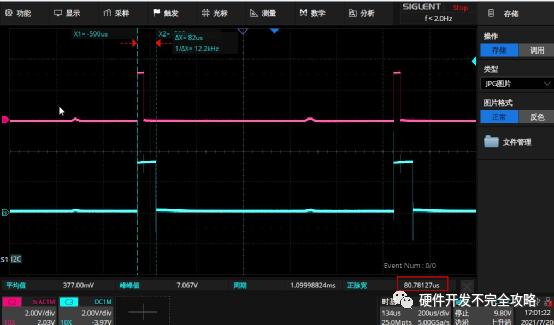

2)ADC2采样转换时间分析及测试

同时使用ADC1,ADC2:

ADC时钟输入:40M,2分频,过采样次数:8,采样时间:8.5 CYCLES,4个通道,

ADC1采样时间:28.12US,每通道时间:28.12/4=

ADC2时钟输入:40M,2分频,过采样次数:16,采样时间:16.5 CYCLES,4个通道,

ADC2采样时间:80.781US,每通道时间:80781/4=

注:浅蓝线是ADC2

与只使能一个ADC1时的时间是一致的。

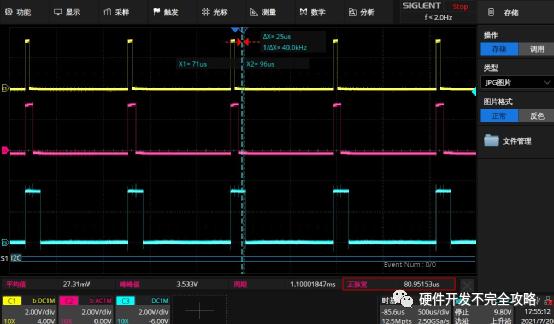

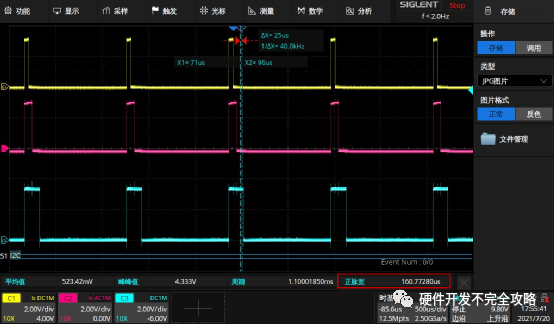

3)ADC3采样转换时间分析及测试

同时使用ADC1,ADC2,ADC3:

ADC时钟输入:40M,2分频,过采样次数:8,采样时间:8.5 CYCLES,6个通道,

ADC1采样时间:41.751 US,每通道时间:41.751 /6=

ADC2时钟输入:40M,2分频,过采样次数:8,采样时间:16.5 CYCLES,8个通道,

ADC2采样时间:80.951US,每通道时间:80.951/8=

ADC3时钟输入:40M,2分频,过采样次数:16,采样时间:16.5 CYCLES,8个通道,

ADC3采样时间:80.781US,每通道时间:80781/4=

4)ADC采样时间分析小结

ADC配置选用:输入频率20M,不分频。过采样次数8次,采样时间8.5 CYC,每个通道连续采两次,使用后一次的值。

根据手册的计算公式:Tconv =( ts + 0.5 +N/2) CYCs = 8.5+0.5+16/2 = 17

相当于每一路采样所需时间:7.05*2=14.1US,以64点采样为例,312.5/14.1=22路。

如果路数需要的不是很多,为了采样更稳定,可以将采样时间增大一级16.5。

可以对比一下减少过采样次数,增大采样时间,是不是效果更好?

1.2.1.3配置

以ADC1为例,详细展示各个参数的配置。此配置方案使用TIMER硬件触发ADC起动,DMA实现多通道顺序采样。

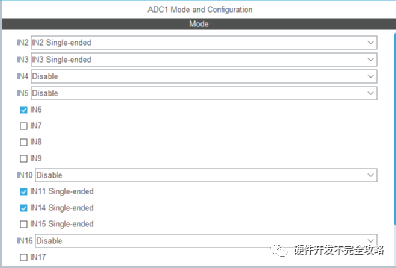

ØSTEP1:配置使能各个ADC通道

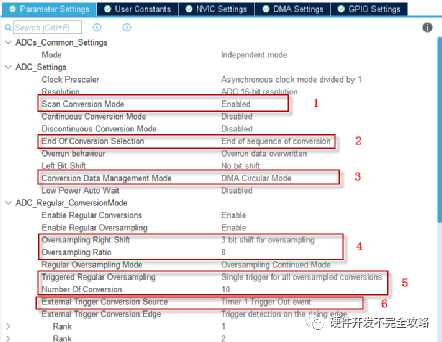

ØSTEP2:配置ADC公共参数

Tips1:如下图的3,需要选择DMA Circular Mode;

Tips2:如下图的4,过采样次数与右移BIT位要对应一致,保证采样结果没有倍数变化(例如:过采样8次,右移3位;过采样16次,右移4位);

Tips2:如下图的5,每一个ADC的Number Of Conversion最多支持16路

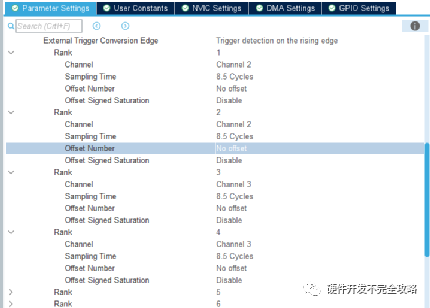

ØSTEP3:配置ADC各通道参数

各通道可独立配置ADC的Channel序号、采样时间:Sampling Time,每个Channel可以配置到多个通道中。

ØSTEP4:配置ADC--DMA

1.2.1.4Tips

1)如果有两路信号会用于计算合成一路新的信号,尽量将这两路信号分配在两个ADC中,这样可以尽可能的同步采样。例如将UAB、UBC,分别配置在ADC1、ADC2上,合成UCA精度会更高,避免繁杂的校准计算工作,硬件设计时也需要注意尽可能按此来设计;

2)可以监视CPU的工作温度、VBAT、内部VREFINT

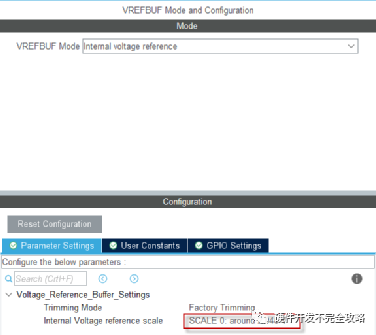

1.2.2VREFBUF

Tips1:如下图所示,CubeMX配置显示的内容与手册上不一致,有BUG。这里显示的2.048V,其实应该是2.5V;

2048

2048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?