原工程

器件:2812,

外部晶振:10MHz

外部晶振通过锁相环

外部晶振通过锁相环

SysCtrlRegs.PLLCR = 0xa; //clk*10/2

经过这个程序设置后,

SYSCLKOU=10*5=50MHz

SYSCLKOU=10*5=50MHz

SysCtrlRegs.HISPCP.all = 0x0000;

SysCtrlRegs.LOSPCP.all = 0x0002;

HIGH SPEED CLOCK=SYSCLKOU/1=50MHz

HIGH SPEED CLOCK=SYSCLKOU/1=50MHz

LOW SPEED CLOCK=SYSCLKOU/4=12.5MHz

SPI时钟是使用的低速时钟

再来看XINTF的时钟,主要看他的DSP外部存储的1分区

XintfRegs.XINTCNF2.bit.XTIMCLK = 0x0000;

XintfRegs.XINTCNF2.bit.CLKMODE =0;

XTIMCLK=SYSCLKOUT=50M,XCLKOUT=50M

//Zone 1

XintfRegs.XTIMING1.bit.USEREADY = 0;

XintfRegs.XTIMING1.bit.XWRTRAIL = 2;//10

XintfRegs.XTIMING1.bit.XWRACTIVE = 2;

XintfRegs.XTIMING1.bit.XWRLEAD = 2;

XintfRegs.XTIMING1.bit.XRDTRAIL = 2;

XintfRegs.XTIMING1.bit.XRDACTIVE = 2;

XintfRegs.XTIMING1.bit.XRDLEAD = 2;

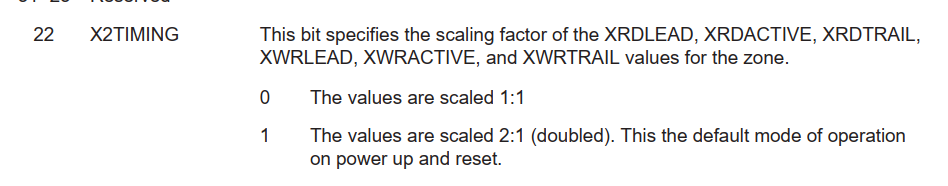

XintfRegs.XTIMING1.bit.X2TIMING = 1;

它的读、写的Lead Active Trail 都是4个SYSCLOUT时钟周期

它的读、写的Lead Active Trail 都是4个SYSCLOUT时钟周期

根据这个来看 他的XRD/XWE 低电平有效的时间为4个SYSCLK时钟周期

根据这个来看 他的XRD/XWE 低电平有效的时间为4个SYSCLK时钟周期

也就是50M/4=12.5M

他的XZCS为12个SYSCLKOUT,50M/12=4.167M

XA=50M/12。

XD在读的时候,可以理解为最快50M/12内读一次

XD在写的时候,存在50M/8那么久

综合FPGA来看,他选中的时长为4个时长,也就是4/50M 这么多秒 一个周期为12个SYSCLKOUT 但是只有其中1/3的周期 对FPGA来说 是有效的

4648

4648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?