最近使用STM32F030用到了IIC配置,需要配置SDA为输入或输出用到MODER寄存器,查找资料找了好久(主要是某度搜出来的全是垃圾,没有用于的资料),为了后期开发有可能用到,特在此记录。

简介

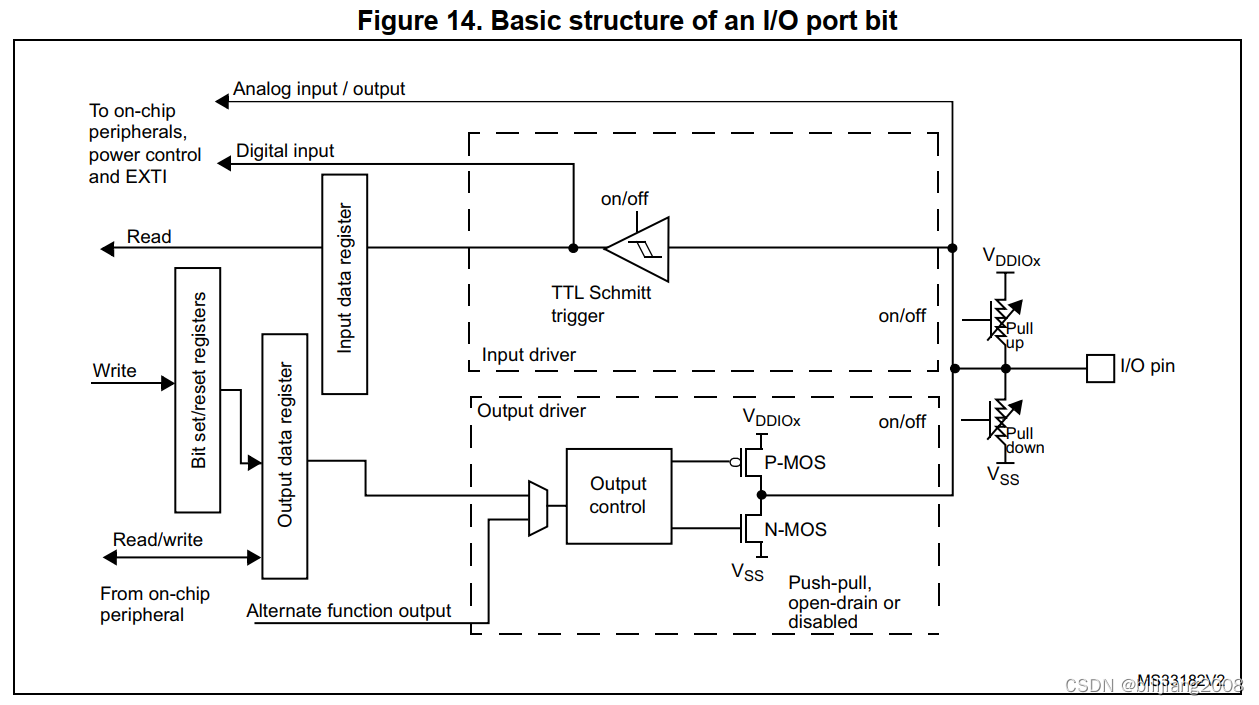

每个通用I/O端口有四个32位配置寄存器(GPIOx MODER,GPIOx_OTYPER、GPIOx_OSPEEDR 和 GPIOx_PUPDR),两个 32 位数据寄存器(GPIOx_IDR和GPIOx_ODR)和一个32位设置/重置寄存器(GPIOx_BSRR)。

端口A和B还有一个32位锁定寄存器(GPIOx_LCKR)和两个32位替代函数选择寄存器(GPIOx_AFRH和GPIOx_AFRL)。在STM32F030xB和STM32F030xC设备上,端口C和D也有两个32位的备用功能选择寄存器(GPIOx_AFRH和GPIOx_AFRL)。

GPIO的主要特性

输出状态:推拉或开漏+上拉/下拉

从输出数据寄存器(GPIOx_ODR)或外设(替代函数输出)输出数据

每个I/O的速度选择

输入状态:浮动,上拉/下拉,

模拟输入数据到输入数据寄存器(GPIOx_IDR)或外围设备(备用功能输入)位设置和重置寄存器(GPIOx_BSRR),用于按位写访问GPIOx_ODR,提供锁定机制(GPIOx_LCKR),

用于冻结端口A或B I/O端口配置。

模拟功能备用函数选择寄存器(每l/O最多可能有16个AFs)快速切换,能够改变每两个时钟周期高度灵活的引脚多路复用允许使用I/O引脚作为gpio或作为几个外围功能之一

GPIO功能描述

根据数据表中列出的每个I/O端口的具体硬件特性,通用I/O (GPIO)端口的每个端口位可以通过软件以几种方式单独配置:

输入浮动

输入上拉

Input-pull-down

模拟

输出开漏与上拉或下拉

能力输出推拉与上拉或下拉能力交替功能推拉与上拉或下拉能力交替功能开启排水与上拉或下拉能力每个I/O端口位都可以自由编程,但是I/O端口寄存器必须作为32位字、半字或字节访问。

I/O端口控制寄存器

每个GPIO端口有4个32位内存映射控制寄存器(GPIOx_MODER, gpiox_otype, GPIOx_OSPEEDR, GPIOx_PUPDR),可以配置最多16个I/ o。GPIOx_MODER寄存器用于选择I/O模式(输入,输出,AF,模拟)。gpiox_otype和GPIOx_OSPEEDR寄存器用于选择输出类型(推拉或开漏)和速度。GPIOx_PUPDR寄存器用于选择任意I/O方向的上拉/下拉。

I/O端口数据寄存器

每个GPIO有两个16位内存映射的数据寄存器:输入和输出数据寄存器(GPIOx_IDR和GPIOx_ODR)。GPIOx_ODR存储要输出的数据,可读可写。通过I/O输入的数据存储在输入数据寄存器(GPIOx_IDR)中,这是一个只读寄存器。参见第8.4.5节:GPIO端口输入数据寄存器(GPIOx_IDR) (x = A..D, F)和章节8.4.6:GPIO端口输出数据寄存器(GPIOx_ODR) (x=A..D, F)为寄存器。

I/O数据位处理位集

重置寄存器(GPIOx_BSRR)是一个32位寄存器,它允许应用程序设置和重置输出数据寄存器(GPIOx_ODR)中的每个位。位集重置寄存器的大小是GPIOx_ODR的两倍。

对于GPIOx_ODR中的每一位,对应GPIOx_BSRR中的两个控制位:BS(i)和BR(i)。当写入1时,位BS(i)设置相应的ODR(i)位。当写入1时,位BR(i)重置ODR(i)对应的位。在GPIOx_BSRR中向O写入任何位都不会对GPIOx_ODR中相应的位产生任何影响。如果试图同时设置和重置GPIOx_BSRR中的位,则设置操作具有优先级。使用GPIOx_BSRR寄存器来更改GPIOx_ODR中单个位的值是“一次性”效果,它不会锁定GPIOx_ODR位。GPIOx_ODR位始终可以直接访问。

GPIOx_BSRR寄存器提供了一种执行原子位处理的方法。在位级编程GPIOx_ODR时,软件不需要禁用中断:可以在单个原子AHB写访问中修改一个或多个位。

GPIO锁定机制

通过对GPIOx_LCKR寄存器应用特定的写顺序,可以冻结端口A和端口B GPIO控制寄存器。冻结寄存器是GPIOx_MODER,GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRL和GPIOx_AFRH。要写入GPIOx_LCKR寄存器,必须应用特定的写/读序列。当正确的LOCK序列应用于该寄存器的第16位时,LCKR[15:0]的值用于锁定l/ o的配置(在写入序列中LCKR[15:0]的值必须相同)。当LOCK序列应用于端口位时,该端口位的值不能再被修改,直到下一次MCU复位或外设复位。每个GPIOx_LCKR位冻结控制寄存器中相应的位(GPIOx_MODER,GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRL和GPIOx_AFRH。LOCK序列(参考第8.4.8节:GPIO端口配置锁寄存器(GPIOx_LCKR) (x= A..B))只能通过对GPIOx_LCKR寄存器的一个字(32位长)访问来执行,因为GPIOx_LCKR位16必须与[15:0]位同时设置。更多详细信息请参见章节8.4.8中的LCKR寄存器描述:GPIO端口配置锁寄存器(GPIOx_LCKR) (x=A..B)。

I/O交替函数输入/输出

提供了两个寄存器来为每个I/O选择一个可用的备用函数输入/输出。使用这些寄存器,用户可以根据应用程序的需要将替代函数连接到其他引脚。这意味着使用GPIOx_AFRL和GPIOx_AFRH备用函数寄存器在每个GPIO上复用许多可能的外围函数。因此,应用程序可以为每个l/O选择任意一个可能的函数。AF选择信号对于交替函数输入和交替函数输出是公用的,对于给定I/O的交替函数输入/输出选择一个通道。

外部中断/唤醒线

所有端口都具有外部中断能力。要使用外部中断线,给定的引脚不能配置为模拟模式或用作振荡器引脚,因此输入触发器保持启用。请参阅第11.2节:扩展中断和事件控制器(EXTI)和第11.2.3节:事件管理。

输入配置

当I/O端口被编程为输入时:输出缓冲区被禁用施密特触发器输入已激活上拉和下拉电阻根据GPIOx_PUPDR寄存器中的值被激活在每个AHB时钟周期中,I/O引脚上的数据被采样到输入数据寄存器中对输入数据寄存器的读访问提供了I/O状态

输出配置

当I/O端口被编程为输出时:输出缓冲区已启用:开漏模式:输出寄存器中的“O”激活N-MOS,而输出寄存器中的“1”使端口处于Hi-Z状态(P-MOS从未被激活)推挽模式:输出寄存器中的“O”激活N-MOS,而输出寄存器中的“1”激活P-MOS施密特触发器输入已激活上拉和下拉电阻根据GPIOx_PUPDR寄存器中的值被激活在每个AHB时钟周期中,I/O引脚上的数据被采样到输入数据寄存器中对输入数据寄存器的读访问获取I/O状态对输出数据寄存器的读访问将获得最后写入的值

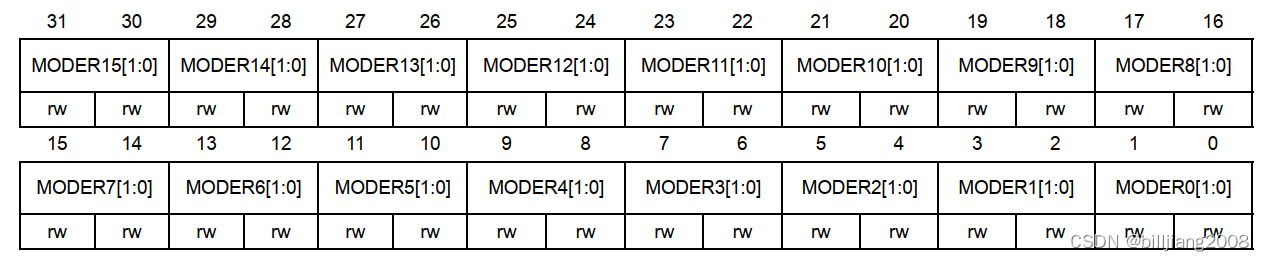

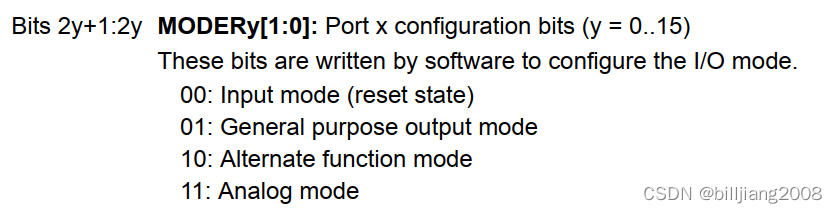

GPIO端口模式寄存器

(GPIOx_MODER) (x=A…D, F)

地址偏移量:0 x00

MODERy[1:0]:端口x配置位(y=0..15)

这些位由软件写入,用于配置I/O模式。

00:输入模式(复位状态)

01:通用输出模式

10:备选功能模式

11:模拟模式

例如配置PA10为输入输出模式

3的二进制表示为11,将11左移2*9=18位(由2y:2y+1确定端口9的配置位,即第19、18位),取反后与上GPIOC->MODER;此操作是使得GPIOC->MODER的19、18位寄存器清零。

0左移9*2=18位,即配置位18/19置为0;此次操作实现配置端口9为输入模式

#define SDA_IN {GPIOA->MODER&=~(3<<(10*2));GPIOA->MODER|=0<<10*2;}

#define SDA_OUT {GPIOA->MODER&=~(3<<(10*2));GPIOA->MODER|=1<<10*2; }

958

958

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?