一、串口传图设计图

这一部分在之前写的SDRAM控制顶层模块的基础上加了pll时钟,之前写的tft4.3寸显示屏控制模块,串口接收数据模块和比特计数器。

pll时钟:之前在初始化部分提到过,此处有四路时钟信号,整体系统、字节接收为开发板自带的50M时钟,另有pll产生的一路9M时钟是给tft4.3寸显示屏驱动,两路相位相差180度(实际考虑电路时延,一般设置为150度)的100M时钟给SDRAM,由于在上升沿读取数据,相位不变的用于时钟计数,用来发送信号、做控制;相位改变180度的时钟上升沿正好在写入数据时的中间,用它来读写数据。(详细记在了初始化那里)

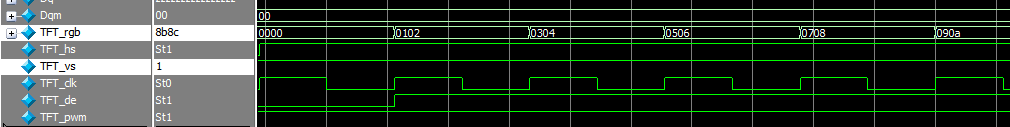

tft4.3寸显示屏控制模块:直接调用之前写的480272的显示屏驱动,tft的场信号控制是确定的,比特数=行像素点列像素点/2(RGB565格式16位的,即比特数的两倍),比特计数器记满即下一帧(场)图像。

串口接收数据模块:在字节接收时,八位字节与之前设计的fifo16位不一致,更改fifo_read为8字节进入,16位字节输出。

比特计数器:对串口接收字节计数,写使能时开始计数,记满一帧则产生图片可显示信号,说明数据已完全写入SDRAM。(此处就可得出使用SDRAM的作用——缓存帧数据)

二、控制信号

assign TFT_begin = (hcount_r==0)&&(vcount_r==0)?1'b1:1'b0; //帧起始标志位信号输出

assign Rd_en = (disp_state && TFT_de)?1'b1:1'b0; //SDRAM控制器读FIFO的读使能

assign TFT_de = dat_ack; //区别显示区和消隐区

dat_ack = ((hcount_r >= hdat_begin)&&(hcount_r < hdat_end))&&

((vcount_r >= vdat_begin)&&(vcount_r < vdat_end))?1'b1:1'b0; //数据、同步信号输出在显示区

parameter img_data_byte = img_h*img_v; //总的数据数目,行列16位的,即比特数的两倍,下面计数的时候要<< 1

三、fifo输入输出位数更改

这个地方开始没有勾选输入输出位数不一致,出了问题,调了好一会儿。

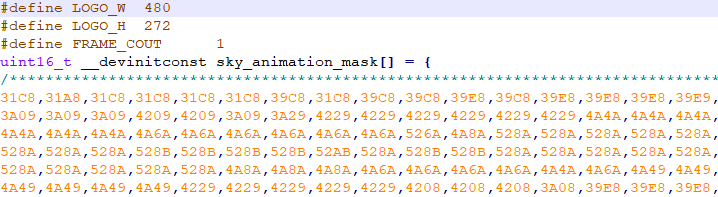

然后串口传图这个地方是把图片转成RGB565比特流的形式,用的小梅哥提供的转换小程序,他是高低位不一致的

.Data_in({Rd_data[7:0],Rd_data[15:8]}), //fifo是{高8,低8};Picture2Hex图片产生数据是{低8,高8},这个地方要进行一个调换

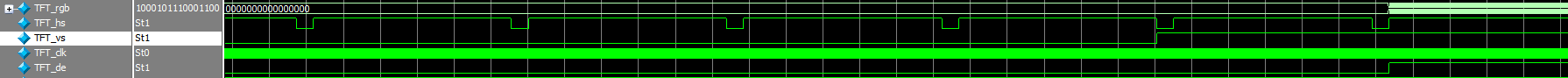

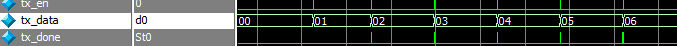

四、仿真

initial

begin

Rst_n = 0;

tx_en = 0;

tx_data = 0;

#(`CLK_PERIOD*200+1)

Rst_n = 1;

//等待初始化完成

@(posedge uart2sdram2tft.sdram.sdram_control.init_done)

#2000;

//串口传输400个数据

repeat(Img_H*Img_V*2)begin

tx_en = 1;

tx_data = tx_data + 1;

#(`CLK_PERIOD)

tx_en = 0;

@(posedge tx_done);

#20;

end

//等待图片可显示状态到来

@(posedge uart2sdram2tft.disp_state); //图片可显示状态行列都为0

@(posedge uart2sdram2tft.TFT_vs); //TFT 场同步信号

@(posedge uart2sdram2tft.TFT_de);

#50000;

$stop;

end

五、实际上开发板传图

1214

1214

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?