目录

前沿

USB专栏对USB的协议、USB Device模式及STM32F103系列单片机USB模块的功能及代码进行了详细的讲解,本专栏将对STM32F407 OTG模块进行一个系列的讲解,主要围绕以下讲解:

- STM32F407 OTG模块的组成

- ULPI简介

- OTG代码获取及代码讲解

1 OTG简介

OTG是一款双角色(DRD)控制器,同时支持USB主机和USB从机模式,主要是通过ID线来区别该设备是主机设备还是从机设备。同时OTG也支持HNP和SRP协议,也就是主机协商和会话请求协议,个人认为这两个协议比较鸡肋,使用比较少,所以不展开讲有关这两个协议涉及到的内容。

2 STM32F407 OTG简介

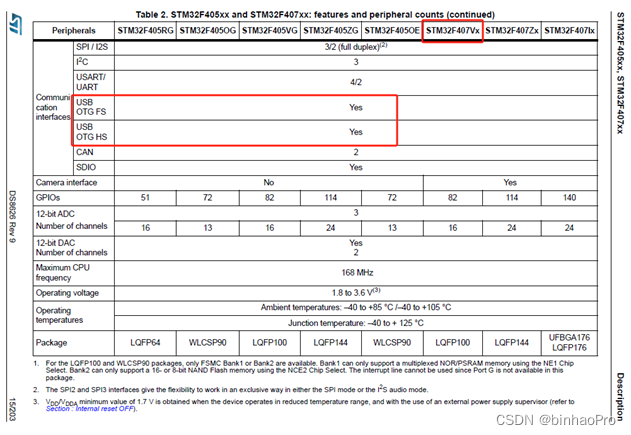

从STM32F40x的数据手册可知,STM32F407有两个OTG模块,分别是USB OTG FS和USB OTG HS。主要区别在于前者支持的最大通信速度为12Mbps(全速模式),后者支持的最大通信速度为480Mbps(高速模式)。

2.1 STM32F407 OTG_FS简介

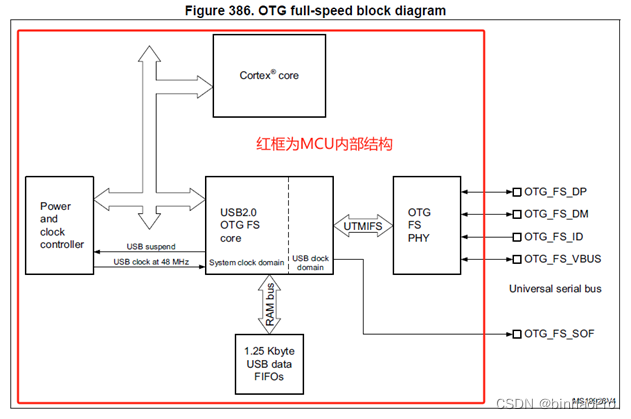

打开STM32F407的用户手册,查看OTG_FS框图,如下所示:

框图分为两部分,一部分是MCU内部结构,另一部分为OTG_FS引出的接口。MCU内部结构是我们不需要关心的部分,这个是芯片设计人员关注的问题。

从MCU内部结构可看出,USB2.0 OTG FS core通过UTMIFS接口与OTG FS PHY通信,所以此设备只支持全速(12Mbps)通信。

2.1.1 引脚定义

从上图可知,开放给嵌入式软件工程师的接口为OTG_FS_DP、OTG_FS_DM、OTG_FS_ID、OTG_FS_VBUS和OTG_FS_SOF引脚,所以我们只需要关注这几条信号线即可(内部的UTMIFS接口可以不关注),引脚对应的功能如下:

| Pin脚 | 功能 | 备注 |

| PA8 | OTG_FS_SOF | SOF输出引脚,对于全速/低速设备,输出的频率为1KHz |

| PA9 | OTG_FS_VBUS | VBUS引脚,通过寄存器选择外部VBUS供电还是内部VBUS供电 |

| PA10 | OTG_FS_ID | ID引脚,拉高/浮空为设备模式,拉低为主机模式 |

| PA11 | OTG_FS_DM | 差分信号负端 |

| PA12 | OTG_FS_DP | 差分信号正端 |

2.2 STM32F407 OTG_HS简介

此框图主要描述了OTG的三大部分:

- OTG HS内核部分

- OTG FS PHY部分

- ULPI接口部分

OTG HS内核部分不是我们这里关注的要点,主要关注OTG FS PHY部分和ULPI接口部分。

2.2.1 OTG_HS内部全速PHY引脚定义

OTG HS模块中的OTG FS PHY可以理解为OTG FS模块中的PHY,他俩的PHY是同一类PHY,都是通过UTMI接口进行通信的,因为在芯片内部,所以我们只关心PHY模块引出的引脚,OTG_HS_DP、OTG_HS_DM、OTG_HS_ID、OTG_HS_VBUS、OTG_HS_SOF。

| Pin脚 | 功能 | 备注 |

| PA4 | OTG_HS_SOF | SOF输出引脚,对于全速/低速设备,输出的频率为1KHz |

| PB13 | OTG_HS_VBUS | VBUS引脚,通过寄存器选择外部VBUS供电还是内部VBUS供电 |

| PB12 | OTG_HS_ID | ID引脚,拉高/浮空为设备模式,拉低为主机模式 |

| PB14 | OTG_HS_DM | 差分信号负端 |

| PB15 | OTG_HS_DP | 差分信号正端 |

2.2.2 OTG_HS外部高速PHY ULPI接口讲解

此接口需要外挂一个USB的PHY芯片,这个芯片我们一般使用USB3318和USB3300等芯片,都是支持高速USB的,通过我们配置STM32F407的OTG HS寄存器,进一步在ULPI总线上下发命令来配置这类型的PHY芯片,他们支持的协议都是一样的,所以使用相同的STM32F407 OTG程序,能够完全驱动这两款PHY芯片,进而实现USB的通信。

| Pin脚 | 功能 | 备注 |

| PA5 | ULPI_CLK | MCU时钟输入,固定60M |

| PC0 | ULPI_STP | MCU在一个时钟周期内触发STP,以停止当前总线上的数据流。如果MCU正在向PHY发送数据,STP表示数据的最后一个字节在前一个周期中位于总线上。 |

| PC3 | ULPI_NXT | 限制数据。当MCU向PHY发送数据时,NXT指示当前字节何时已被PHY接受。MCU在下一个时钟周期中将下一个字节放置在数据总线上。 |

| PC2 | ULPI_DIR | 控制数据总线的方向。当PHY有数据要传输到链路时,它将DIR驱动到高电平以获得总线的所有权。当PHY没有要传输的数据时,它将DIR驱动为低电平,并监视总线以获取来自链路的命令。 |

| PA3 | ULPI_D0 | 双向数据总线 |

| PB0 | ULPI_D1 | 双向数据总线 |

| PB1 | ULPI_D2 | 双向数据总线 |

| PB10 | ULPI_D3 | 双向数据总线 |

| PB11 | ULPI_D4 | 双向数据总线 |

| PB12 | ULPI_D5 | 双向数据总线 |

| PB13 | ULPI_D6 | 双向数据总线 |

| PB5 | ULPI_D7 | 双向数据总线 |

其实以上MCU的引脚定义我们也不必太多关注,只需要把PHY芯片的对应引脚接入MCU对应的引脚即可。

3 STM32F407 OTG模块总结

STM32F407 有两个OTG模块,分别是OTG FS和OTG HS。

- OTG FS内置全速PHY芯片,通过引脚PA11和PA12进行通信

- OTG HS分为两个部分,一部分是内置全速PHY芯片,通过引脚PB14和PB15进行通信;另一部分是通过ULPI接口外挂一个高速PHY芯片(如USB3318或USB3300),通过高速芯片进行USB的通信

本文详细介绍了STM32F407单片机的两个OTG模块:STM32F407OTG_FS支持全速模式,而STM32F407OTG_HS则包括内置全速PHY和外部高速PHY通过ULPI接口。文章重点讲解了各模块的引脚定义和功能,以及高速PHY的外挂和配置方法。

本文详细介绍了STM32F407单片机的两个OTG模块:STM32F407OTG_FS支持全速模式,而STM32F407OTG_HS则包括内置全速PHY和外部高速PHY通过ULPI接口。文章重点讲解了各模块的引脚定义和功能,以及高速PHY的外挂和配置方法。

109

109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?