目录

链接快速定位

所有资料也可在顶部进行免费下载,也可通过评论留下邮箱进行发送

前沿

这里简单讲解一下关于安信可的ESP8266模块烧录AT固件的步骤与方法。

1 为什么要烧录固件

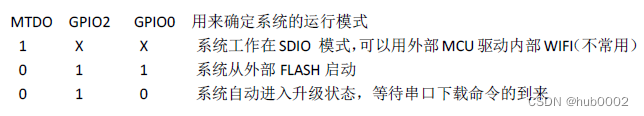

我们从淘宝买的ESP8266套件或者开发板上自带的ESP8266模块,出厂的时候,由设备厂商为我们烧录好了ESP8266的基础固件,烧写到外部FLASH(内部存储器是禁止用户使用的,类似于imx6ull等芯片,芯片厂商使用这部分区域来作为引导和初始化程序)。例如正点原子的ESP8266模块,他提供了自定义的AT命令固件,通过该固件能够快速实现对原子云的访问。

基础固件满足大部分的需求,但是如果我们想要进行特定的处理,比如快速实现MQTT通信,我们就能够自己编写固件库,进行烧录,当然也可以去安信可官网下载官方写好的固件,我们这里只简单讲解从安信可官网下载的固件怎么烧录到ESP8266模块上。

2 烧录固件

2.1 AT固件的准备

AT固件,就是执行AT命令所使用的固件,它由安信可公司提供,也可以自己开发,我们这里下载安信可公司的AT固件,下载链接:安信可固件,链接界面如下所示:

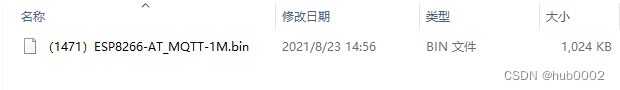

这里我们随便选择一种固件进行下载,注意自己外接的FLASH大小,我这里外接FLASH较小,所以选择的是1MByte的固件版本,如果外接FLASH大于等于4MByte。可以选择4MByte的固件,下载好的固件如下所示:

2.2 硬件准备

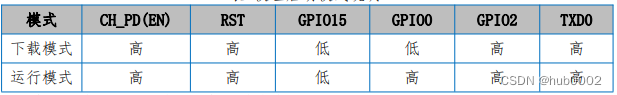

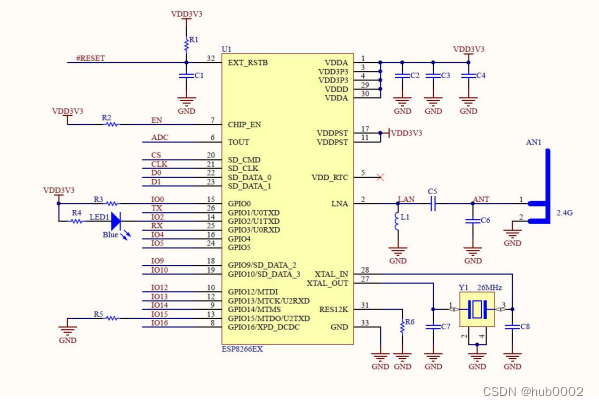

硬件可以通过网上购买ESP8266模块板,这里以安信可的ESP01S为例讲解(ESP01S规格书),参考下列接线,可以实现ESP8266的烧写和启动。

这里我们烧写FLASH(下载模式),所以我们需要把CH_PD(EN)、RST、GPIO15、GPIO0、GPIO2按下图拉低或拉高,因为CH_PD(EN)、RST、GPIO2默认拉高,GPIO15默认拉低,此时只需要在GPIO0外部引出的pin脚位置拉低即可进入下载模式,等待下载完成,再把GPIO0悬空,就会在外部的FLASH加载程序。

2.3 烧录工具的准备

烧录工具使用安信可官网的固件烧录工具--“ESP_DOWNLOAD_TOOL”,下载地址:烧录工具。

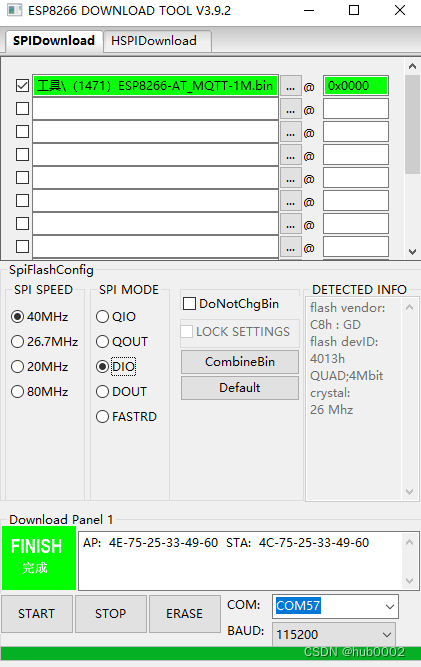

下载好软件,打开软件,选择“SPIDownload”界面,界面分为三块:

- Download Path Config

包含固件加载路径,固件下载地址,以16 进制格式填写,比如0x1000。

- SPI Flash Config

- SPI SPEED:SPI速度

- SPI MODE:SPI模式

- DETECTED INFO:自动检测到外挂的FLASH和晶振信息

- DoNotChgBin:若使能,则按照bin 文件原始内容烧录。若不使能,按照界面的SPI SPEED、SPI MODE 配置更新并烧

- Download Panel

包含开始烧录,停止烧录,擦除FLASH和串口选择。

按照上图配置,地址写0x0000,表示从外部FLASH的0地址开始烧录,配置好以后,点击START,等待烧录完成,如果烧录失败,建议降低串口波特率。

更多操作参考“doc”文件夹的操作手册。

接下来讲解esp8266的AT MQTT 命令的测试及云平台的简单搭建,敬请期待。。。

本文讲述了为何要烧录ESP8266固件,包括基础固件的限制和自定义AT固件的重要性。详细介绍了如何准备AT固件、硬件连接和使用安信可官方烧录工具进行烧录的过程。

本文讲述了为何要烧录ESP8266固件,包括基础固件的限制和自定义AT固件的重要性。详细介绍了如何准备AT固件、硬件连接和使用安信可官方烧录工具进行烧录的过程。

2705

2705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?