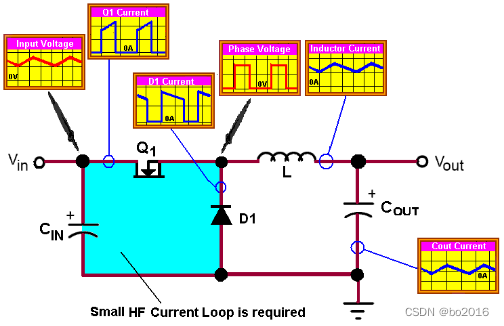

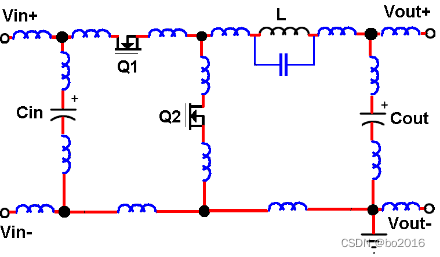

1.电源芯片的输入电容的GND在哪? 电源芯片的输出电容的GND在哪? 电源芯片的GND在哪?(非同步拓扑结构,肖特基GND即可为电源芯片的GND)

每个环路都是一个干扰发射源 尽可能缩小此两个环路!

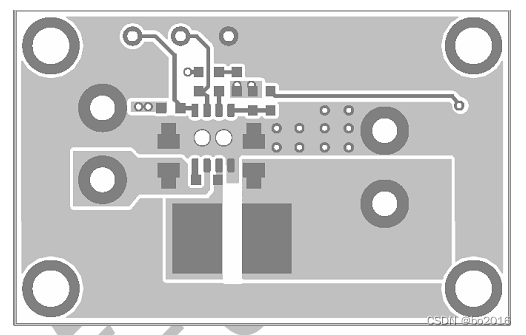

1. SW引脚到电感的导线,尽可能粗而短;

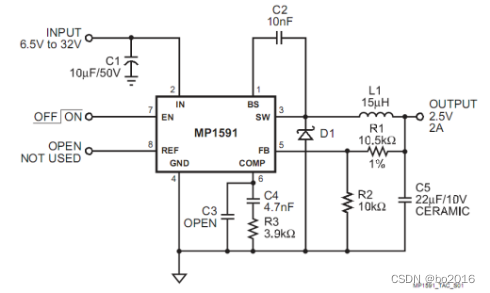

2. 输入电容、输出电容、电感、MOSFET、自举电容尽可能离IC近些,LAYOUT优先保证功率环路,再考虑信号部分;

3. 如果外围电路有肖特基,肖特基的两端要和相邻器件最 短链接,否则负向脉冲很大;

4.地层通过多个过孔接到器件侧的地上,以进一步减少敏感电路节点上的噪声干扰.

5.去藕电容应靠近VREF和VDD引脚.

EMI从哪里来?

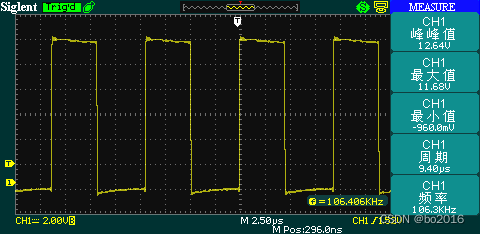

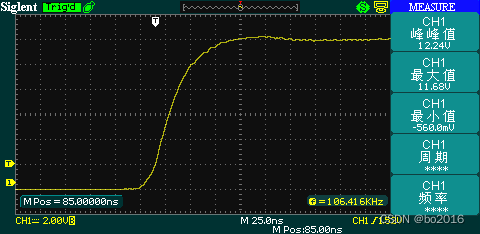

开关频率-EMI传导 开关频率越高,同样电感和电容,纹波越小; 开关频率越高,同样纹波所用电感越小。

开关速度-EMI辐射 开关速度越快,IC转换效率越高; 开关速度越慢,IC转换效率越低;

文章讨论了电源芯片在非同步拓扑结构中的GND位置,强调了减小干扰环路的重要性,如缩短SW引脚到电感的连接,优化元件布局,确保肖特基二极管的短链接,以及使用多个过孔降低噪声干扰。此外,还提到了开关频率和速度对EMI辐射及转换效率的影响。

文章讨论了电源芯片在非同步拓扑结构中的GND位置,强调了减小干扰环路的重要性,如缩短SW引脚到电感的连接,优化元件布局,确保肖特基二极管的短链接,以及使用多个过孔降低噪声干扰。此外,还提到了开关频率和速度对EMI辐射及转换效率的影响。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?