74HC138 是一款高速 CMOS 器件,属于3线转8线二进制译码器,可将3位二进制输入代码转换为 8 个互斥的低有效输出信号(23 等于 8)。它的工作电压范围一般为 2.0V 至 6.0V,具有较宽的电压适应范围,能够满足多种不同电源电压的应用场景。

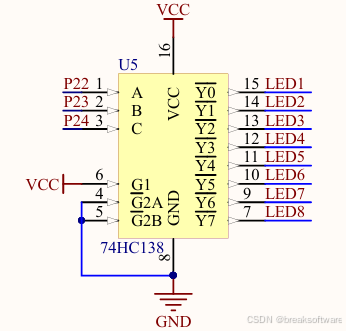

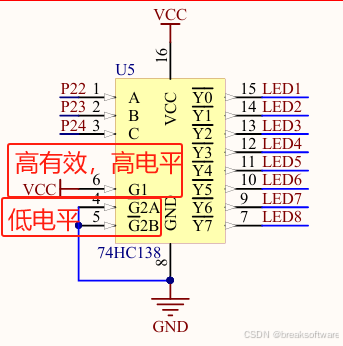

它的原理图如下:

下面我们会分开讲解各个模块

组成

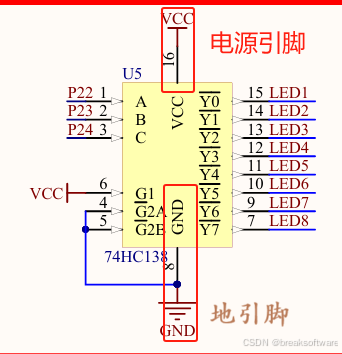

电源引脚和地引脚

VCC 为电源引脚,GND 为地引脚,为芯片提供电源和参考电位。

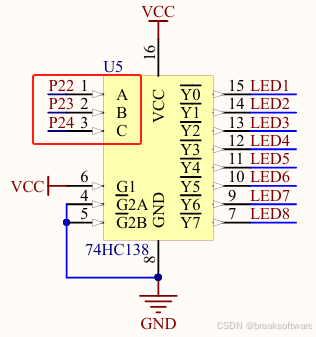

地址输入端

A、B 和 C 是 3 个地址输入端,用于输入 3 位二进制代码,通过这 3 个引脚的不同电平组合来选择对应的输出端。

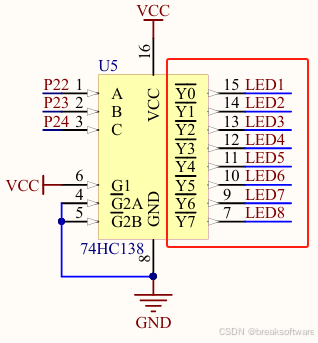

输出端

Y0 至 Y7 是 8 个输出端,当译码器使能且地址输入有效时,会根据地址输入的组合,在对应的输出端输出低电平,其余输出端则为高电平,实现 8 个互斥的低有效输出。即它将3位二进制数转换成8个数,区间是0~7。对应的引脚表达为低电平,其余表达为高电平。

使能输入端

共有 3 个使能输入端,分别是两个低有效使能端 G2A 和 G2B,以及一个高有效使能端 G1。

只有当 G2A 和 G2B置低且 G1 置高时,译码器才能正常工作,否则所有输出将保持为高电平。

原理

使能控制机制

使能输入端 G1、G2A、G2B起到控制译码器工作状态的作用。只有当 G2A=0、G2B=0 且 G1=1 时,译码器才会根据地址输入进行正常译码输出;否则,无论地址输入是什么,所有输出端 Y0 至 Y7 都将保持高电平,不进行译码工作。

在我们的电路板中,G1连接了正极,G2A和G2B连接了负极,就是让电路处于“使能”状态。

译码功能实现

根据 3 位地址输入端 A、B、C 的二进制编码组合,从 8 个输出端 Y0 至 Y7 中译出一个低电平输出,其余输出端为高电平。如当CBA=000 时,Y0 输出低电平,其他输出端为高电平;当 CBA=001 时,Y1 输出低电平,以此类推。

| C | B | A | 低电平位 |

|---|---|---|---|

| 0 | 0 | 0 | Y0 |

| 0 | 0 | 1 | Y1 |

| 0 | 1 | 0 | Y2 |

| 0 | 1 | 1 | Y3 |

| 1 | 0 | 0 | Y4 |

| 1 | 0 | 1 | Y5 |

| 1 | 1 | 0 | Y6 |

| 1 | 1 | 1 | Y7 |

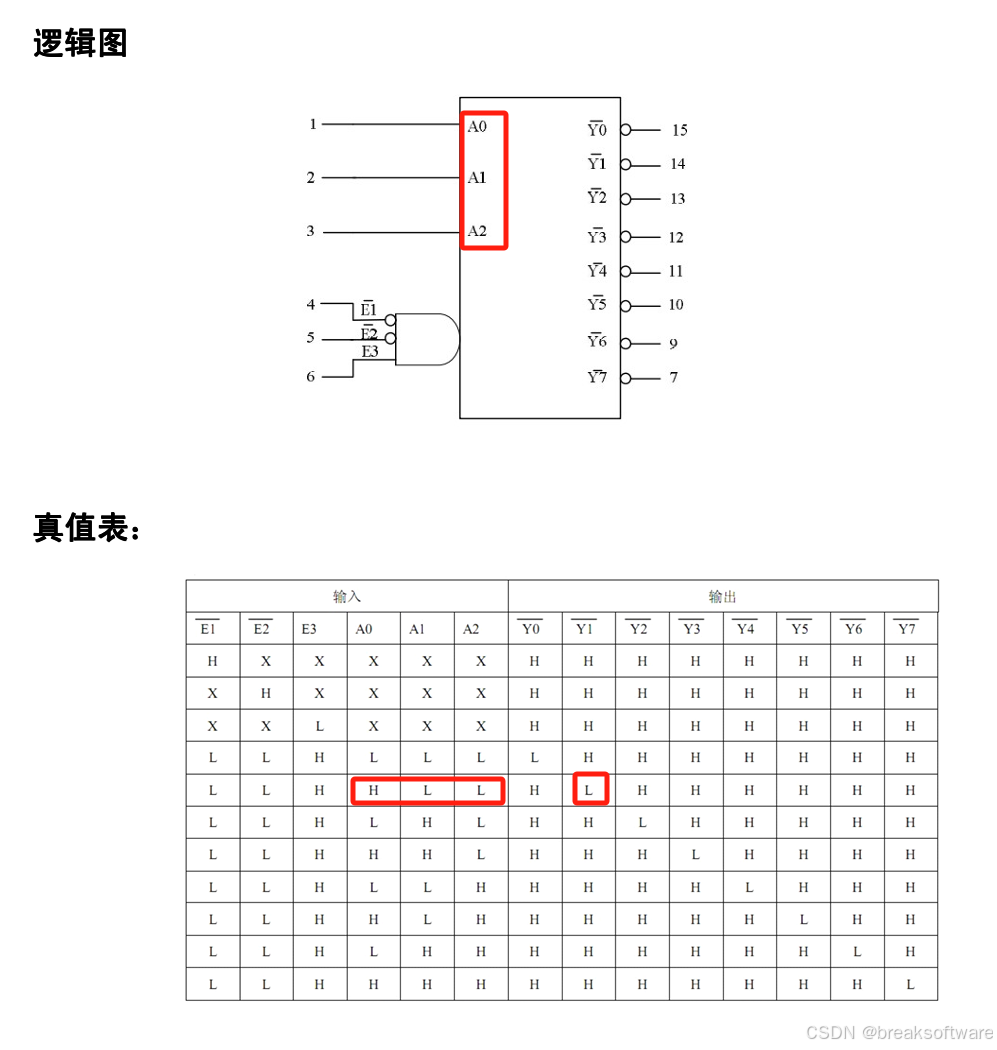

这儿需要注意的是,ABC这三个二进制数的组合应该是ABC、还是CBA。针对这个问题我们需要看74HC138的说明文档。

该文档中A0对应我们A、A1对应B、A2对应C。然后在真值表中,我们发现只有A0为高电平时,Y1处于低电平。所以其读取顺序是A2 A1 A0。

3366

3366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?