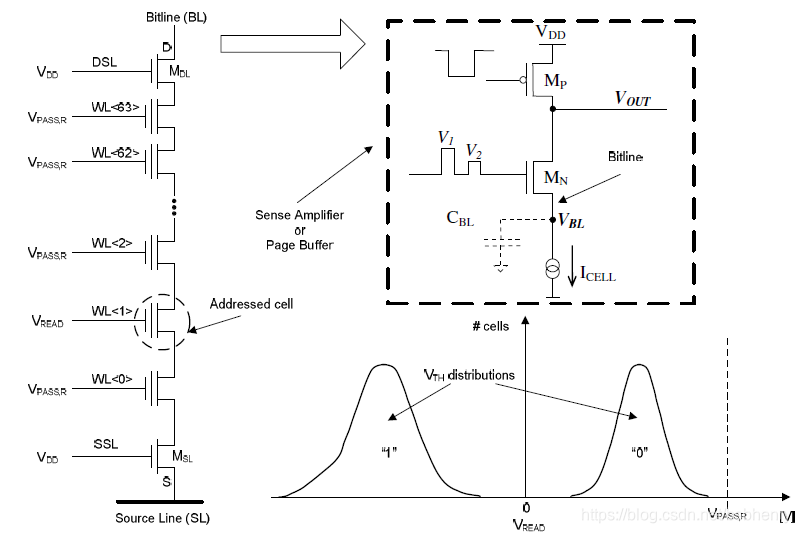

当对一个cell进行读操作时,对相应的wordline施加Vread电压,对其他wordline施加Vpass电压,如上图所示。状态为“0”的cell(被program的cell)的Vth均大于0,状态为“1”的cell(被erase的cell)的Vth均小于1,且所有cell的Vth有一个上限,所以对其他cell施加一个能确保导通的Vpass电压, 对要读数据的cell加一个电压值在两种状态之间的Vread,如果该cell为“0”,则不会形成source到drain端的通路,在bitline上检测不到电流,反之可以检测到电流。电流的检测是通过sense amplifier实现的。

以上过程只是针对SLC cell,对于MLC,TLC,具有更多的状态,读的过程也更加复杂。

参考

Inside NAND Flash Memories

3469

3469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?