1 Quartus Prime软件的基本操作

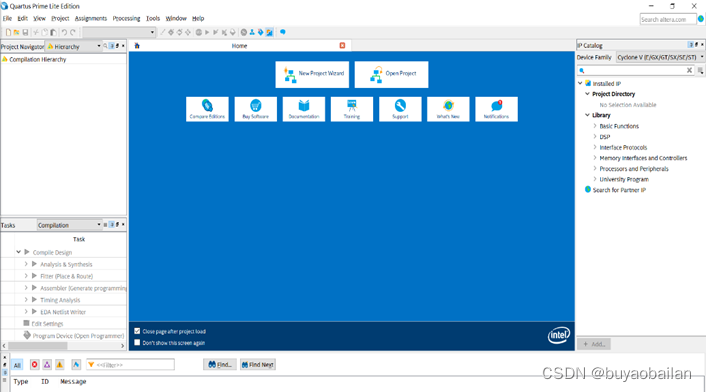

Quartus Prime(以下简称Quartus)软件操作界面如图1-1所示,其中中间的蓝色区域是工程工作区。工程工作区左侧从上到下分别是菜单栏、工具栏、资源管理窗口和编译状态显示窗口;工程工作区下侧是信息显示窗口;工程工作区右侧是IP模块管理窗口。

图1-1 Quartus软件开始界面

Quartus软件的操作流程基本可以概括为以下几个步骤。

首先应该点击工程工作区中的“New Project Wizard”,或者点击菜单栏中“File”下的“New”,弹出窗口后选择“New Quartus Prime Project”。完成上述操作后会弹出建立工程向导窗口。首先点击“Next”,然后再弹出的窗口中选择工程的保存位置,注意文件保存路径只能由英文、数字、下划线组成,且文件名只能以英文或下划线开头。下面两栏设定工程名和顶层设计文件名,一般和工程保存的文件夹名字保持一致。注意名字中不能出现非法字符,例如中文、空格等。点击“Next”后下一个界面可以选择工程是空工程还是带有模板的工程,默认选择空工程,选择好后点击“Next”。下一个界面的标题是Add files,即添加文件,在建立子模块工程时可以直接跳过这步,但是在建立总的集成工程时则需要将你需要的子模块文件添加进入。

下一个界面是Family,Device & Board Settings,在此界面中选择合适的器件,选择好后单击“Next”即可。接下来是仿真器的设置,可以在“simulation”一栏设置仿真器类型,生成测试文件的代码种类。以上操作完成后就完成了建立工程的设置,最后一个界面是用于检查设置,如果有问题可以点击“Back”回到之前的界面重新设置。

若要对子模块进行波形仿真,需要新建仿真文件夹,依次点击File,New,在弹出的任务栏中选择University Program VWF,点击OK,在Insert Node or Bus中点击Node Finder,选好合适的输入输出端口后,设置输入端口的输入值,最后在Simulation中选中Run Functional Simulation即可得到仿真波形。

2 利用硬件描述语言Verilog HDL编程设计

本次实训使用Verilog HDL语言编程,在新建工程后,再新建源代码编写文件夹。选中File,再选中new,在新弹出的窗口中选中Verilog HDL File,再电机OK,这样便可以编写Verilog源代码。本次实训中源代码的编写是以老师给出的VHDL代码为参考,经适当修改完成善后完成,因此要先看懂基本的VHDL代码。VHDL设计时的基本结构按照顺序分别是是库的引用、实体声明、结构体声明、结构的定义。除此之外,VHDL程序中的注释应该以“--”开头。

而使用Verilog语言时,以module <模块名>(端口列表)开头,通常的描述方式有行为描述和数据流语句,行为描述语句只能出现在initial、always两种语句内,该语言能够使用门和模块实例化语句在结构级进行结构描述,对高级编程语言结构,例如条件语句、情况语句和循环语句,语言中都可以使用。Verilog程序中的注释一般以“//”开头。

本次实训的Verilog源代码包含的子模块有:百分频电路,二十五分频电路,十分频电路,五分频电路,二-四分频电路,状态发生器电路,二进制计数器电路,主支干道同行时间设定模块,各种状态下倒计时计数器脉冲信号发生电路模块,倒计时计数器电路模块,信号灯控制电路模块,数码管闪烁显示控制电路模块,数码管显示数据选择电路模块,共阳数码管译码译码显示电路模块,显示控制电路模块,蜂鸣器报警电路模块,八进制计数器模块,动态扫描显示控制模块。

3 利用原理图进行顶层设计的操作流程

绘制原理图时需要从库中查找需要的元器件:在工作区双击左键,弹出窗口中“Name”一栏中可以搜索需要的元器件,需要注意的是Quartus软件中并不区分大小写。放置元器件后可以右键元器件对元器件进行翻转等操作。在原理图中进行连线也更加方便,直接将鼠标光标放置在元件引脚或节点上,鼠标光标会变为十字形,此时按住左键进行拖动即可进行布线。Quartus软件通过选中线路后直接键盘进行输入就可以进行网络标号。

在Quartus软件中可以自己添加子模块。方法是在建立工程时,在建立工程向导中的“Add Files”界面将需要的子模块设计文件添加到工程文件。之后在文件管理中选择添加的子模块设计文件单击右键,选择“Create Symbol File For Current File”,等待完成后回到原理图工作区添加元器件,可以看到窗口中出现了新的“Projects”文件夹,对应的子模块就在其中,可以将其添加至原理图。除此之外,工具栏中也有很多图标,以及一些快捷键都可以实现快捷操作,提高做作图效率。

绘制完原理图后需要对其进行保存、分析与综合等操作,并进行适当的调整与修改,最后保证其编译无误。

4 设计过程中的一些注意事项

在设计过程中的注意事项主要有:

- 工程文件命名只能由英文或下划线开头,路径中所有文件名只能由英文,数字,下划线组成。

- 一个工程内只能有一个顶层设计文件,如果多了会产生冲突。

- 绘制原理图时注意元件的标号不能重复。

- 利用Modelsim进行仿真时必须要有控制管脚或输入管脚。

- 注意原理图中输入输出端口命名正确。

- 利用波形编辑器进行仿真时,时间设置过长会导致仿真时间很长,注意设置合适的仿真时间。

- 绘制顶层文件时保证布局合理,排版工整,适当的对其端口,简化电路图。

3458

3458

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?