1,概述

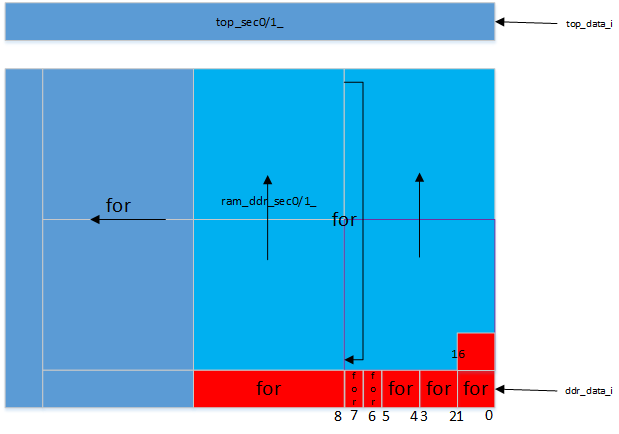

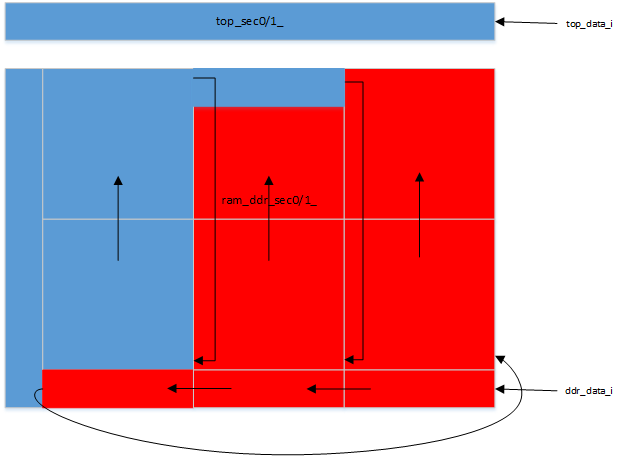

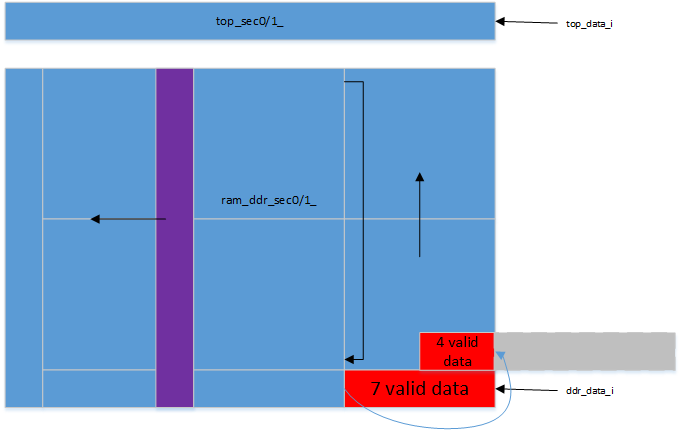

feature_in_reg_matrix分别接受三路数据信号,分别从top_row, left_ram和ddr存储中读取,由于三路数据信号在读取的时候有先后的连续性,所以对于读取的数据该放到缓冲区的那个位置可以考虑移位操作。在feature_in_reg_matrix中,我们把缓冲区分成两个部分,分别对应top row的缓冲区和bram_ddr_buffer部分的缓冲区,如下图所示:

在这个模块中我们主要要做两件事:

数据接收和移位

数据映射

2,数据接收过程

2.1,top row buffer数据接收

虽然top row buffer是22个数据宽度这么长,但是我们其实只需要里面的前16个数据,所以对于这前16个数据,我们可以一次性从ram中读取,而对应存储top row buffer的数据也是这样设计的。所以在top row buffer中不牵扯到数据移位的操作。

2.2,bram_ddr buffer数据接收和移位

对于这个缓冲区的数据接收和移位比较复杂,有以下很多种情况需要考虑:

数据来自block ram还是ddr?

对于第一次填充bram_ddr buffer缓冲区,整个bram_ddr buffer是一个连续ddr数据区域,所以可以进行连续的移位;但是对于同时从block ram和ddr读数据的情况,数据移位的方式会发生变化。如下图所示:

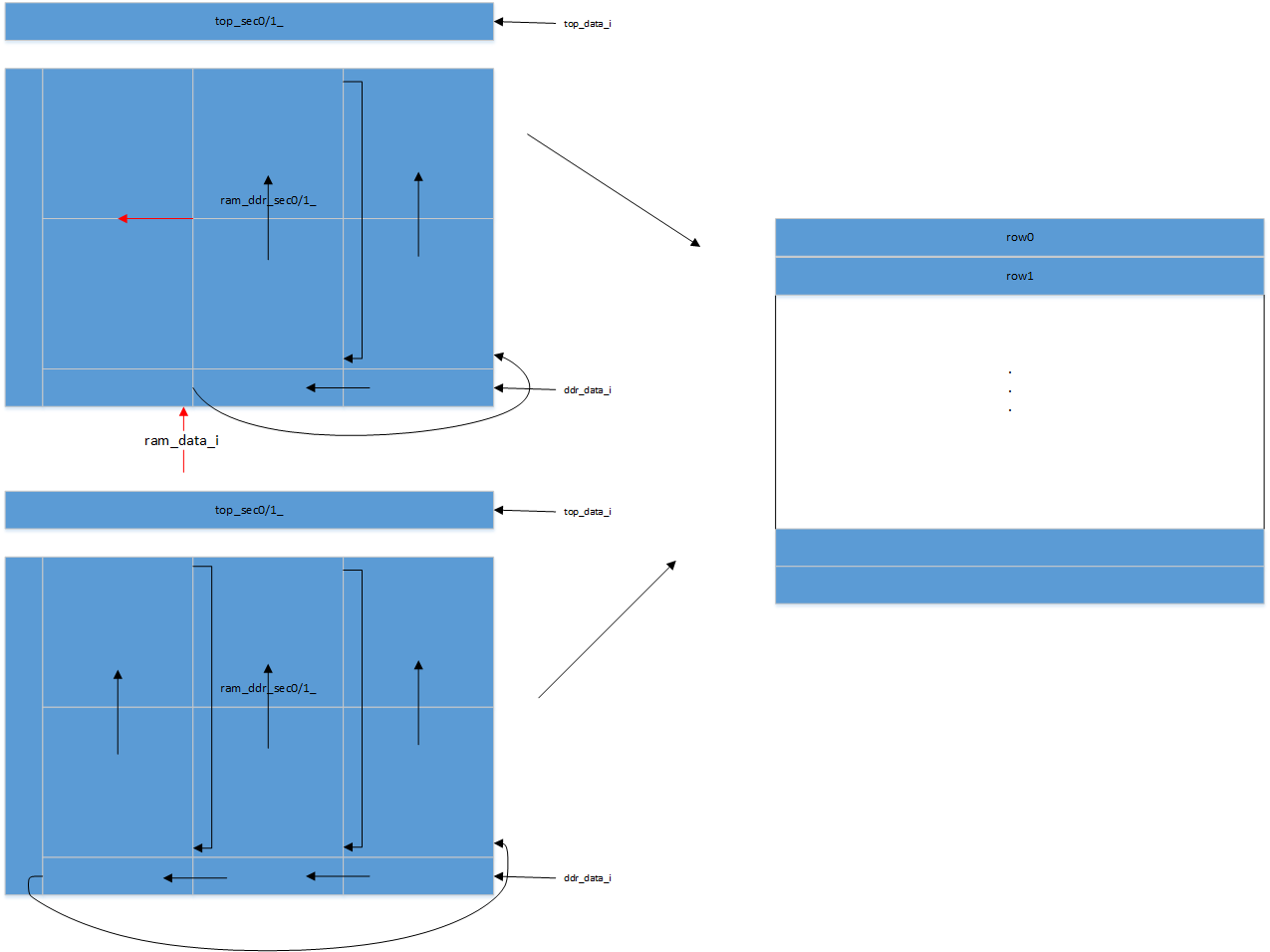

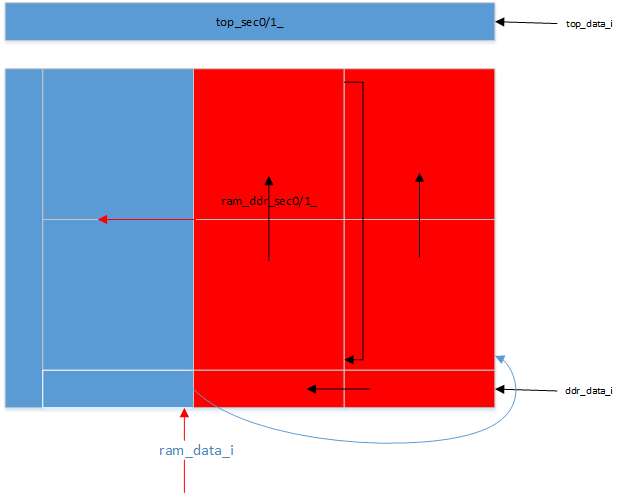

从上面的图中可以看出,对于这两种情况,bram_ddr buffer的后4x7x7+2x7个数据始终是来自ddr的,而之前的数据就要分情况考虑。但是对于后面4x7x7+2x7个数据,这两种情况下对应的数据排列也是不一样的,如下图所示:

从上面两个图看出,虽然后面4x7x7+2x7个数据是肯定来自ddr,但是对应的寄存器却有一点不一样,这没有问题,因为在后面会对寄存器进行统一映射。ddr一次移位多少数据?

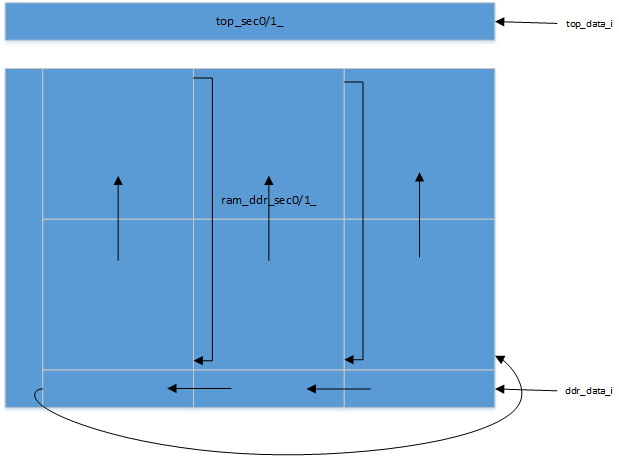

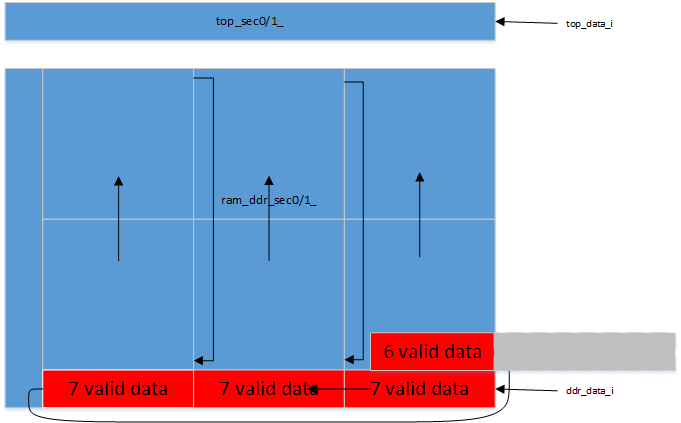

由于ddr中数据存储的基本单元是14x7,所以对于最后从ddr读取的512-bit长度的数据,可能只是某些数据是有效的,而且有效的位数一直在变换。- 对于第一次填充缓冲区,bram_ddr buffer的数据全部从ddr中读取,如下如所示:

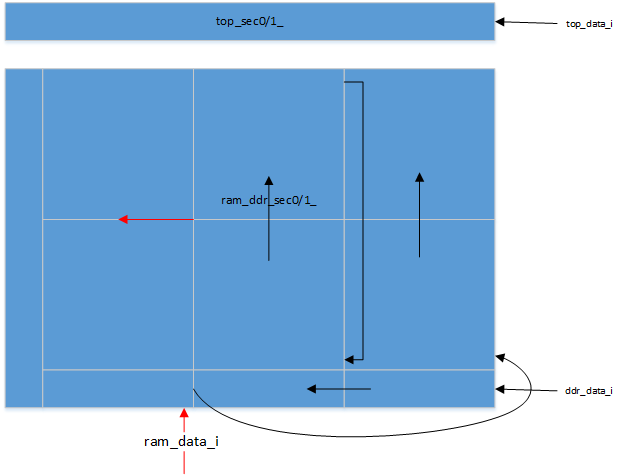

由图中可以看出在读取6x7x7的最后几个数据的时候,512-bit数据只有6个数据是有效的;在读取最下面一行的时候,只有7个数据是有效的。 - 在同时从ddr和ram中读取数据的时候,也会出现只是部分数据有效的情况,这时

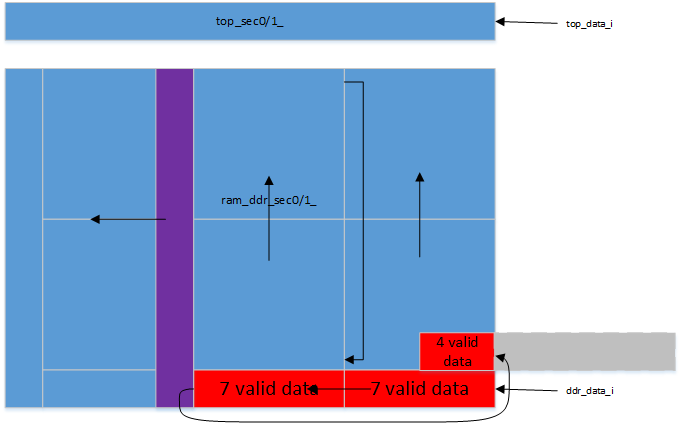

14x7x2的最后一个512-bit的有效数据为4个,如下图所示:

- 对于读取feature map中的最后一列

14x7数据同样会出现只有部分数据有效的情况,这时最后14x7的最后一个512-bit的有效数据为2个,如下图所示:

- 对于第一次填充缓冲区,bram_ddr buffer的数据全部从ddr中读取,如下如所示:

从以上几种情况可以知道,对于bram_ddr buffer的数据移位一下面几种:

一次移位16个数据

一次移位7个数据

一次移位6个数据

一次移位4个数据

一次移位2个数据

由于verilog语言的特性,我们不能把移位多少个数据设置成一个变量,而只能以case...endcase语句的形式实现。

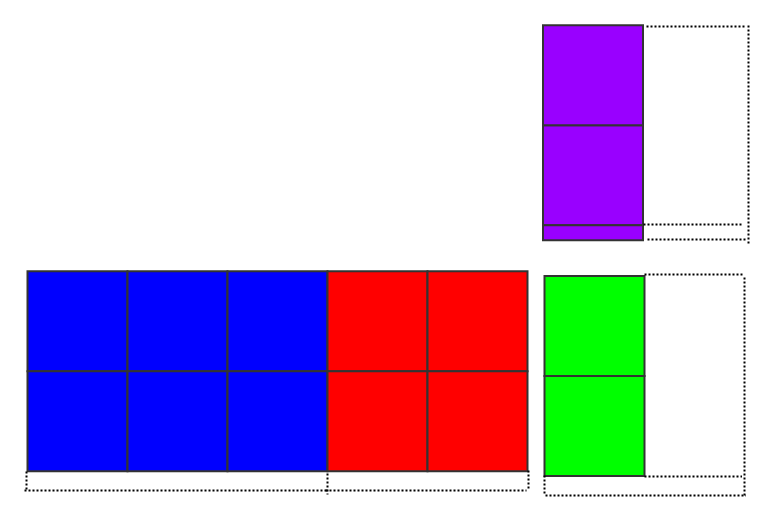

对于每个数据的移位,我们肯定不可能在写代码的时候,逐像素地进行实现,必须使用for...end循环语句实现,但是这里我们把for..end语句分成7个部分,如下如所示:

在每一个for循环之内我们决定是接收来自read_op的数据,还是进行数据移位,移位多少。

- ddr移位跨度的补充

上面的情况只是针对输入数据的有效个数来确定移位多少个数据,但是还有一种情况就是当读到feature map的最后一列或者最后一行,或者feature的最后一个14x7的时候,即使最后一个数据的有效数据是2个,移位的跨度这个时候却不是两个,而是更大,如下图所示:

在last column的时候,由于虚线框内的14x7数据不存在,所以下一次读取的数据肯定是下面紫色的一行,按照上面所描述的普通情况,这个时候数据应该移位先移位2个,在移位7个,但是由于左边数据存在,那么在接受到下面紫色7个数据的时候,数据应该移位7+2x7x7。在移位完成之后,由于下方虚线框表示的数据也不存在,所以还要另外移位7个数据长度。

在读取last row的时候,在深蓝色的6x7x7数据全部读取完毕的时候,下面虚线框表示的数据由于不存在,所以也不需要读,但是此时数据由于没有移位完毕,并没有到应该到的位置上,所以这个时候要两外移位3x7个数据长度。对于红色的部分,在读完4x7x7个数据的时候,红色下面虚线框表示数据不存在,所以不需要读,此时需要额外移动2x7个数据长度。

在读取feature map最后一个数据的时候,在读取完绿色部分的时候,左侧的2x7x7和下面的2x7个数据也不存在,这个时候也要另外移位2x7x7+2x7个数据长度。

对于上述缓冲区数据额外的移位可能会出现一种问题,就是哪些数据应该进行额外移位,哪些数据不需要,如果对不需要额外移位的数据进行移位,就会出现数据错误的问题。所以这里要进行判断。

3,数据映射过程

在上述所描述的数据接收和移位的过程中,出现了一种情况就是,对于不同的数据接收情况(从ddr,从ram),寄存器之间的排列顺序也是不一样,这样数据排列顺序的变化就给将来卷积操作的数据选择带来困难。再有就是上面的数据事实上是以14x7为单位存储的,但是对于卷积操作的数据选择来说,还是按行存储比较方便,所以就需要一种数据的映射,类似于虚拟内存。

对于不同的数据接收情况,映射的情况也是不一样的,如下图所示:

这样进行统一的映射很方便与将来卷积核的数据选择。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?