目录

FIFO用作数据流缓冲块,一般用在写快读慢时。FIFO的深度一般为2^N,要符合格雷码转换规则。考虑最坏的情况:写速率最大,读速率最小的时候,就是需要存储数据最多的时候,也就是FIFO深度的下限值。

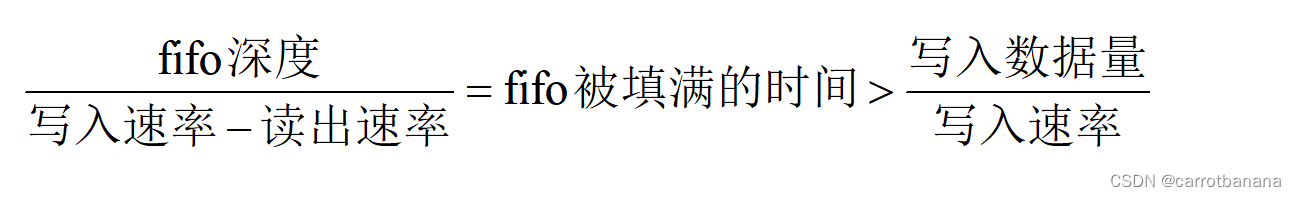

最小深度计算原理:

确保FIFO写数据的时候不发生溢出,FIFO读数据的时候不发生读空。

例题:A/D采样率50MHz,dsp读A/D读的速率40MHz,要不丢失地将10万个采样数据送入DSP,在A/D在和DSP之间至少加多大容量(深度)的FIFO才行?

解:代入公式:fifo深度/((50-40)*10^6)>10^5/40*10^6

所以fifo最小深度为2*10^4。

读写同时进行:最小深度计算公式:

fifo_depth = burst_length - burst_length * X/Y * r_clk/w_clk

其中:burst_length为最大连续写入长度

X/Y:读取速度。读时钟下,每Y个时钟周期,会有X个数据被读出

r_clk/w_clk:读时钟频率与写时钟频率的比值,在同步fifo中,该值为1.

注意:假如读写不同时进行,则FIFO最小深度为写数据的最大突发个数。

有了最小深度计算公式后,上题便可以快速得出答案;

例题:A/D采样率50MHz,dsp读A/D读的速率40MHz,要不丢失地将10万个采样数据送入DSP,在A/D在和DSP之间至少加多大容量(深度)的FIFO才行?

解:burst_length=10^5

X/Y没有给出,因此默认为1

r_clk/w_clk=4/5

fifo_depth= 10^5-10^5*(4/5)=2*10^4

最小深度计算公式应用:

(1)同步FIFO最小计算

设计一个同步fifo,读写时钟相同,其中在写入时每100个时钟周期会写10个,具体哪个时刻写入不确定,在读出侧每10个cycle会读1个,计算最小深度?

解:

考虑背靠背传输,在两百个时钟周期中连续写20个数据,所以最大突发写长度 Burst_length= 20;

同步FIFO中,读时钟等于写时钟,rd_clk = wr_clk;

每10个时钟周期读取1个数据,所以X/Y = 1/10=0.1;

所以:

FIFO_Depth >= Burst_length -Burst_length* (rd_clk/ wr_clk)*(X/Y)

= 20 – 20*1*0.1

= 18

(2)异步FIFO最小深度的计算

异步FIFO,w_clk=200MHz,r_clk=100MHz。其中在写入时每100个时钟周期会写40个,在读出侧每10个cycle会读8个,计算最小深度?

解:

考虑背靠背传输,在两百个时钟周期中连续写80个数据,所以最大突发写长度 Burst_length= 80;

异步FIFO中,rd_clk /wr_clk=1/2;

每10个时钟周期读取8个数据,所以X/Y = 8/10=0.8;

所以:

FIFO_Depth >= Burst_length -Burst_length* (rd_clk/ wr_clk)*(X/Y)

= 80 – 80*1/2*0.8

= 48

(3) 笔试题

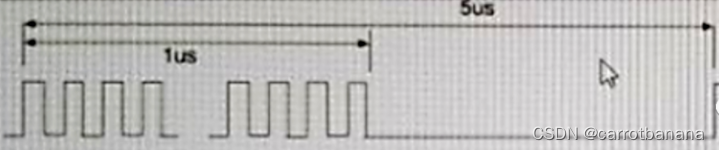

ModuleA/ModuleB用的是同个Clock, Clock频率80MHz。ModuleA和ModuleB同时启动,ModuleA产生如下周期性的burst数据给ModuleB,一共产生8次burst. burst rate : 1280Mbit/s,burst持续时间1us。burst内部速率均匀,burst周期5us,余下的4us内没有数据。

ModuleB收到启动信号后,需要花10us做初始化,所以先把module A的数据缓存在ModuleB内部的同步FIFO中,同步FIFO位宽32bits,初始化结束后,ModuleB以640 Mbit/s的均匀速度从FIFO中读取数据。在满足功能需求的前提下,为了节省电路面积,要求FIFO size越小越好,以下四个选项的FIFO深度,选项()的FIFO深度符合要求:

A: 128 B: 64 C: 96 D: 160

答案:A

解析:

考虑最大数据情况,在ModuleB启动的10us内,ModuleA一直在传输数据,一共2us有效数据,需要存储 1280Mbit/s * 2us = 2560bit;在第11us,ModuleA传输数据 1280Mbit/s * 1us = 1280bit,ModuleB读取 640 Mbit/s * 1us = 640 bit,需要存储 1280 - 640 = 640 bit,此时共需存储 2560 + 640 = 3200 bit。

考虑整个读写,前15us共写入 3 * 1280=3840,读取 5*640=3200,只需要存储640,目前设置存储3200,所以满足要求。

综合考虑,最大需要存3200bit,深度需要 3200 / 32 = 100,由于FIFO一般为2^N,所以选A的128较为合适。

参考:

FPGA笔试面试题之FIFO深度计算【字节跳动】【大疆】【简便计算公式】

1385

1385

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?