生成器件镜像后

,

下一步是将其下载到目标器件。

Vivado IDE

具有内置原生的系统内器件编程功能用于执行此操作。 Vivado Design Suite 和

Vivado Lab Edition

都包含相应的功能

,

支持您连接到包含

1

个或多个

FPGA

或

ACAP

的硬 件,

以便对这些器件进行编程并与之交互。要连接到硬件

,

可通过

Vivado Lab Edition

或

Vivado Design Suite

图形用 户界面,

也可使用

Tcl

命令。无论采用何种方法

,

连接到硬件并对目标器件执行编程的步骤都相同

:

1.

打开硬件管理器

(Hardware Manager)

。

2.

打开主机上运行的硬件服务器所管理的硬件目标。

3.

将器件镜像与相应的器件相关联。

4.

将器件镜像编程或下载到硬件器件中。

打开硬件管理器

打开硬件管理器是对硬件中的设计进行编程和

/

或调试的第一步。要打开硬件管理器

,

请执行以下操作之一

:

• 如果工程已打开

,

请单击

Vivado Flow Navigator

的“编程和调试

(Program and Debug)

”部分中的“

Open Hardware Manager”按钮。

• 选择“

Flow

” → “

Open Hardware Manager

”。

• 在

Tcl

控制台窗口中

,

运行

open_hw_manager

命令

打开硬件目标连接

打开硬件目标

(

如包含

JTAG

链的硬件开发板

,

该链中包含一个或多个

FPGA

或

ACAP

)

后

,

下一步是连接到硬件服务 器,

它负责管理与硬件目标间的连接。有

3

种方法可用

:

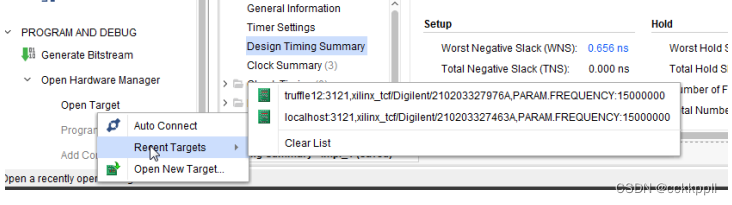

• 在

Vivado Flow Navigator

的“编程和调试

(Program and Debug)

”部分中的“硬件管理器

(Hardware Manager)

” 下,

使用“

Open Target selection

”打开新的硬件目标或最近的硬件目标

(

如下图所示

)

。

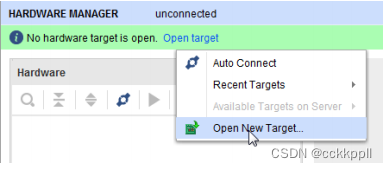

• 使用“

Hardware Manager

”窗口顶部的绿色用户辅助功能栏上的“

Open Target

” → “

Recent targets

”或“

Open Target” → “

Open New Target

”选项即可分别打开最近的硬件目标或新的硬件目标

(

如下图所示

)

。

使用

Tcl

命令打开到硬件目标的连接。

提示

:

“自动连接

(Auto Connect)

”选项可用于自动连接至本地硬件目标。

使用

hw_server

连接至硬件目标

连接至本地机器上的目标时

,

Vivado

会自动启动

hw_server

。但您也可以在本地机器或远程机器上手动启动 hw_server。例如

,

在

Windows

平台上安装的完整版

Vivado

中

,

在

cmd

命令提示符处运行以下命令

:

C:\Xilinx\Vivado\<Vivado_version>\bin\hw_server.bat

如果当前在

Windows

平台上使用的是

Hardware Server (Standalone)

安装

,

那么请在

cmd

命令提示符处运行以下命 令:

c:\Xilinx\HWSRVR\<Vivado_version>\bin\hw_server.bat

请遵循下一章节中的步骤

,

使用此代理打开到新硬件目标的连接。

要获取兼容

JTAG

下载线缆和器件列表

,

请参阅

附录

D: hw_server

支持的

JTAG

线缆和器件

。

如需了解有关使用

SmartLynq

数据线缆的更多信息

,

请参阅《

SmartLynq

数据电缆用户指南》

(

UG1258

)

。

重要提示

!

如果

Vivado Hardware Manager

已连接至

hw_server

并且

hw_server

已停止

,

那么

,

Hardware Manager 会自动检测到此状况

,

并断开与服务器的连接。

打开新硬件目标

“打开新硬件目标

(Open New Hardware Target)

”

Wizard

提供了一种交互式方法

,

供您用于连接到硬件服务器和目 标。此向导流程包含以下步骤:

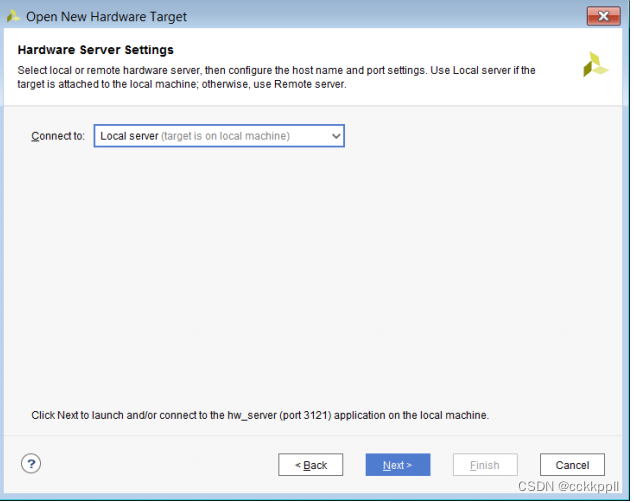

1.

根据您的硬件目标连接到的机器

,

选中本地服务器或远程服务器

:

• 本地服务器

(Local server)

:

如果您的硬件目标连接到运行

Vivado Lab Edition

或

Vivado IDE

的机器

,

请使用此 设置(

请参阅下图

)

。

Vivado

软件会在本地机器上自动启动

Vivado Hardware Server (hw_server)

应用。

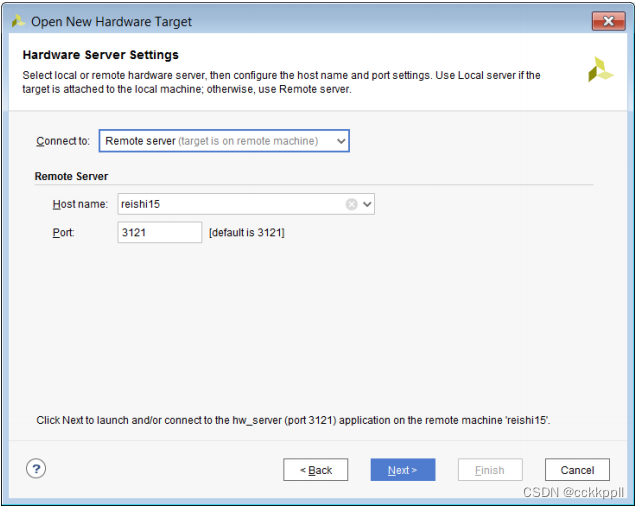

• 远程服务器

(Remote server)

:

如果您的硬件目标连接到的机器与运行

Vivado Lab Edition

或

Vivado IDE

的机器 不同,

请使用此设置。指定远程机器的主机名或

IP

地址以及该机器上运行的

Hardware Server (hw_server)

应 用的端口号(

请参阅下图

)

。请参阅“连接到实验室机器上运行的远程

hw_server

”以获取有关远程调试的更 多信息。

重要提示

!

使用远程服务器时

,

您需要手动启动

Vivado Hardware Server (

hw_server

)

应用

,

启动的应用 版本与您将用于连接到硬件服务器的 Vivado

软件版本相同。

提示

:

如果只需远程连接到实验室机器

,

则无需在该远程机器上安装完整的

Vivado Design Suite

。可改为 在该远程机器上安装轻量级 Vivado Hardware Server (Standalone)

工具。

2.

从硬件服务器管理的目标列表中选择相应的硬件目标。请注意

,

选择目标时

,

您会看到该硬件目标上可用的各种硬 件器件。

重要提示

!

如果在

JTAG

链中存在第三方器件

,

请使用

赛灵思答复记录

61312

中的指示信息来为未知器件 添加 IDCODE

、

IR Length

和名称。

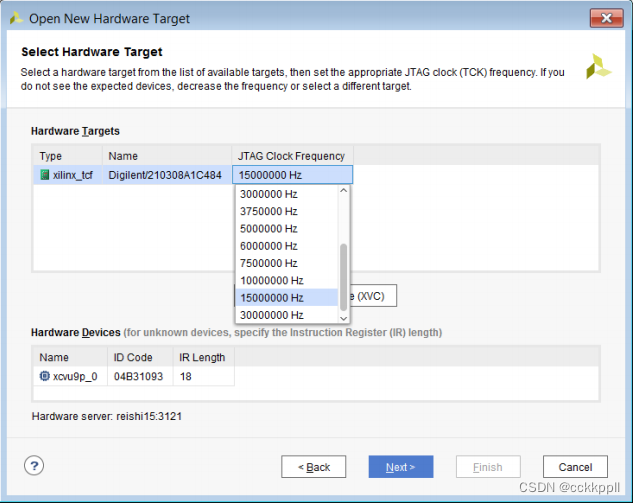

对硬件目标进行故障排除

尝试连接至硬件目标时可能会遇到问题。以下是常见问题以及有关解决此类问题的建议

:

• 如果您无法正确识别目标上的硬件器件

,

这可能表示您的硬件无法按默认目标频率运行。您可调整硬件目标或电缆 的 TCK

管脚频率

(

请参阅上图

)

。请注意

,

每一种类型的硬件目标都可能包含不同属性。请参阅每个硬件目标的文 档,

以了解有关这些属性的更多信息。

• 当

Vivado

硬件服务器尝试自动判定

JTAG

链中所有器件的指令寄存器

(IR)

长度时

,

在极为罕见的情况下

,

它可能无 法正确判定其长度。您应检查每个未知器件的 IR

长度

,

确保其正确无误。如需指定

IR

长度

,

可在“打开新硬件目 标 (Open New Hardware Target)

”

Wizard

的“硬件器件

(Hardware Devices)

”表中直接指定其长度

(

请参阅“打开 新硬件目标”)

。

相关信息

打开新硬件目标

打开最近的硬件目标

“打开最近的硬件目标

(Open New Hardware Target)

”

Wizard

同样可用于填充先前已连接的硬件目标列表。除使用此 向导连接到硬件目标外,

您也可以通过选中“硬件管理器

(Hardware Manager)

”窗口中的“打开最近的目标链路 (Open recent target link)”

,

然后选中列表中任一最近连接的硬件服务器

/

目标组合来重新打开到先前已连接的硬件目 标的连接。您还可通过 Vivado Flow Navigator

的“编程和调试

(Program and Debug)

”部分中的“

Hardware Manager”下的“打开目标

(Open Target)

”选项来访问此最近使用的目标列表。

使用

Tcl

命令打开硬件目标

您也可以使用

Tcl

命令来连接至硬件服务器

/

目标组合。例如

,

要连接至由

localhost 3121

上运行的

hw_server

所管理 的 digilent_plugin

目标

(

序列号

210203339395A

),

请使用以下

Tcl

命令

:

connect_hw_server -url localhost:3121

current_hw_target [get_hw_targets */xilinx_tcf/Digilent/210203339395A]

set_property PARAM.FREQUENCY 15000000 [get_hw_targets \

*/xilinx_tcf/Digilent/210203339395A]

open_hw_target

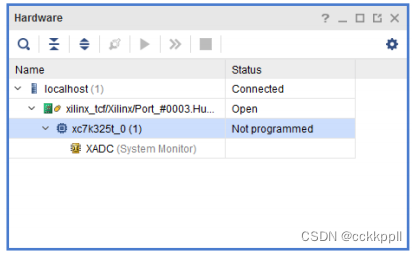

完成打开到硬件目标的连接后

,

“硬件

(Hardware)

”窗口中将显示打开的目标的硬件服务器、硬件目标和各种硬件器 件(

请参阅下图

)

。

将编程文件与硬件器件相关联

连接到硬件目标后

,

在进行器件编程之前

,

需将比特流数据编程文件与该器件相关联。在“硬件

(Hardware)

”窗口中 选择硬件器件,

确保“属性

(Properties)

”窗口中的“编程文件

(Programming file)

”属性设置为相应的编程文件。

注释

:

为方便起见

,

Vivado IDE

自动使用当前实现的设计的编程文件作为打开的硬件目标中的首个匹配器件的 “Programming File

”属性的值。仅当使用

Vivado IDE

工程模式时

,

此功能才可用。使用

Vivado IDE

非工程模式时

, 您需要手动设置该属性。 您也可以使用 set_property

Tcl

命令来设置硬件器件的

PROGRAM.FILE

属性

:

set_property PROGRAM.FILE {C:/<path_to_programming_file>} [lindex

[get_hw_devices] 0]

1198

1198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?