来源:tomshardware

编译:EETOP

世界上最先进的半导体研究机构 Imec 最近在比利时安特卫普举行的未来峰会上分享了其亚1nm和晶体管路线图。

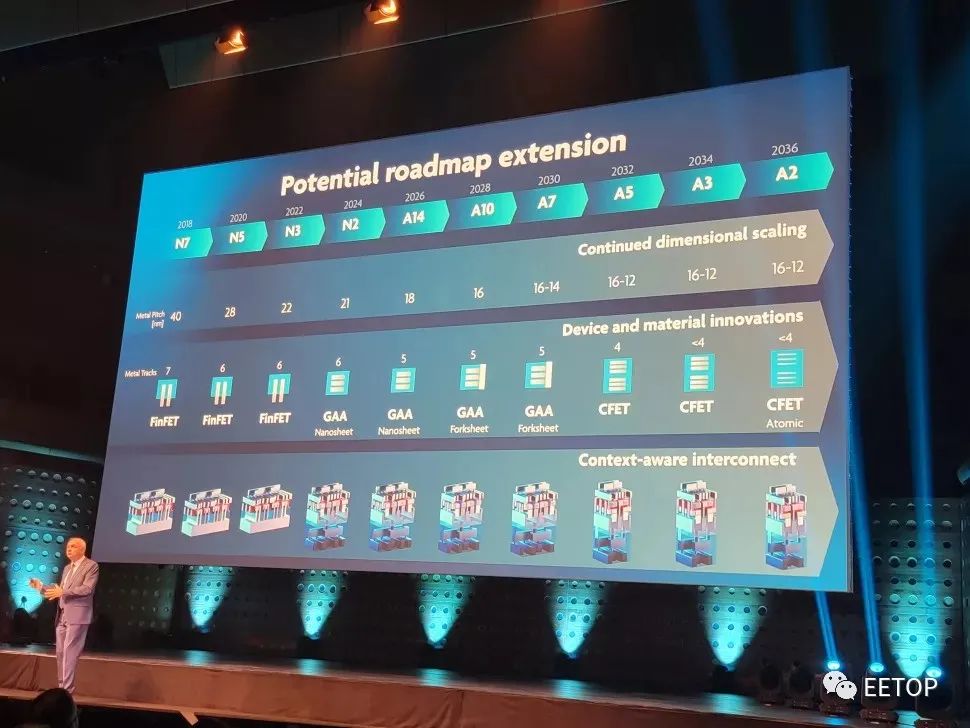

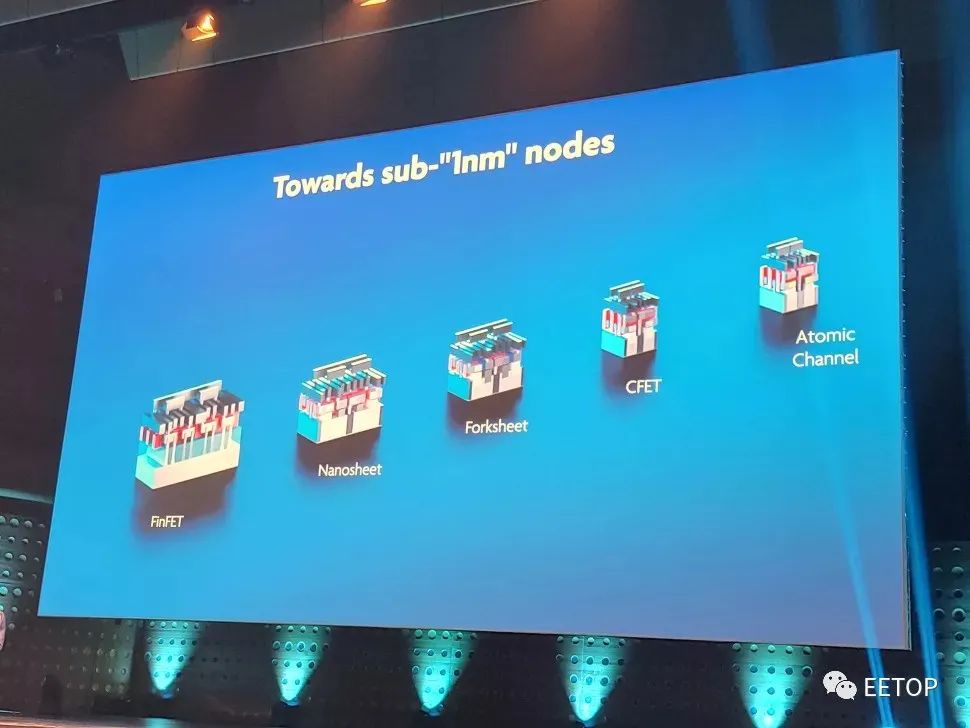

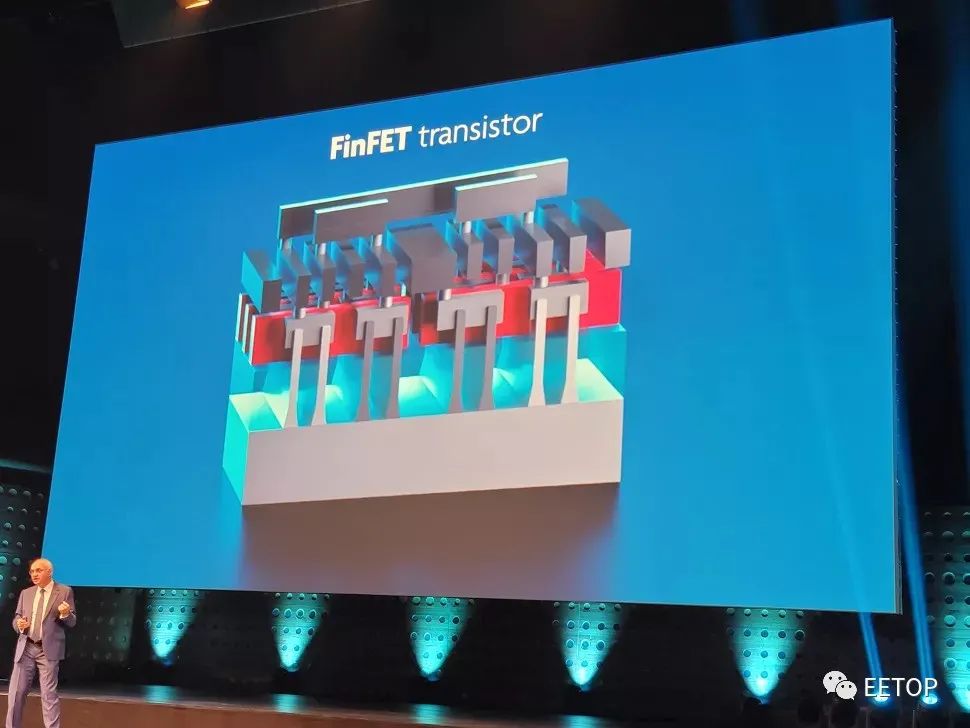

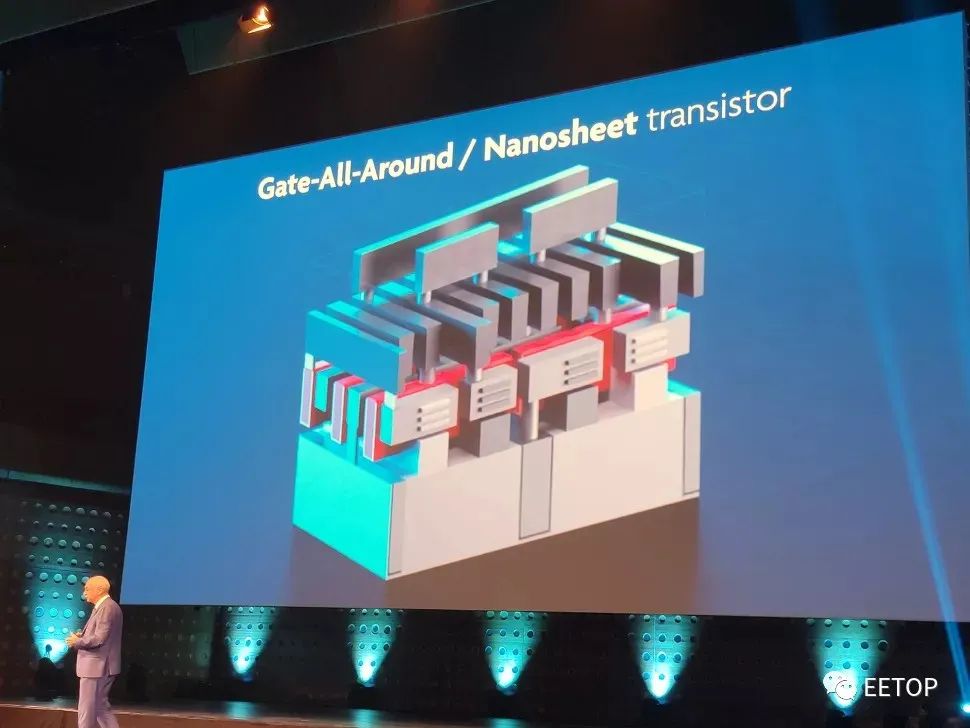

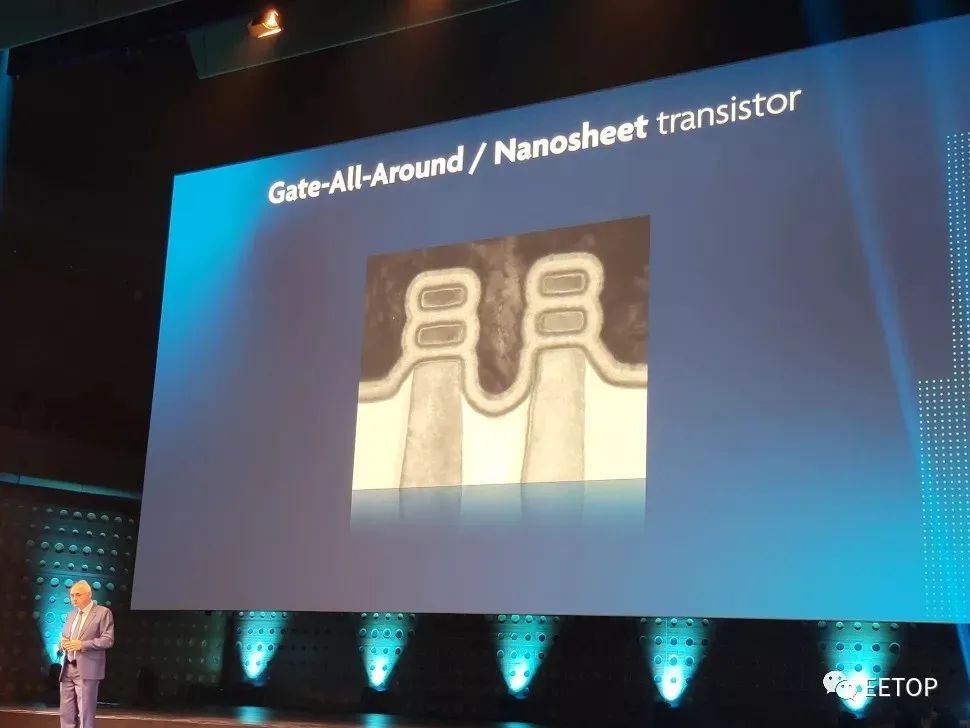

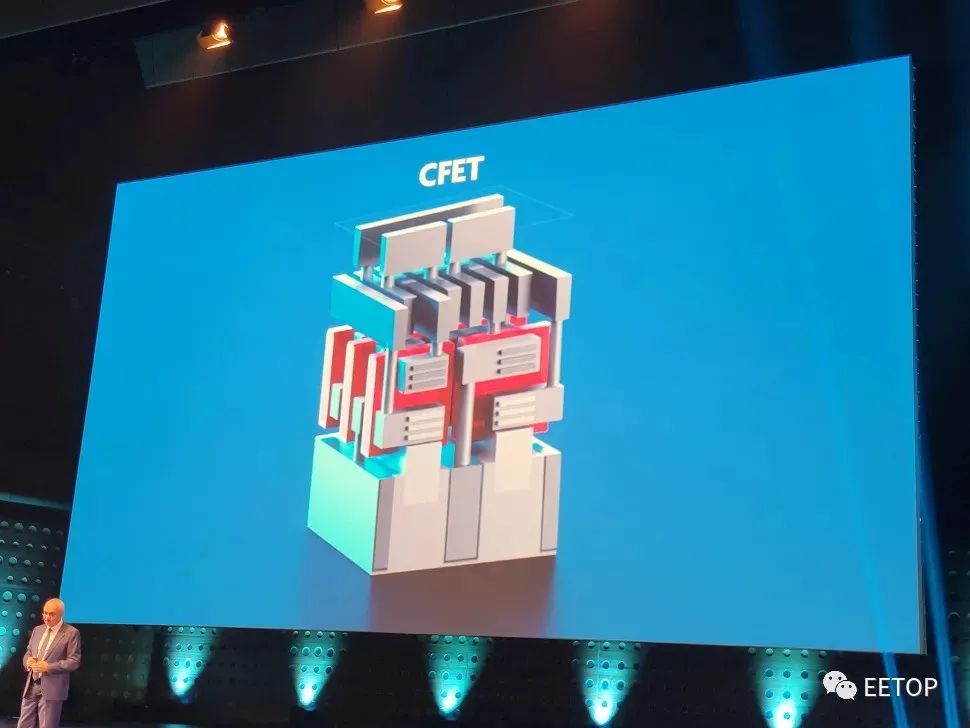

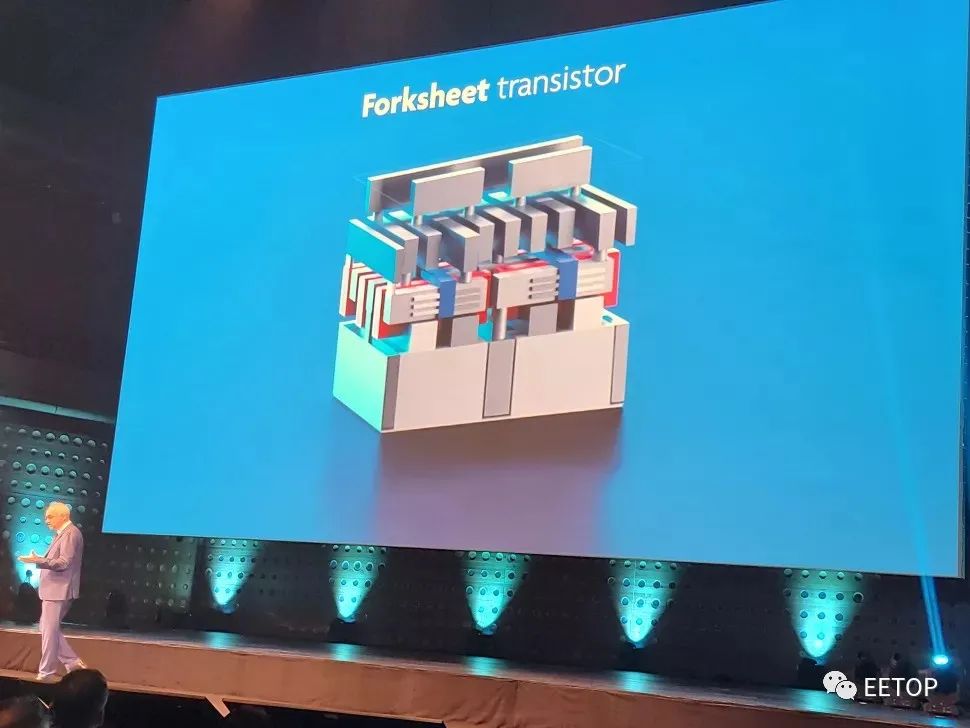

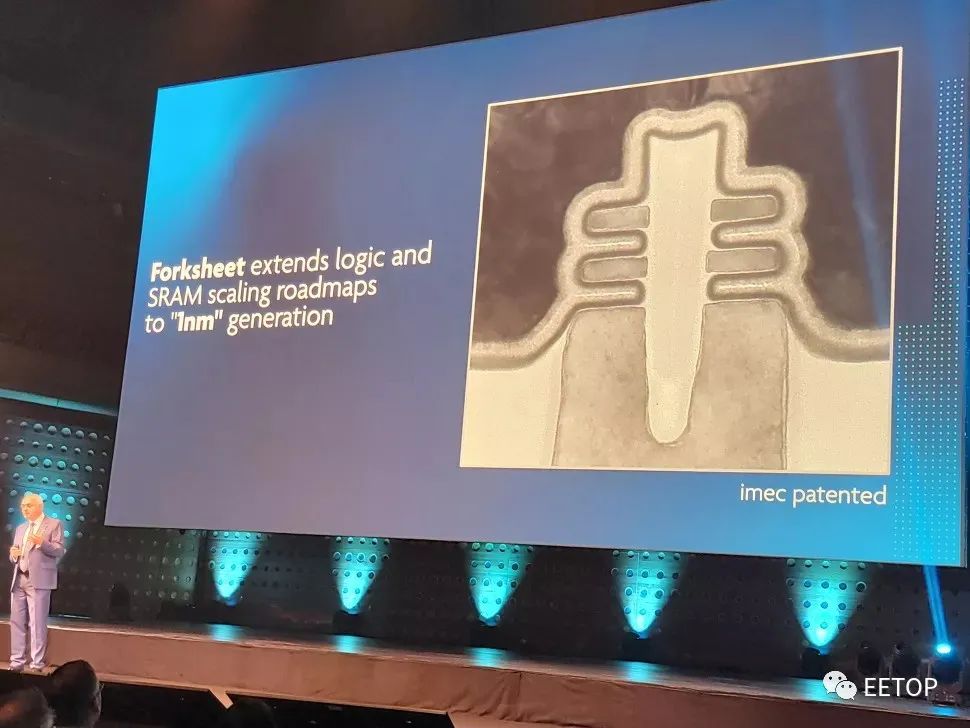

该路线图让我们大致了解了到 2036 年Imec将在其实验室与台积电、英特尔、三星和 ASML 等行业巨头合作研发的下一个主要工艺节点和晶体管架构的时间表。该路线图包括突破性晶体管设计,从持续到 3nm 的标准 FinFET 晶体管发展到新的 Gate AllAround (GAA) 纳米片和叉片设计,分别为 2nm 和 A7(7 埃),然后是突破性设计,如 CFET 和原子A5 和 A2 的通道。提醒一下,十埃等于 1nm,因此 Imec 的路线图包含亚1nm工艺节点。

如果你不是半导体领域的,您以前可能没有听说过比利时校际微电子中心(imec),但它与台积电和 EUV 光刻机制造商 ASML 等知名公司并列为世界上最重要的半导体公司之一。虽然专注于半导体研究的imec并没有大张旗鼓,但它是半导体行业的安静基石,将英特尔、台积电和三星等激烈的竞争对手与ASML和应用材料等芯片工具制造商聚集在一起。更不要说把同样重要的半导体软件设计公司(EDA),比如Cadence和Synopsys,牵手在一个非竞争的环境中,这种合作使两家公司能够共同定义下一代工具和软件,他们将用于设计和制造为世界提供动力的芯片。

面对设计芯片和制造它们的工具的复杂性和成本急剧增加,标准化方法变得越来越重要。Imec 还与英特尔或台积电等客户合作,研发可用于最新处理器的新技术。该公司还因其与其长期合作伙伴 ASML 一起帮助开拓 EUV 技术而闻名。归根结底,所有领先的芯片制造商都使用来自少数关键工具制造商的大部分相同设备,因此一定程度的标准化是必要的。然而,这需要在部署前十年开始研发工作,这意味着与 AMD、英特尔和英伟达等公司的近期产品路线图相比,imec 的路线图可以让我们对半导体行业即将取得的进步有更长远的了解。事实上,如果没有 imec 提前数年开展的协作工作,其中许多产品甚至都不可能实现。让我们仔细看看路线图及其背后的一些互补技术。

定义问题

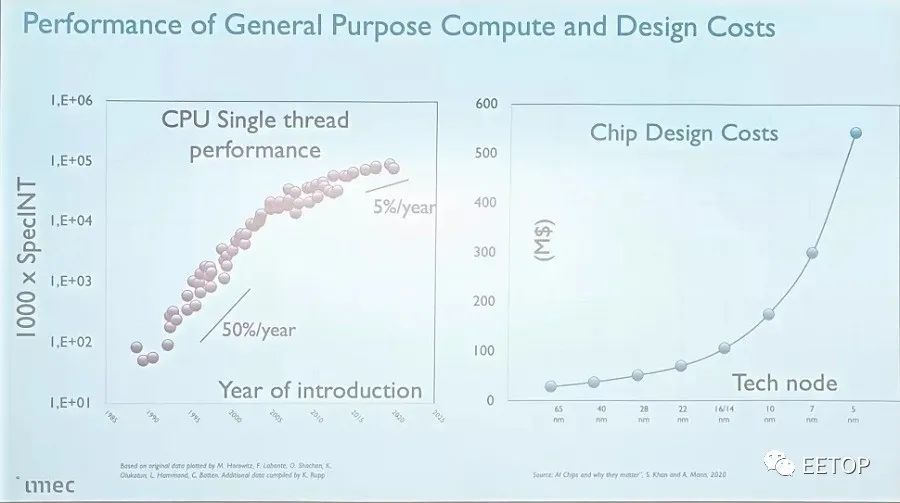

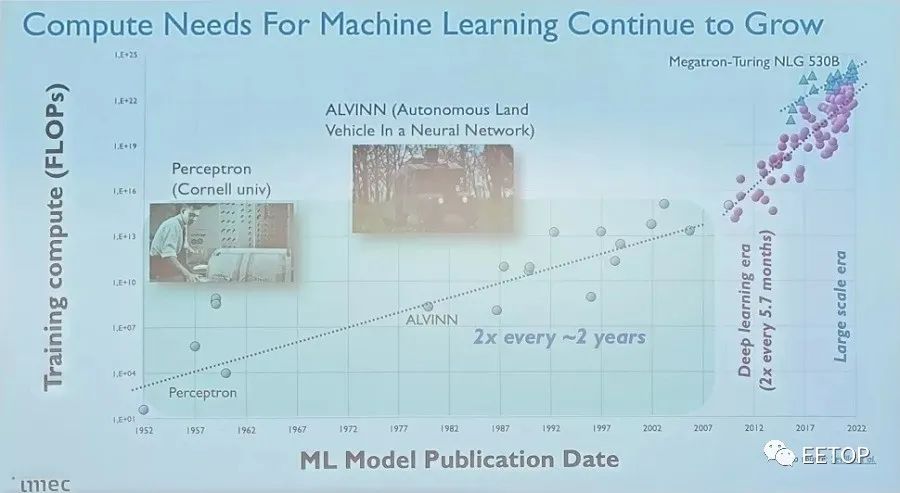

随着节点的进步、成本的飙升以及对更多计算能力的需求,尤其是机器学习的非线性增长,该行业面临着越来越多的挑战。

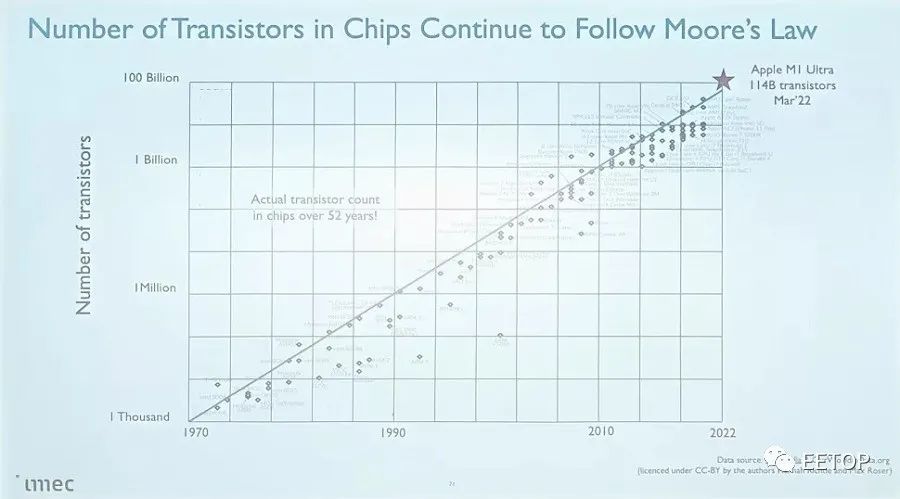

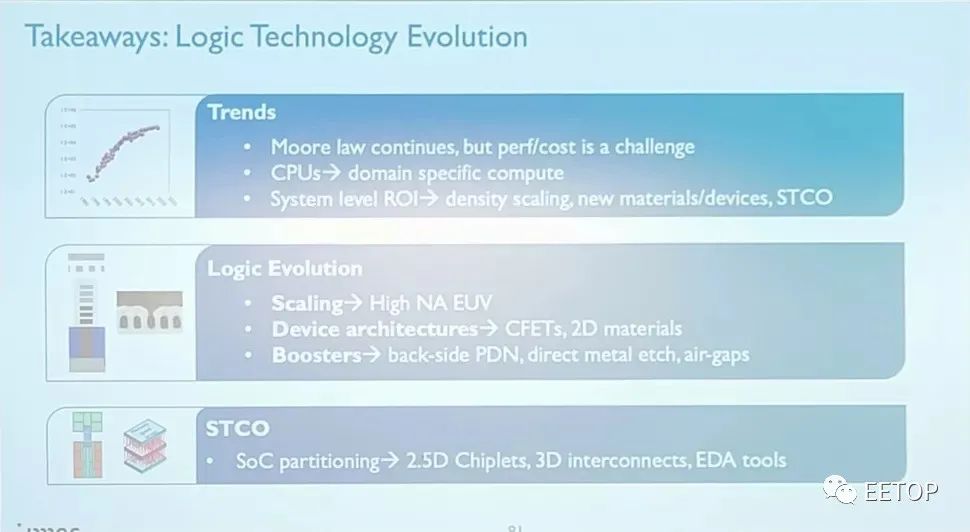

Imec 完全相信摩尔定律在它制定 52 年后仍然有效,尽管我们认为这不适用于该定律的经济部分,该部分还定义了随着时间的推移降低每个晶体管的成本。事实上,如上所示,由于更复杂的设计规则和更长的设计周期,芯片设计成本正在飙升,从而导致每晶体管成本的增加。此外,单线程性能提升正在从 90 年代末和 2000 年代初的 50% 年增长的令人兴奋的日子放缓到每年约 5%。但是,如果我们不考虑密度或经济性,摩尔定律通常保持在每两年晶体管数量翻一番的轨道上——苹果的 M1 Ultra 拥有 1140 亿个晶体管。为了应对单线程性能下降的趋势,我们已经看到 GPU 等特定领域计算设备(专为一组狭窄任务设计的专用处理器)的兴起。这些设备通常高度并行化,因此可以更快地提高功率/性能和面积效率。

Imec 指出,虽然对更多计算能力的需求过去每两年翻一番,基本上符合摩尔定律所提供的性能提升,但机器学习/人工智能所需的原始计算能力大约每六个月翻一番。这提出了一个令人烦恼的问题,因为即使晶体管数量持续翻倍也无法跟上步伐。Imec 认为,尺寸缩放(包括更好的密度和封装技术)、新材料和设备架构以及系统技术协同优化 (SCTO) 的三管齐下的解决方案可以使行业保持在正轨上。

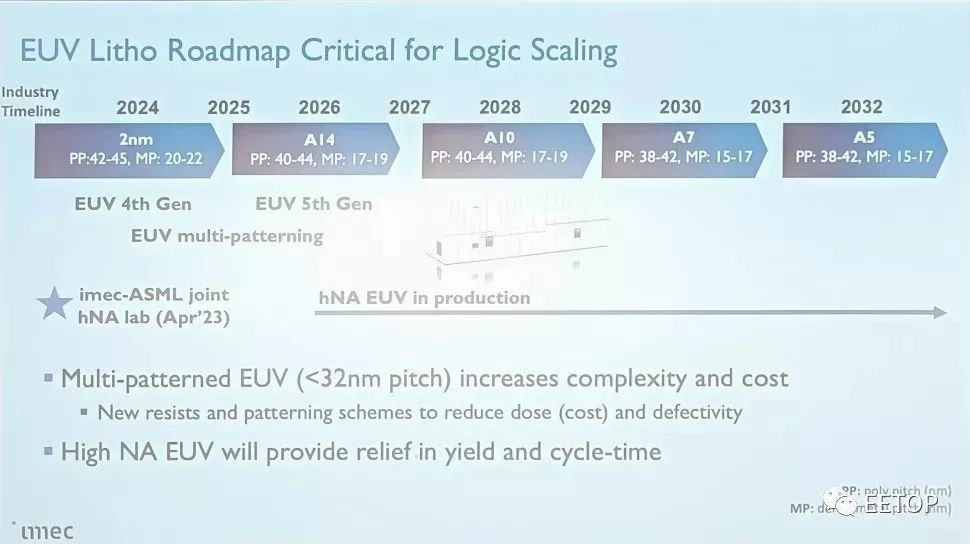

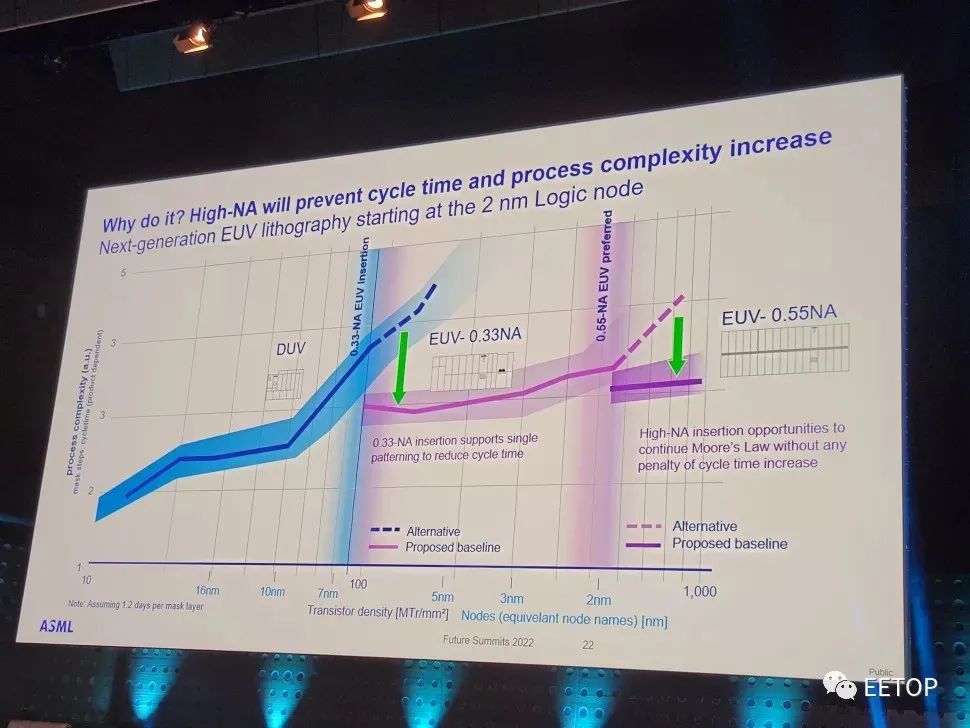

Imec 的晶体管和亚 1nm 工艺节点路线图

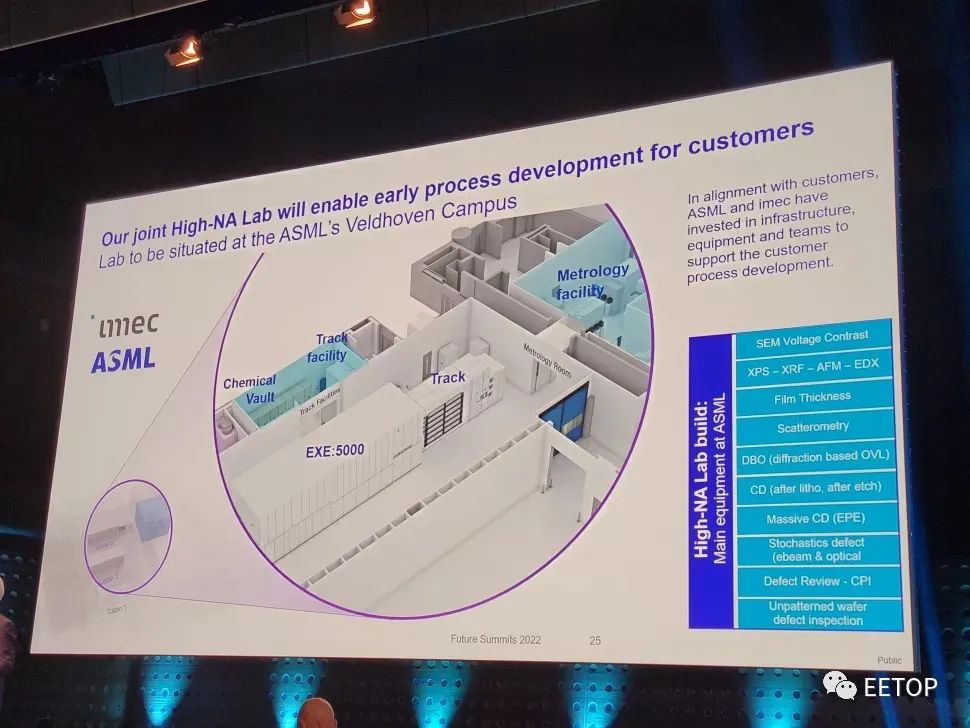

第一步是启用下一代设备。今天的第 4 代 EUV 光刻机的孔径为 0.33,因此芯片制造商将不得不使用多重图案技术(每层超过一次曝光)来创建 2nm 及以上的最小特征。由于晶圆必须为单层“印刷”两次,因此出现缺陷的可能性更高。这将导致产量降低和周期(生产)时间延长,从而导致成本增加。下一代 High-NA 型号(第 5 代)的孔径为 0.55。这种更高的精度将允许在单次曝光中创建更小的结构,从而降低设计复杂性并提高产量、周期时间(每小时 200 多片晶圆)和成本。Imec 和 ASML 预计这些工具将在 2026 年用于量产。第一个价值 4 亿美元的高 NA 工具将于 2023 年上半年在 ASML 完成。Imec 将在 ASML 设施的测试实验室运行,以加快芯片制造商对机器的访问速度(ASML 通常将该设备运送到 imec 的晶圆厂)。

英特尔将成为第一家获得高 NA EUV 设备Twinscan EXE:5200 的公司,该设备预计将于 2025 年正式交付。上述相册中的第二张PPT显示了新型晶体管的路线图,这些晶体管将实现进一步的密度扩展,并希望一些性能改进,也是。Gate AllAround (GAA)/Nanosheet 晶体管于 2024 年首次亮相,采用 2nm 节点,取代了为当今前沿芯片供电的 FinFET。我们已经看到了几家芯片制造商的公告,比如英特尔的四片 RibbonFET,它们采用了这种晶体管技术的不同变体。提醒一下,十埃 (A) 等于一 1nm。这意味着 A14 是 1.4nm,A10 是 1nm,我们将在 2030 年的时间框架内与 A7 一起进入亚 1nm 时代。然而,进程命名节点约定已变成更多的芯片标记营销活动,而不是与任何类型的物理测量相关的指标。在现实世界中,有很多因素会影响工艺节点的经济性和性能,例如晶体管密度、峰值性能、每瓦性能、不同类型的逻辑/电路、SRAM 密度等。在其图表中,imec 使用金属和多晶硅间距以及标准命名约定来提供一些其他重要指标。我们还可以在 ASML 的PPT中看到晶体管密度测量值(上一张专辑中倒数第二张)。

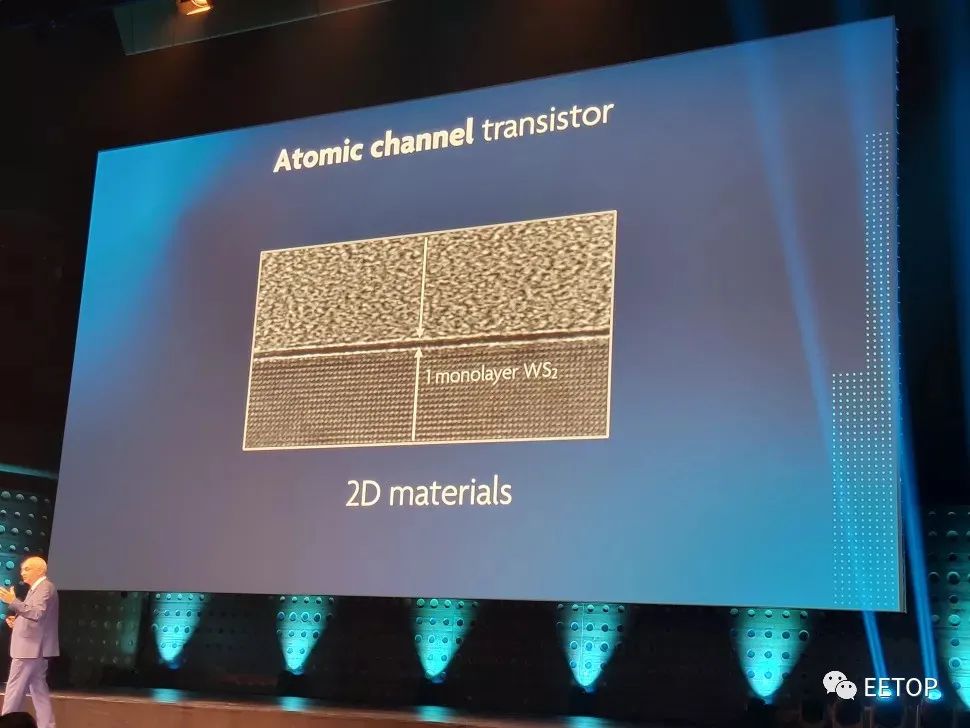

Imec 预计GAA/nanosheet 和 forksheet 晶体管(在最基本的层面上,GAA 的更密集版本)将持续通过 A7 节点。互补 FET (CFET) 晶体管将在 2032 年左右到达时进一步缩小尺寸,从而实现更密集的标准单元库。最终,我们将看到具有原子通道的 CFET 版本,这将进一步提高性能和可扩展性。

正如您在最后两张幻灯片(由 ASML 在活动中展示)中所见,标准 DUV 为我们带来了 100 MTr/mm^2(每平方毫米兆晶体管,一种密度测量),而今天的 0.33NA 将推动行业发展至 ~500MTr/mm^2。即将推出的高 NA 机器将需要在 2nm 上将其提高到 ~1000 MTr/mm^2,并且可能通过多图案化来超越。

Imec 的 BEOL 'Scaling Boosters' 路线图

进一步提高晶体管密度和性能特性也将需要增强的后端 (BEOL) 工艺。BEOL 步骤侧重于将晶体管连接在一起,以实现通信(信号)和电力传输。

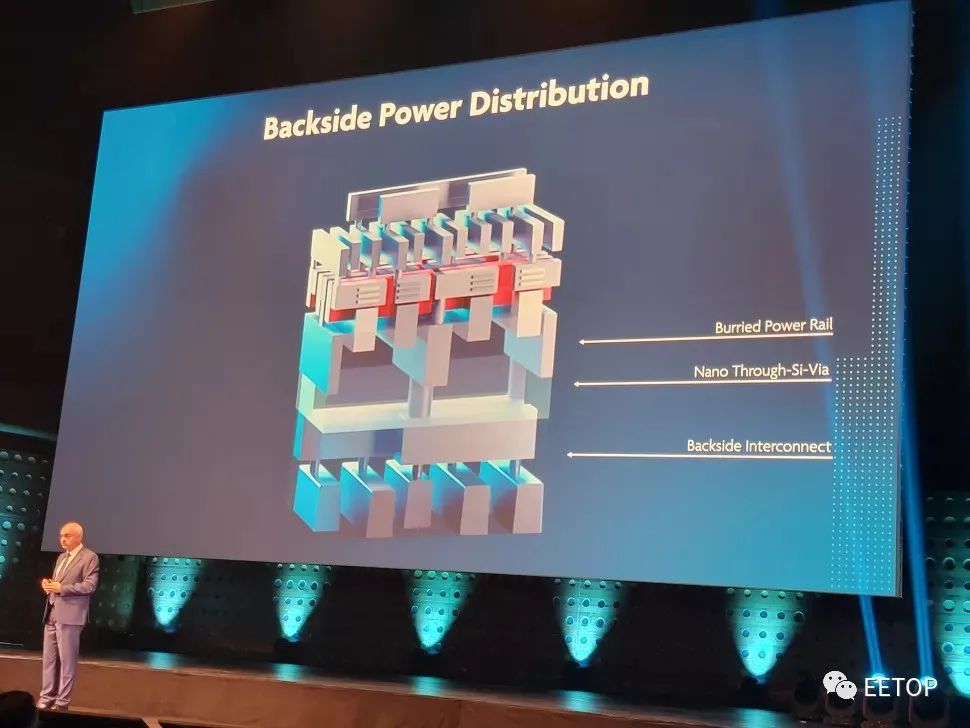

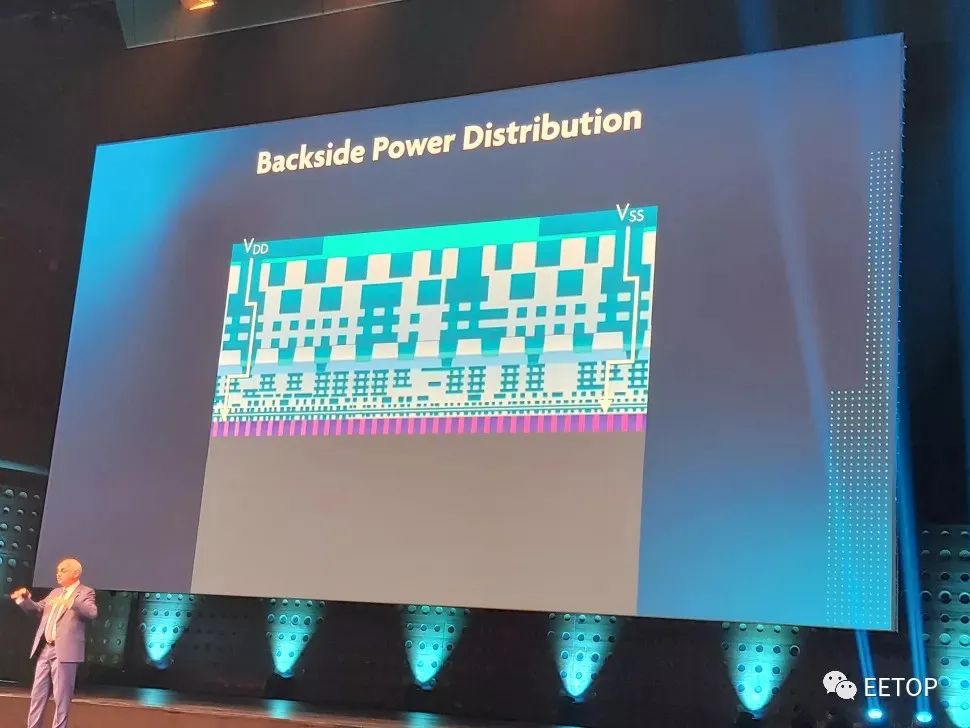

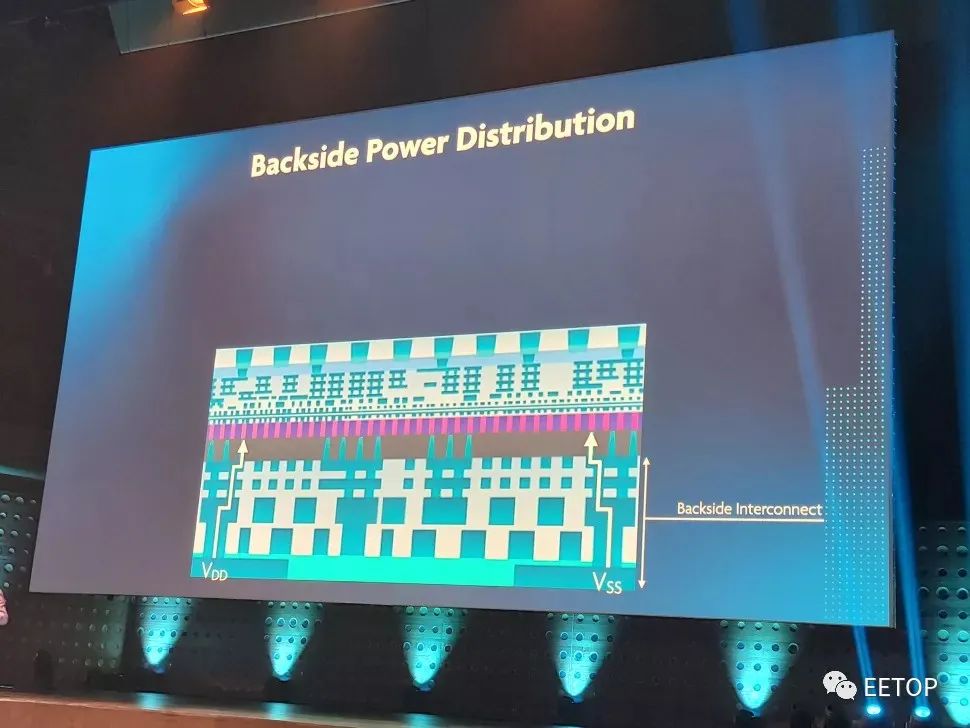

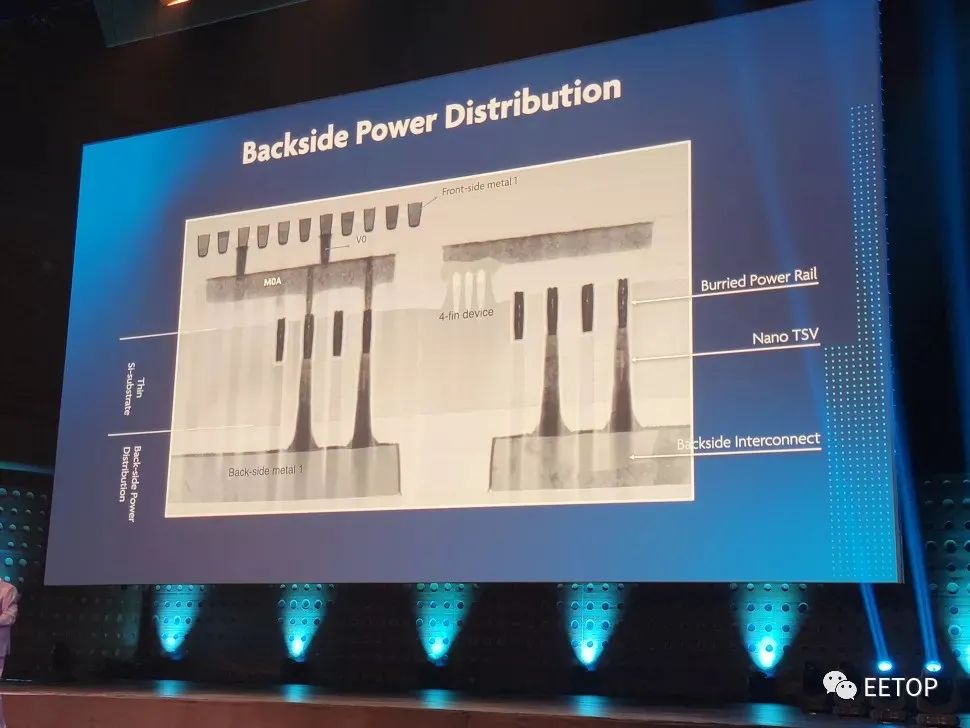

Imec 将这些二次密度提高技术称为“缩放助推器”,因为它们有助于提高晶体管密度和性能,即使它们与晶体管的尺寸/位置没有直接关系。背面配电是将功率带入芯片背面的一项关键进步,英特尔已经宣布了自己的这种技术版本,称为 PowerVIA。这种技术通过晶体管的背面将晶体管的所有功率直接路由到晶体管,将功率分配到晶体管的背面,而数据传输互连保持在另一侧的传统位置。分离电源电路和数据承载互连改善了电压下降特性,允许更快的晶体管开关,同时在芯片顶部实现更密集的信号路由。信号传输也受益,因为简化的布线可实现更快的导线,同时降低电阻和电容。Imec 坚信背面供电将延伸到所有领先的芯片,并且已经在这项技术上研究了五年,创造了自己独特的专利背面供电技术。自然,热量可能成为背面功率传输的一个问题,因为晶体管将在通常散热的硅一侧放置金属层。尽管如此,imec 告诉我们,使用的金属(目前是铜)足以散热以减少影响。但是,需要进行一些设计考虑以适应这种技术。

路线图的进一步改进包括用于互连的直接金属蚀刻技术,以及具有气隙的自对准通孔。互连,即实现电力传输和通信的细线,已成为扩展的最大障碍之一。随着时间的推移,这个问题变得越来越明显——这些导线的宽度只需几个原子厚。Imec 还在研究替代铜的新金属,其中石墨烯是候选金属。

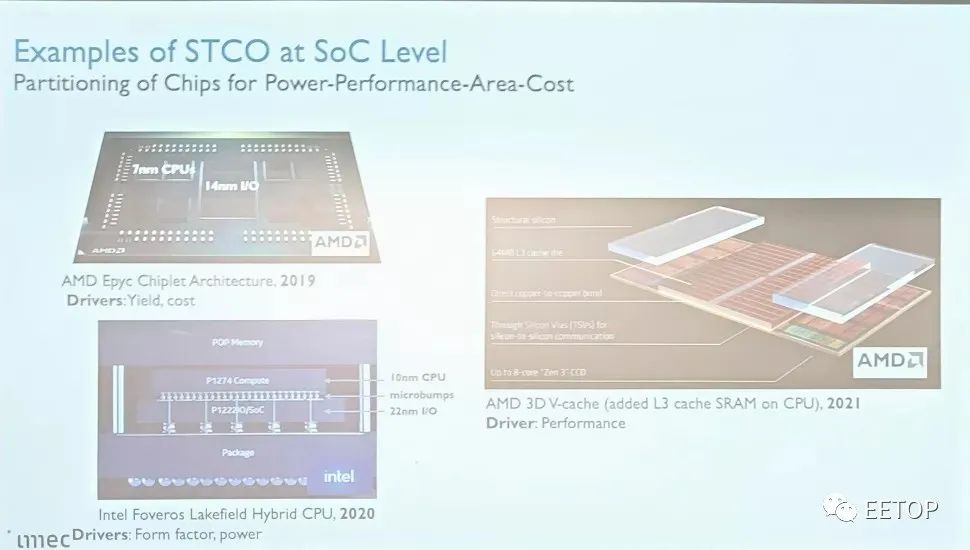

Imec 还在研究系统技术协同优化 (SCTO) 技术,例如 3D 互连和 2.5D 小芯片实现。缺乏用于 3D 芯片设计的电子设计自动化 (EDA) 软件是阻碍更广泛行业采用的主要障碍。Imec 正在与 Cadence 合作,以启用可简化 3D 设计过程的高级软件。

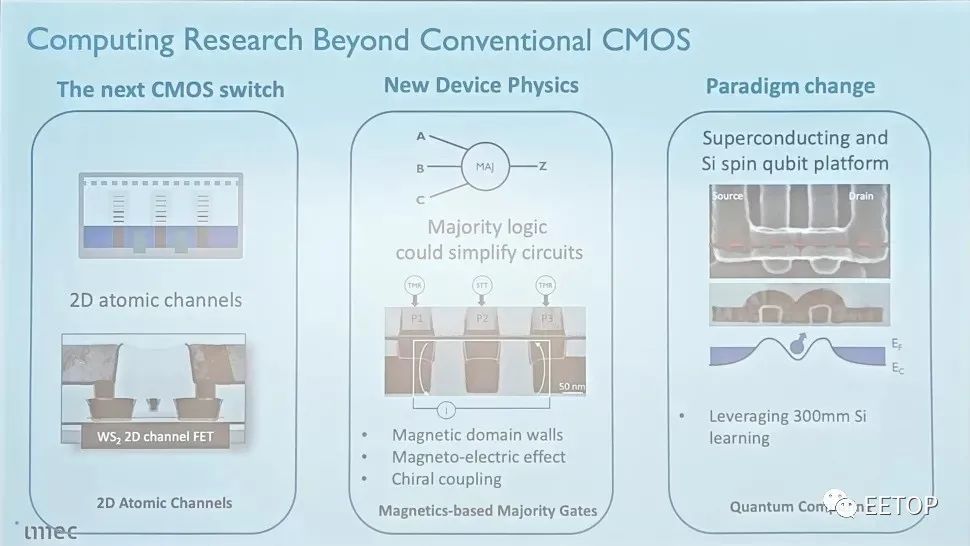

延伸到 2030 年以后更广阔的视野,我们看到 imec 设想新材料将取代硅和 2D 原子通道的出现。Imec 还认为,随着行业无情地转向量子计算,基于磁性的门可能会成为一种替代方案。

原文:

https://www.tomshardware.com/news/imecs-sub-1nm-process-node-and-transistor-roadmap-until-2036-from-nanometers-to-the-angstrom-era

未来智能实验室的主要工作包括:建立AI智能系统智商评测体系,开展世界人工智能智商评测;开展互联网(城市)大脑研究计划,构建互联网(城市)大脑技术和企业图谱,为提升企业,行业与城市的智能水平服务。每日推荐范围未来科技发展趋势的学习型文章。目前线上平台已收藏上千篇精华前沿科技文章和报告。

如果您对实验室的研究感兴趣,欢迎加入未来智能实验室线上平台。扫描以下二维码或点击本文左下角“阅读原文”

7232

7232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?