本文所用文档和工程文件获取点击此处!!!

文档25出,文档中有详细的推导过程,可以根据设计要求计算出具体器件参数,可以自己搭建并仿真出来。

电路工程文件加版图(DRC、LVS、PEX均通过),有仿真验证视频,打包200出,介意勿扰

工艺:TSMC180

前仿真指标

低频增益AOL:75dB

增益带宽积GBW:6.5MHz

相位裕度:65°

共模抑制比CMRR:139dB

正电源抑制比PSRR+:-80dB

负电源抑制比PSRR-:-133dB

有版图,已过DRC、LVS、PEX,可以后仿真,面积58uX133u

————————————————

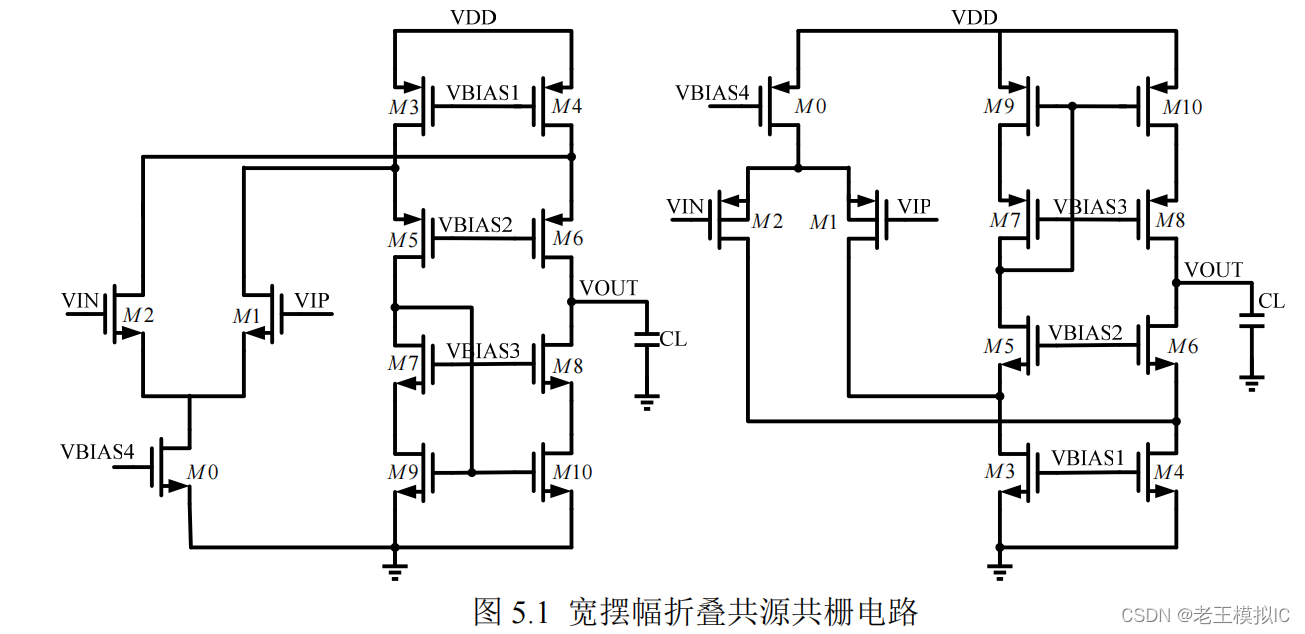

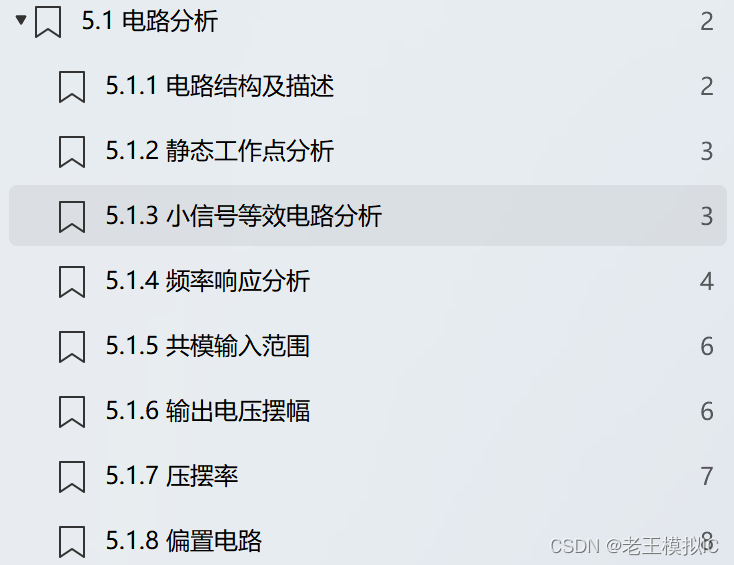

5.1 电路分析

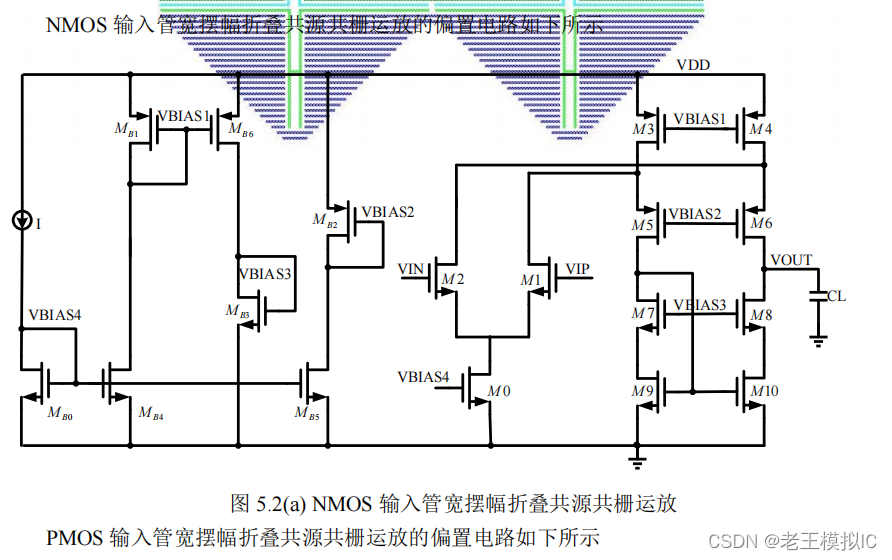

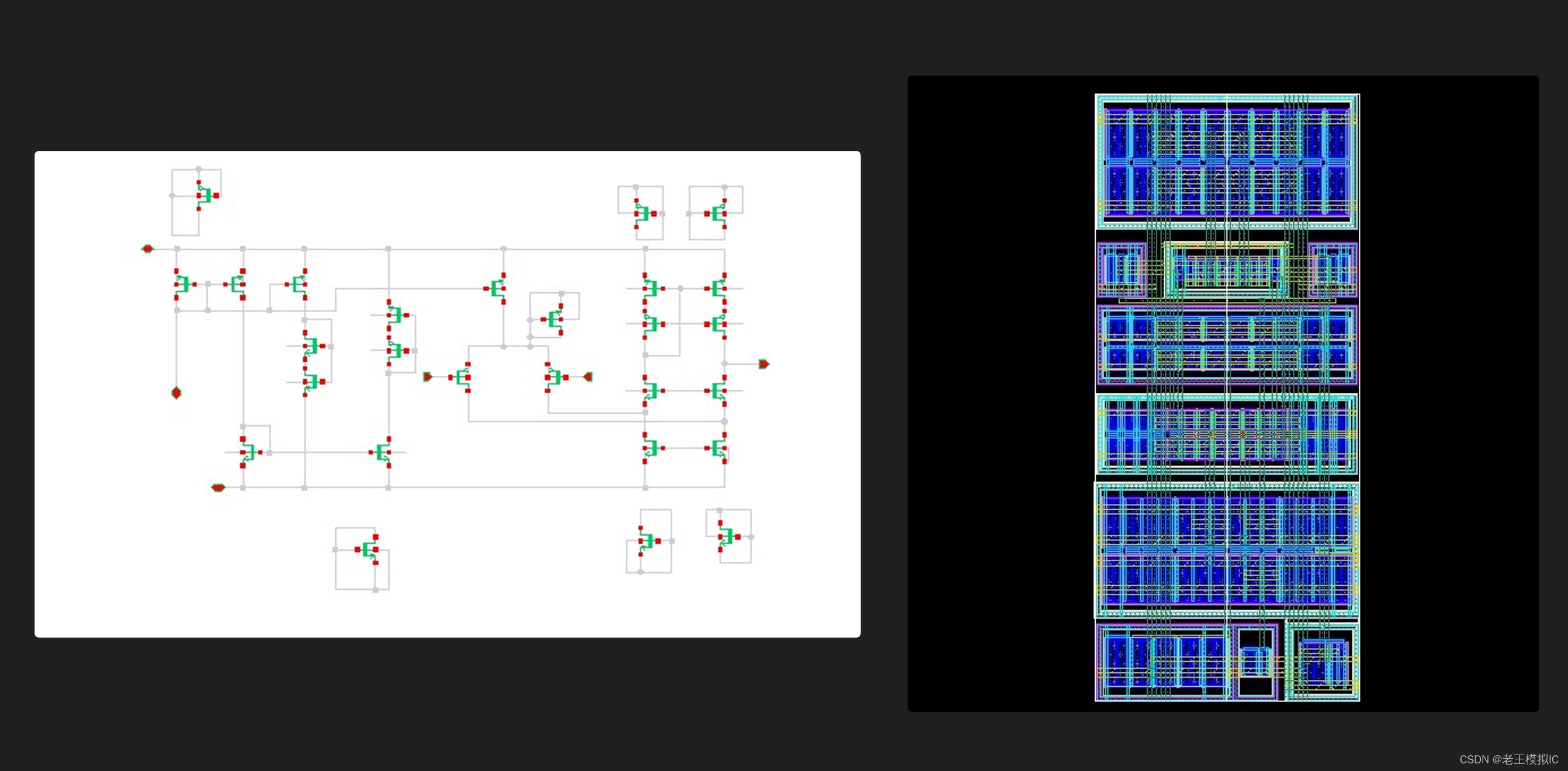

单端输出的折叠共源共栅的结构比较多,在这里选取高增益宽摆幅结构,根据输入管区

分可以分为

N

输入管和

P

输入管结构,主体电路如下所示:

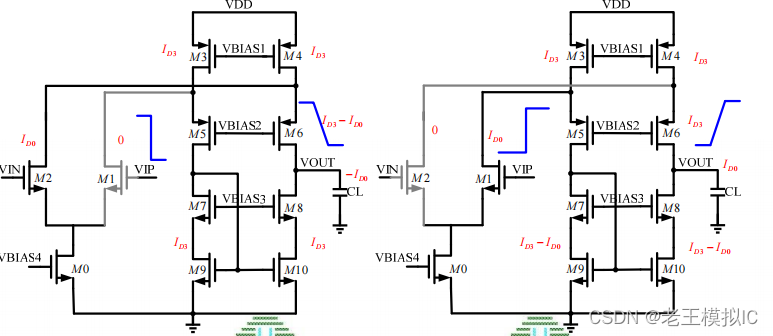

如图 5.1

所示折叠共源共栅放大器的主体电路,使用双端输入单端输出形式,

M1

和

M2

管为输入管,

CL

为负载电容,

VBIAS1-4

为偏置电路,其中

VBIAS4

为差分输入管提供电流,

VBIAS1

为共源共栅结构提供电流,注意在设计中

VBIAS1

提供的电流一定要比

VBIAS4

提

供的电流大,否则电路无法正常工作。

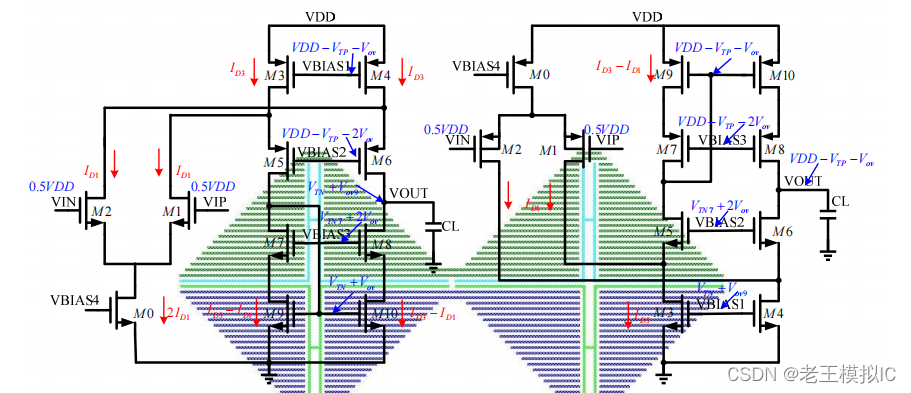

5.1.2 静态工作点分析

电路的静态工作点如下所示,可以看出输出点的静态工作点非常接近上电源或下电源,

这会导致这种类型的放大器具有较小的对称摆幅,且受限于共源共栅结构,放大器最大摆幅

也比两级放大器小。

5.1.3 小信号等效电路分析

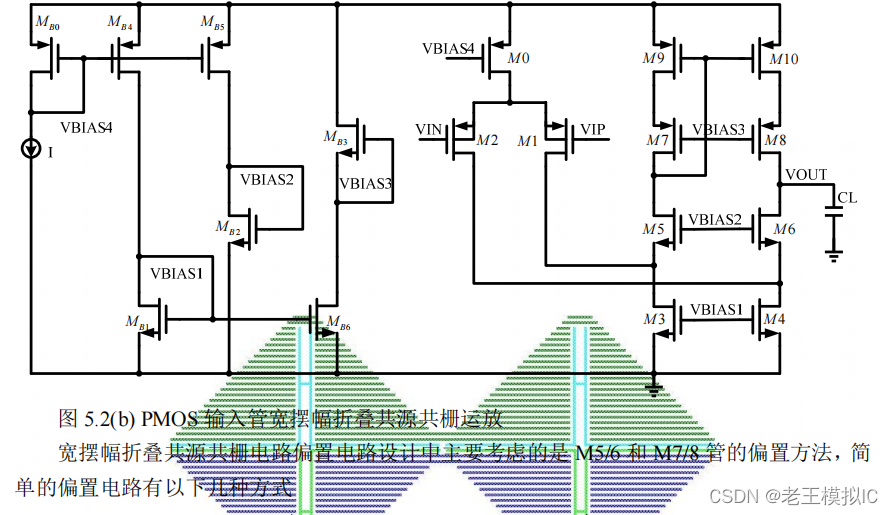

NMOS

输入管的电路和

P

输入管的电路是相同的,所以这里只对

NMOS

输入管结构的电

路进行分析,结构可直接应用到

PMOS

输入管结构。

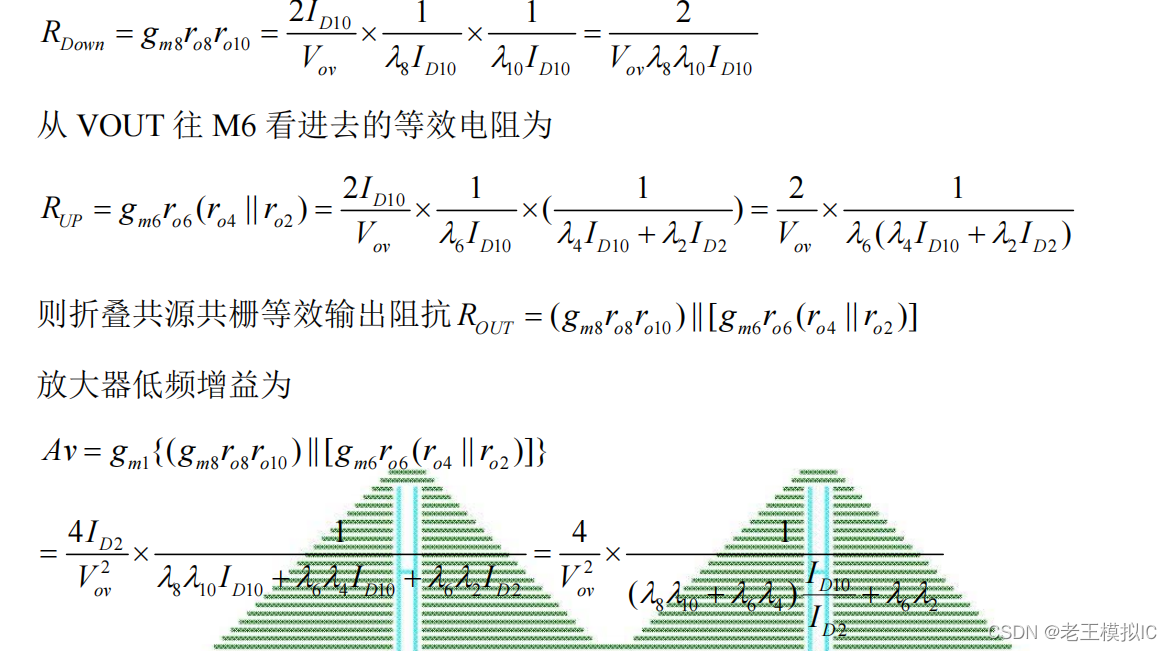

放大器的跨导

从

VOUT

往

M8

看进去的等效电阻

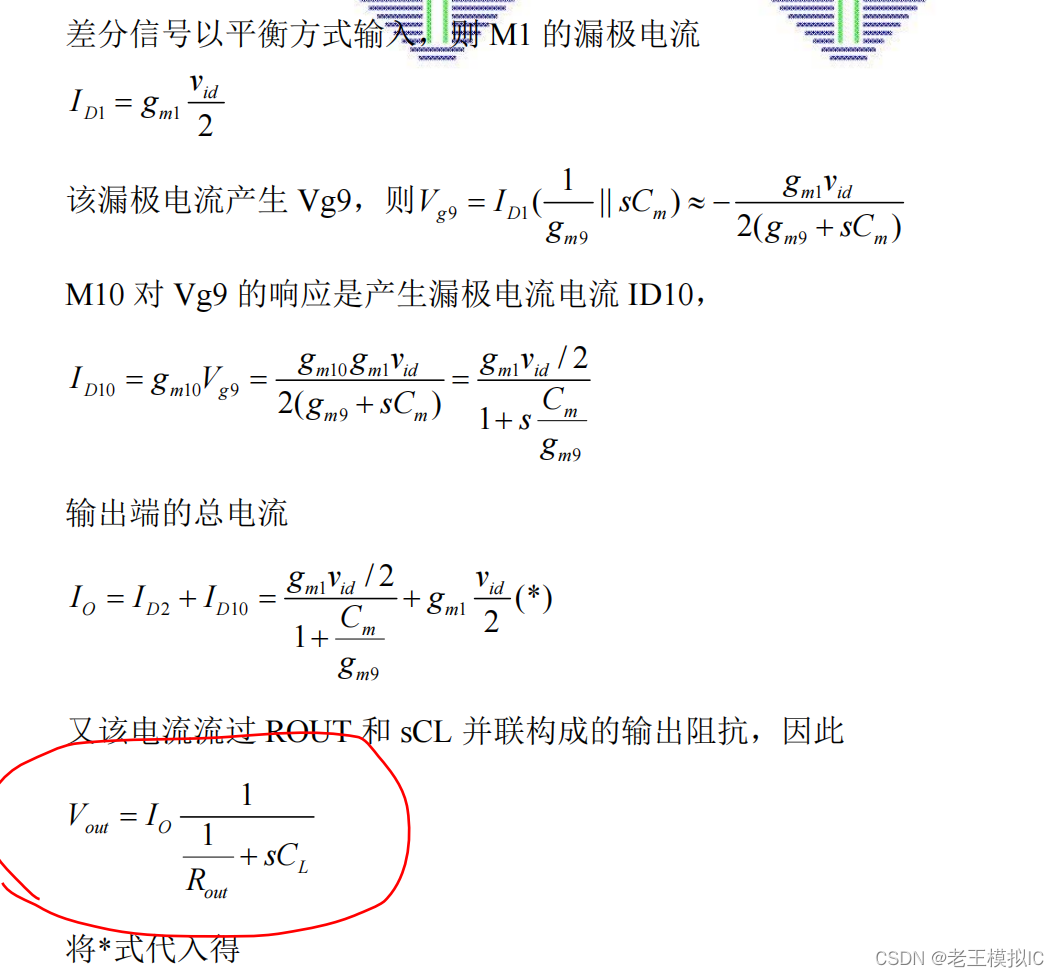

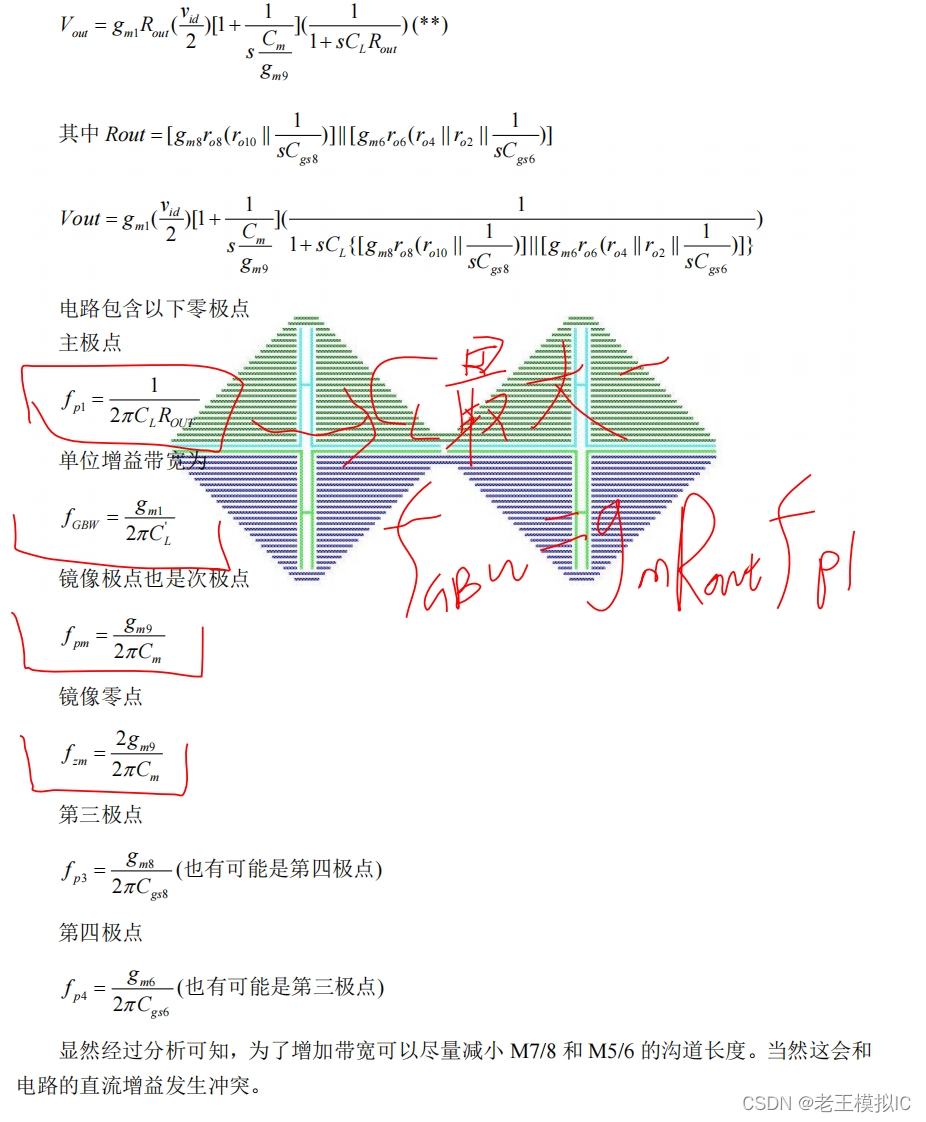

5.1.4 频率响应分析

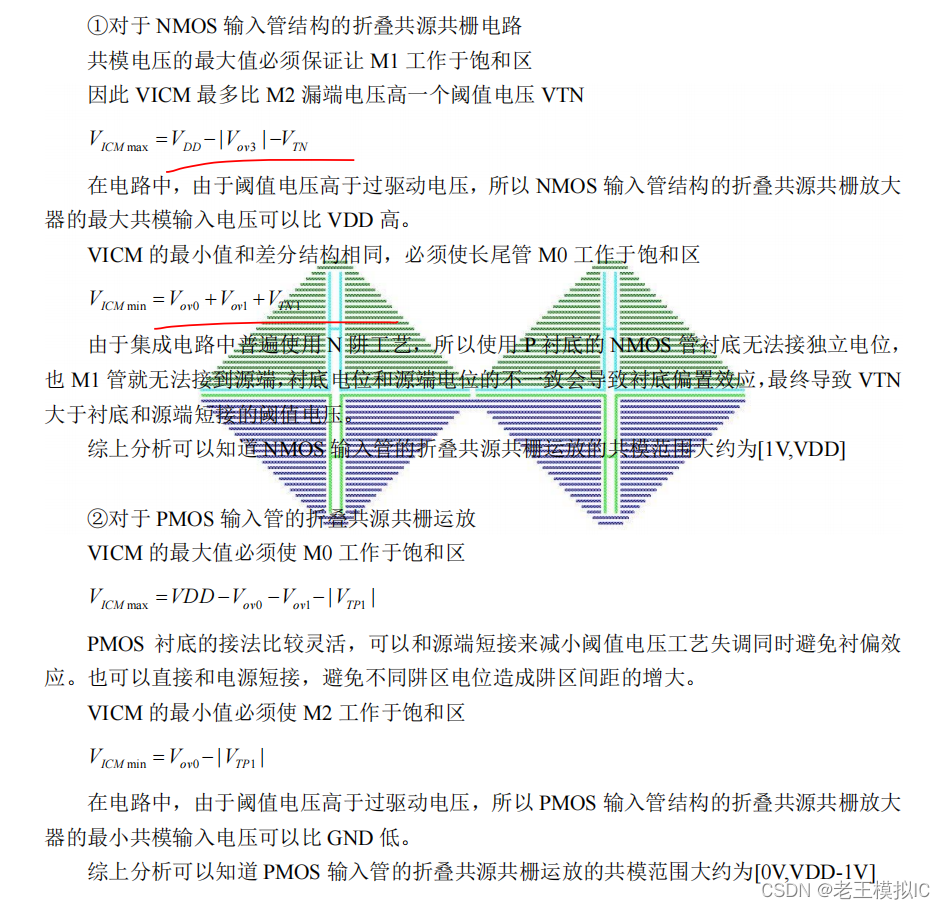

5.1.5 共模输入范围

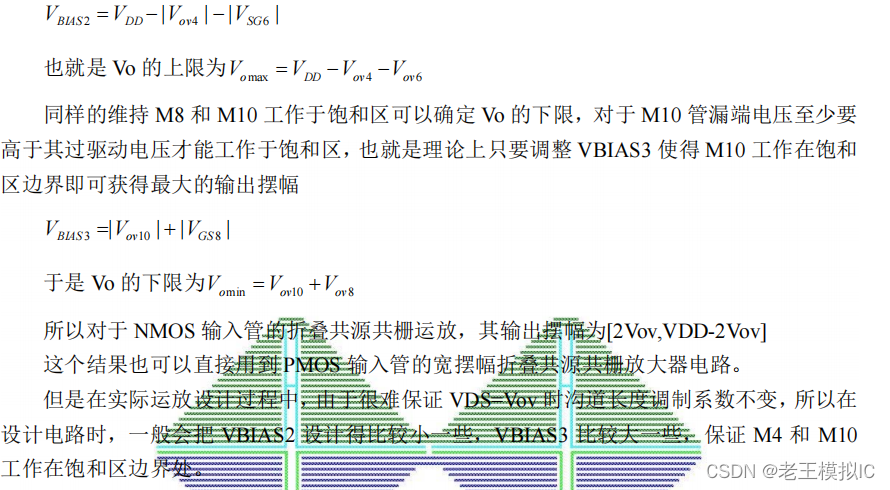

5.1.6 输出电压摆幅

对于 NMOS

输入管结构的折叠共源共栅电路 维持 M4

和

M6

工作在饱和区可以确定

Vo

的上限,对于

M4

管漏端电压至少要高于其过 驱动电压才能工作于饱和区,也就是理论上只要调整 VIAS2 使得

M4

工作在饱和区边界处即

可获得最大输出摆幅。

5.1.7 压摆率

当差模输入电压比较大的时候需要考虑摆率的问题,以

NMOS

输入管折叠共源共栅运放

为例进行分析,结果同样可以推导至

PMOS

输入管折叠共源共栅运放中。。

假设

VIP

接负脉冲时

M1

截止,

M2

导通,流过的电流为

ID0

,则流过

M6

的电流为

ID3-ID0

,

流过

M5

的电流为

ID3

,镜像到

M8

和

M9

电流也是

ID3

,则有大小为

ID0

的电流给

CL

放电,

电压与时间的关系是斜率为

-ID0/CL

的线性函数,即

SR-=ID0/CL

。

假设

VIP

接正脉冲时

M2

截止,

M1

导通,流过的电流为

ID0

,则流过

M5

的电流为

ID3-ID0

,

镜像到

M8

和

M9

电流也是

ID3-ID0

,则有大小为

ID0

的电流给

CL

充电,电压与时间的关系

是斜率为

ID0/CL

的线性函数,即

SR+=ID0/CL

。

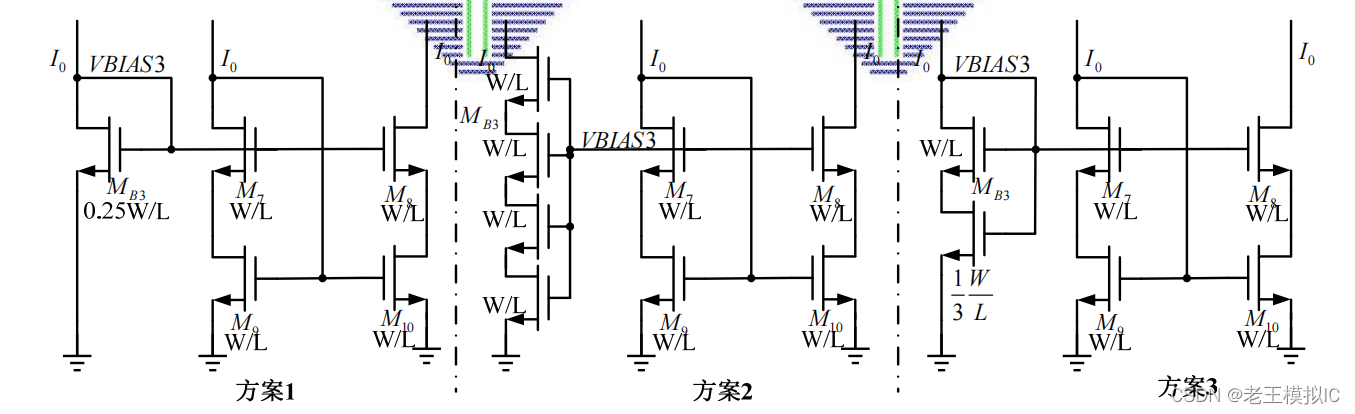

5.1.8 偏置电路

方案 1

中,会将偏置产生管

MB3

宽长比设置为对应器件的

1/4

尺寸,但是这种实现方法 存在衬底偏置效应的影响,一般教材建议的尺寸是 1/5

对应器件尺寸。

方案 2

由方案

1

改进而成,将

4

个宽长比一致的器件串联而成,虽然也存在衬底偏置效 应,但是该方案减缓了衬底偏置效应的影响。

方案 3

中下面的管子取

1/3

尺寸,

MB3

和对应器件尺寸一致。为了保证设计余量一般将 下面的管子的尺寸设计为 1/5.。

实际产生偏置电压的方法有许多,可以见参考[4]中第

5.1

章节内容。

但是需要注意的是当 VDS

很小的时候

(0.2-0.3V)

,沟道长度调制系数很小,很难保证高 增益,所以这些 1/3

或

1/4

的管子,一般取得更小,比如

1/6

甚至

1/10

。

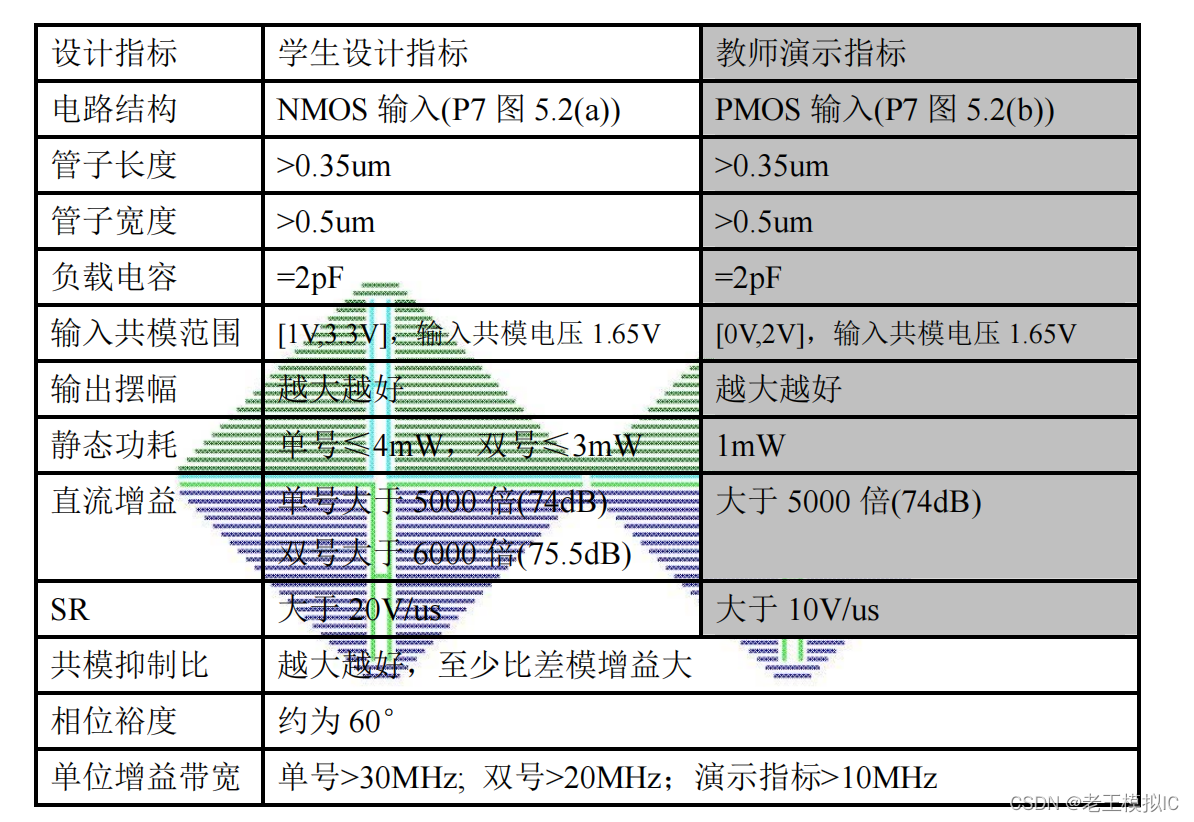

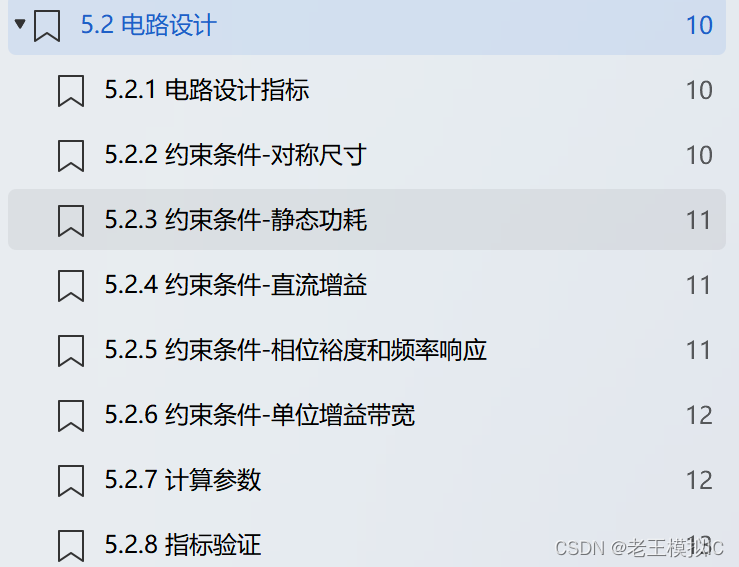

5.2 电路设计

5.2.1 电路设计指标

指标推导计算和仿真电路搭建部分有偿获取

文档和工程文件获取

文档25出,文档中有详细的推导过程,可以根据设计要求计算出具体器件参数,可以自己搭建并仿真出来。

电路工程文件加版图(DRC、LVS、PEX均通过),有仿真验证视频,打包200出,介意勿扰

工艺:TSMC180

前仿真指标

低频增益AOL:75dB

增益带宽积GBW:6.5MHz

相位裕度:65°

共模抑制比CMRR:139dB

正电源抑制比PSRR+:-80dB

负电源抑制比PSRR-:-133dB

有版图,已过DRC、LVS、PEX,可以后仿真,面积58uX133u

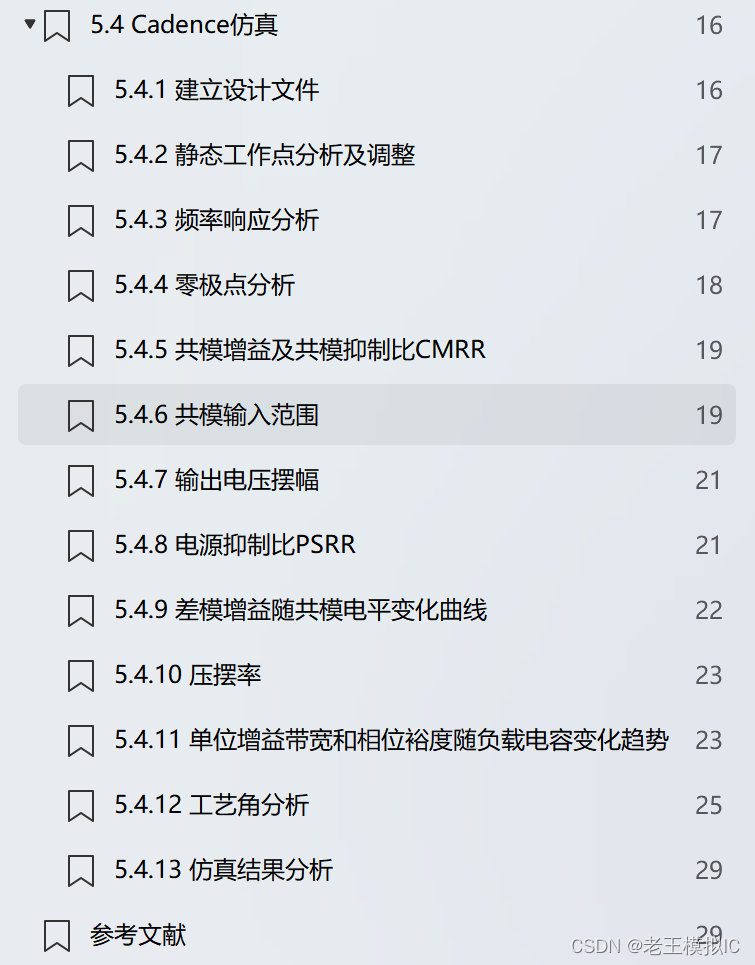

完整文档目录截图

7881

7881

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?