24小时秒发

这份文档是IBM T. J. Watson Research Center的Troy Beukema在2009年IEEE固态电路学会(Solid-State Circuits Society, SSCS)丹佛分会研讨会上关于高速串行器/解串器(Serializer/Deserializer, SERDES)系统设计与分析的演讲概要。SERDES系统是现代高速数据通信中的关键组件,用于在单个信道中串行地发送和接收高速数据。以下是文档内容的简要概述:

引言

- 驱动高速互连的因素:随着视频互联网、三维内存、高性能计算(GPU)、大容量存储以及多处理器CPU等技术的发展,对更高带宽的互连需求不断增长。

- 技术趋势:CMOS工艺节点的不断缩小(如从180nm到32nm,甚至未来可能到4nm),以及存储密度的增加(如从60Gb/in²到1000Gb/in²),推动了高速互连技术的发展。

数据互连应用

- 芯片到芯片(C2C):处理器、内存、HCA(主机通道适配器)等之间的互连。

- 芯片到内存(C2M):处理器与内存之间的连接。

- 芯片到板(C2B):芯片与主板之间的连接。

- 板到板(Board-To-Board):长距离背板连接,如PCI Express Gen 3(8G)。

- 芯片到外设(C2P):如SATA3(6G)、USB 3.0(4.8G)等。

主要内容

- S-参数概述:S-参数是描述线性网络(如传输线)频率响应的复数参数,对于理解和设计高速互连至关重要。

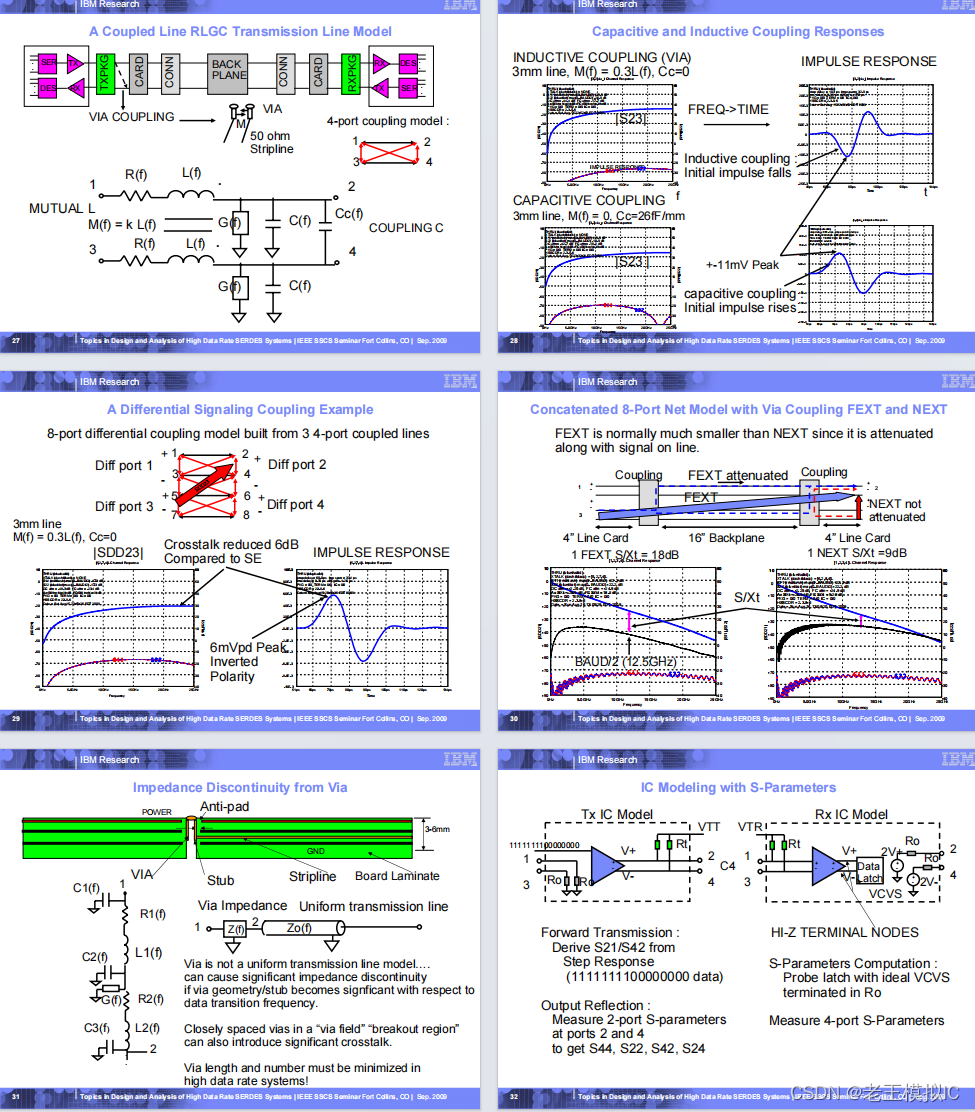

- 链路模型:建立准确的链路模型以预测信号在传输过程中的行为,包括衰减、延迟和反射等。

- 性能分析:通过仿真和测试评估SERDES系统的性能,包括误码率(BER)、眼图质量等。

- 线路均衡化:使用均衡技术(如前馈均衡FFE、判决反馈均衡DFE)来补偿信号在传输过程中的损失,提高信号质量。

- 时钟和数据恢复(CDR):从接收到的信号中恢复出原始的时钟和数据,是SERDES系统的核心功能之一。

- 抖动分析:分析各种来源的抖动(如随机抖动、确定性抖动)对系统性能的影响,并设计相应的抖动抑制策略。

- 20-25Gb/s I/O系统:探讨如何实现和优化20-25Gb/s的高速输入输出系统。

- 数字/ADC I/O:讨论数字接口和模数转换器(ADC)在高速I/O系统中的应用。

附录

- 可能包含额外的技术细节、参考文献或相关案例研究。

总结

该文档为听众提供了一个关于高速SERDES系统设计与分析的全面概览,从驱动因素、应用场景到关键技术点,旨在帮助听众理解这一领域的最新进展和挑战。随着技术的不断进步,对更高速度和更高性能互连系统的需求将持续增长,SERDES系统将继续在这一领域发挥关键作用。

597

597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?