原理图是使用PADS Logic进行设计的,原理图设计完成之后,需要导入到PADS Layout进行PCB设计,导入方法如下:

点击标准工具栏右边的PADS Layout图标,如下图所示:

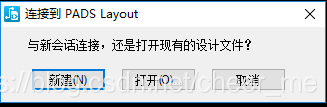

点击PADS Layout图标之后,弹出“连接到PADS Layout”对话框,提示是和已有的PCB文件连接还是新建一个PCB文件并连接,因为我们还没有新建PCB,所以这里选择“新建”,如果前面有使用PCB Layout新建过对应的PCB文件,可以直接选择“打开”,然后选择对应的PCB文件。如下图所示:

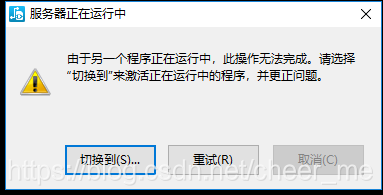

如果弹出下面的对话框,作为直接点击“切换到”即可,如果没有反应,重新试一次。

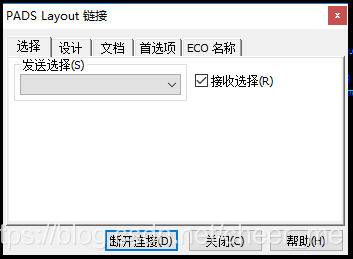

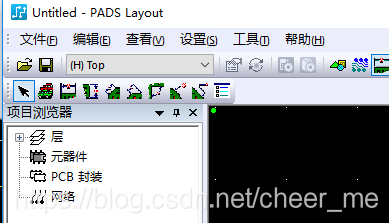

连接成功之后,就会显示PADS Layout链接对话框,同时会打开PADS Layout并新建无标题的PCB文件,如下图所示:

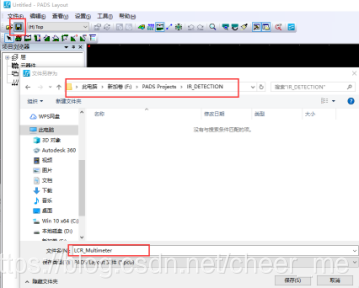

这里我们可以将PCB保存在和原理图对应的目录下,名称可以和原理图一样,如下图所示:

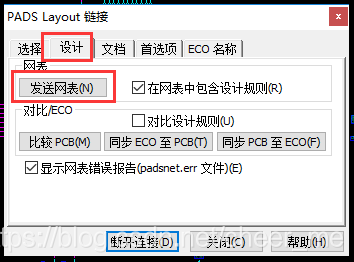

在PADS Layout链接对话框中点击“设计”标签,点击“发送网表”,如下图所示:

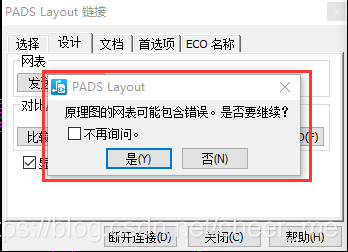

可能会提示一些警告和错误,自己可以看一下提示,如果这些警告没有影响可以忽略,如果影响到PCB的功能则回头修改,如下图所示:

如果提示电源的网络标号问题(比如3.3V和5V使用了同一个标号),这个可以忽略,直接点“是”继续即可,之后网表就会全部导入到PCB文件中,如下图所示:

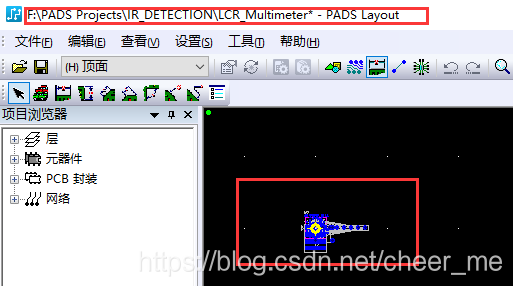

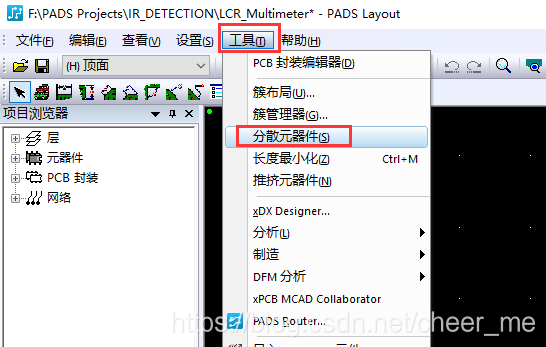

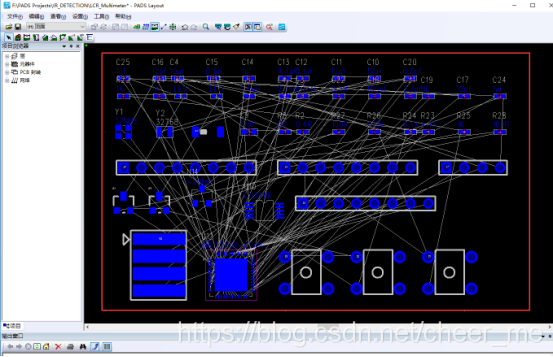

只不过导入PCB之后,这些元器件封装是全部重叠在一起的,点击“工具”-->“分散元器件”即可将封装分开排列,如下图所示:

到这里,原理图导入到PCB就已经完成了。如果有不清楚的地方可以在下方留言。

对应的视频教程以及更多文章请关注微信公众号:ubug404

790

790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?