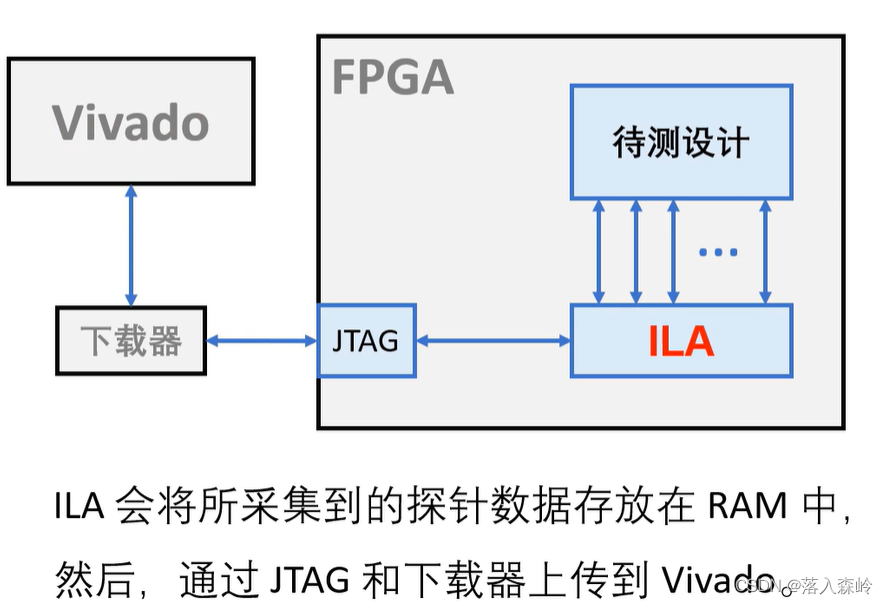

调用IP核来实现功能,逻辑分析仪ILA,查看将代码烧录到FPGA里后,可以插入探针来查看数据的变化

介绍:

调用加法器的IP核,完成加法,再调用ILA的ip核,来检测FPGA里某个数据的值,

四位的sw[3:0]给a,四位的sw[7:4]给b,a+b=sum,将a,b,sum显示在FPGA的数码管上

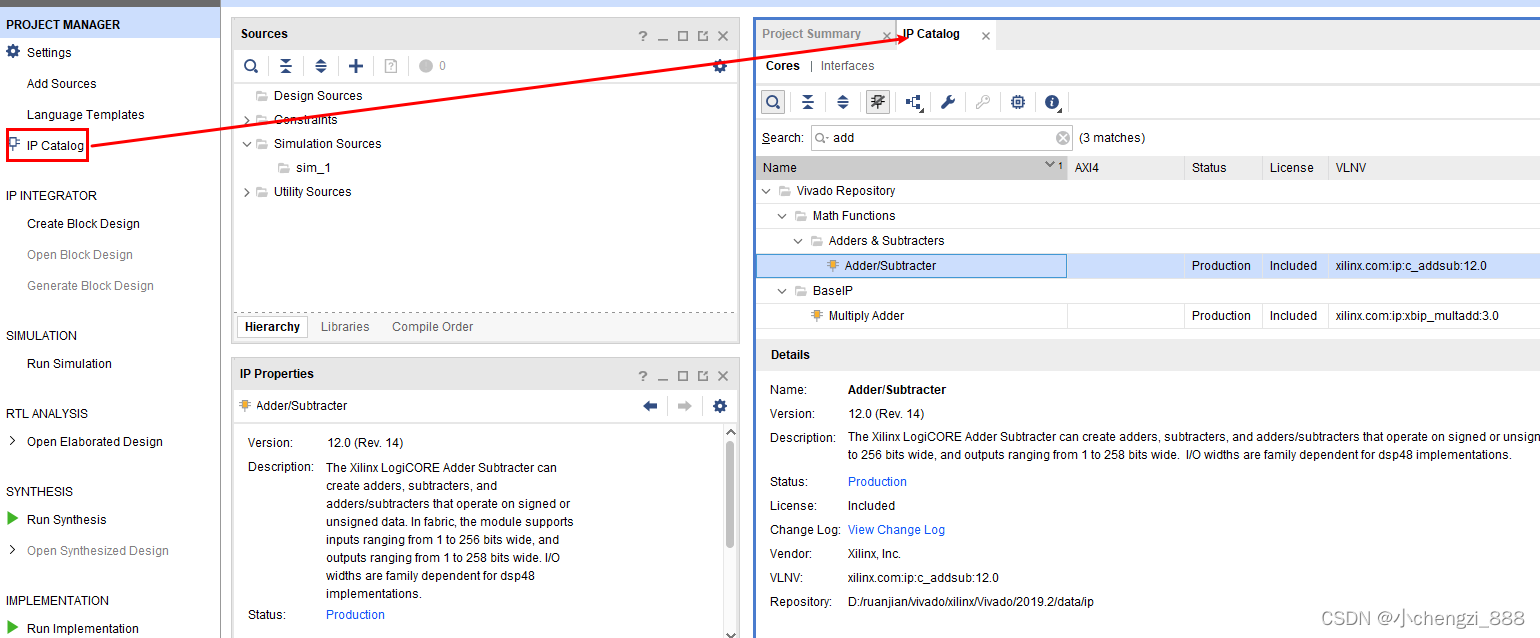

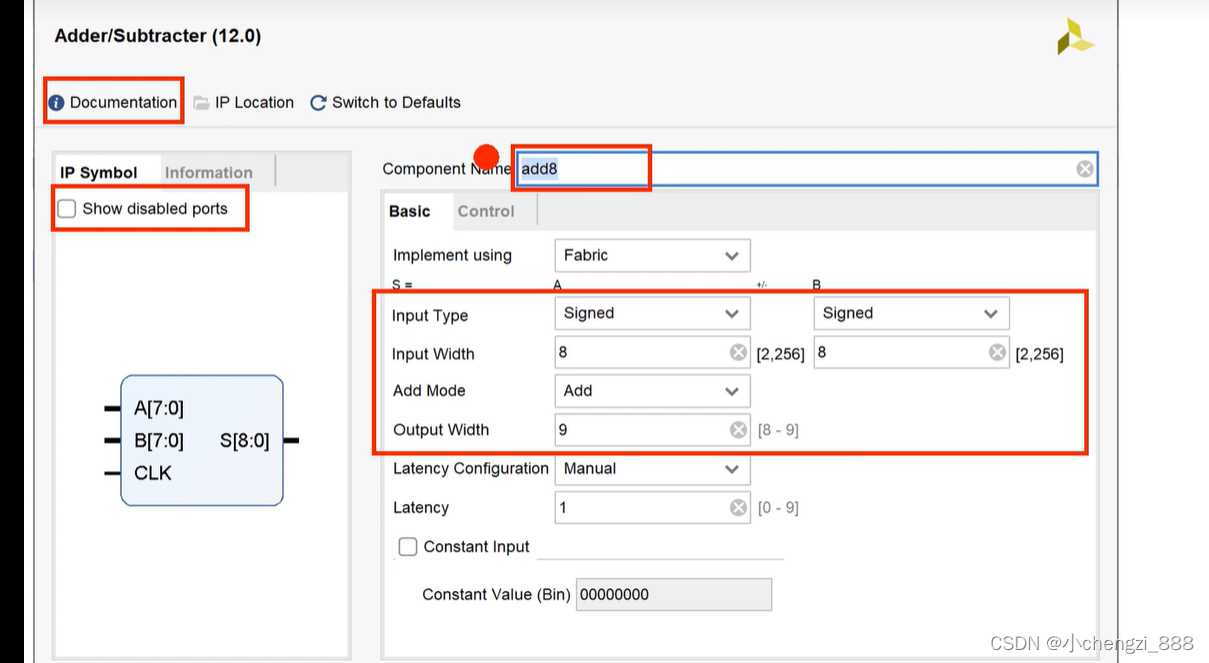

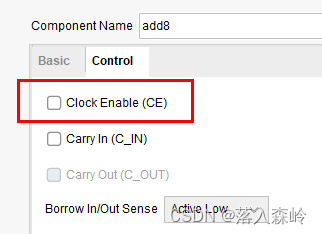

IP核的调用

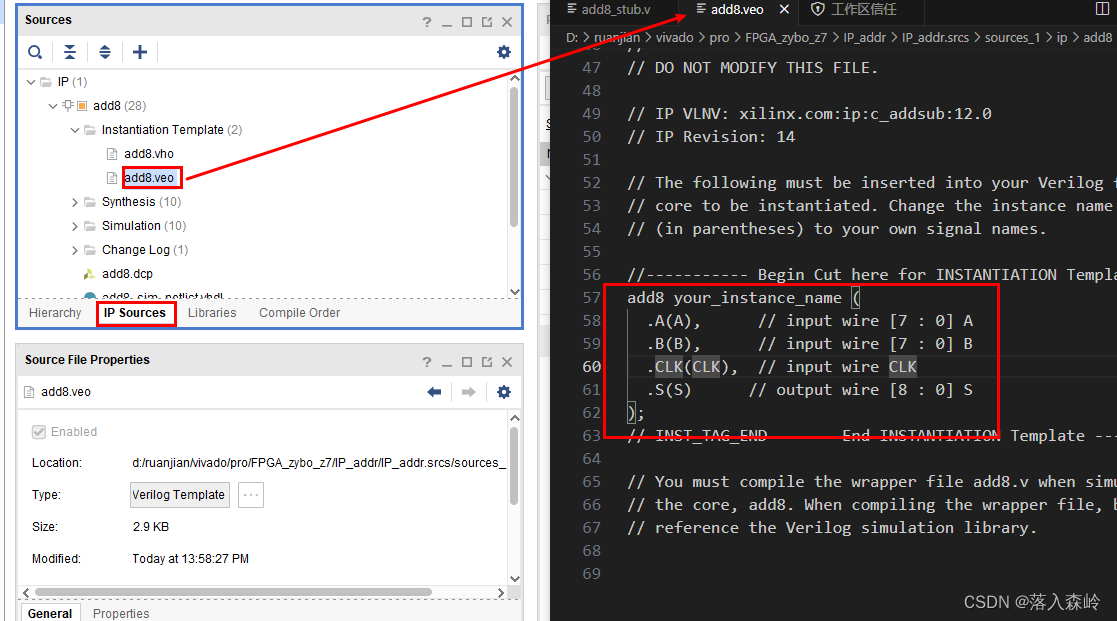

此处我们调用加法器的IP核

点开.veo文件后,可以看到一个实例化的模块your_instance_name

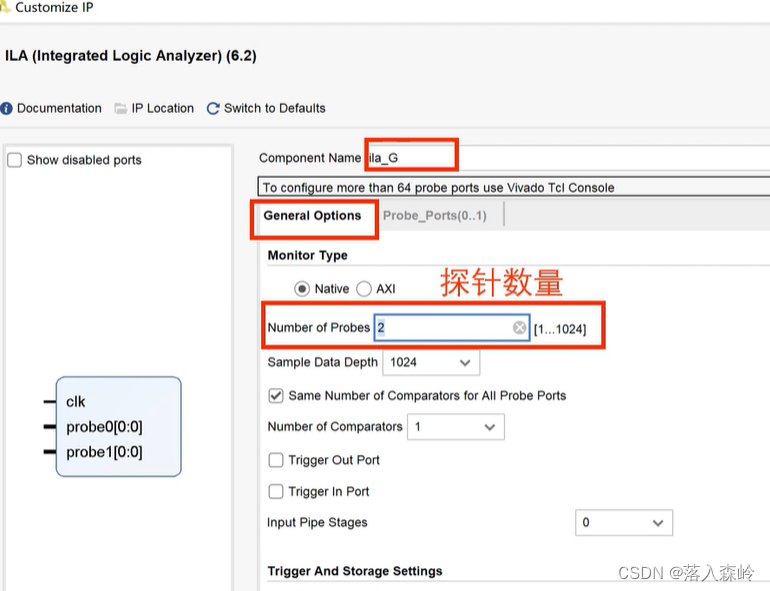

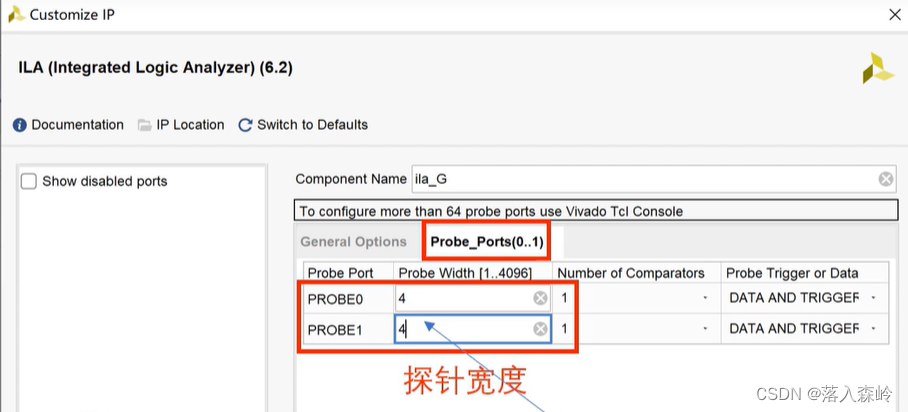

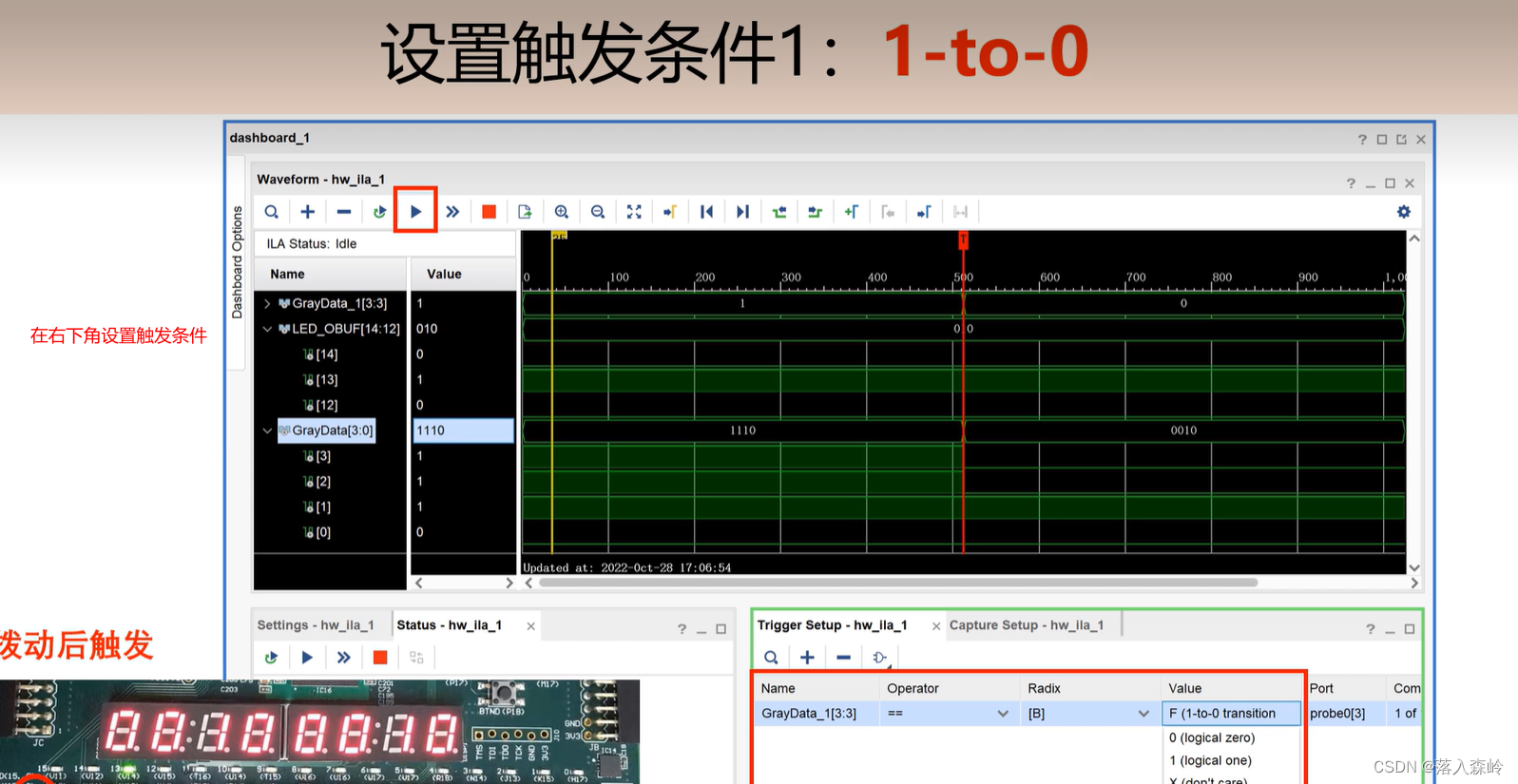

ILA的使用

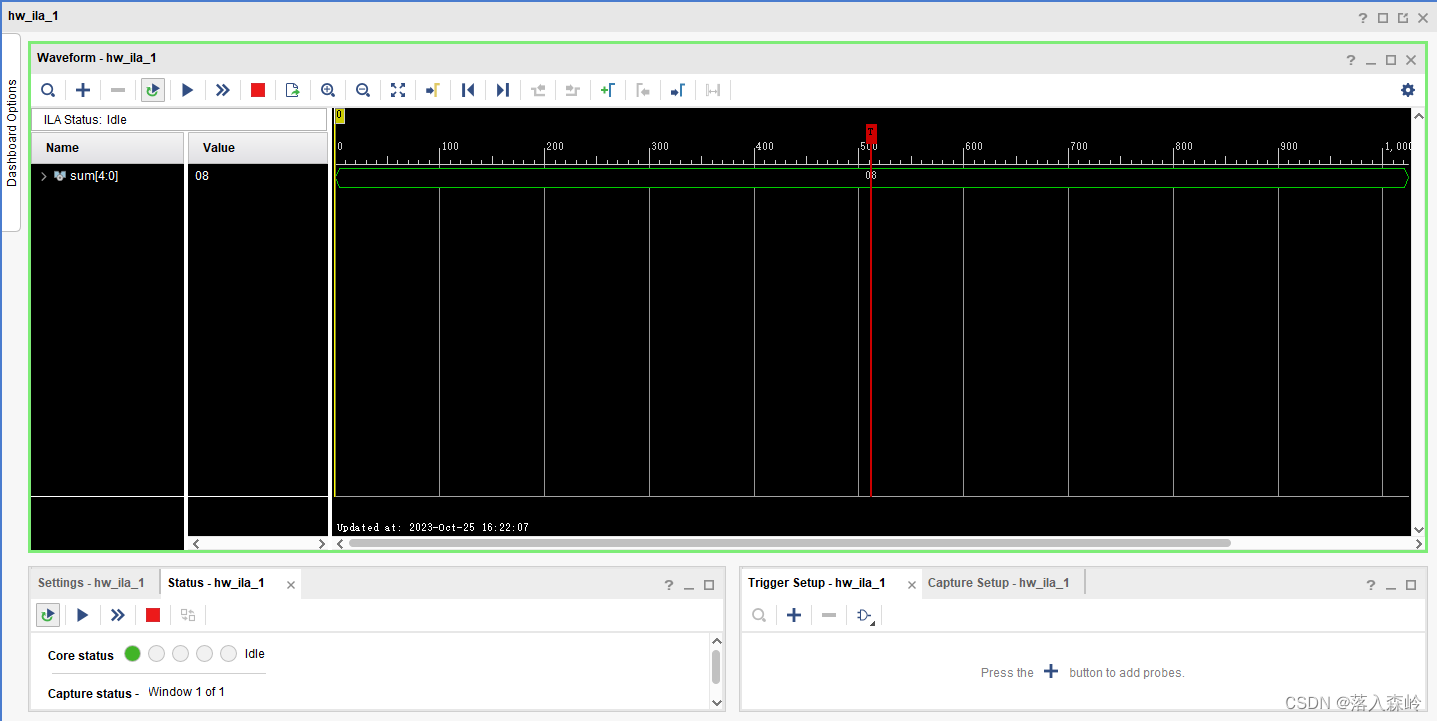

在这里设置探针数量为1,探针数据宽度为5

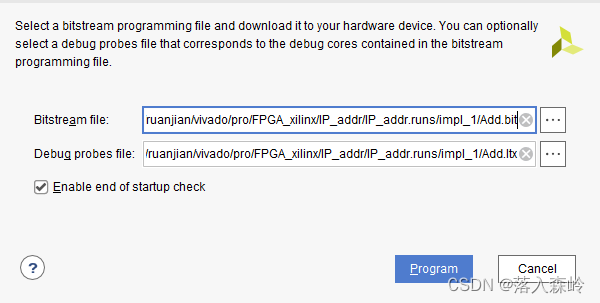

生成bit文件后,烧录bit流时,可以看到还有调试探针信息的.ltx文件

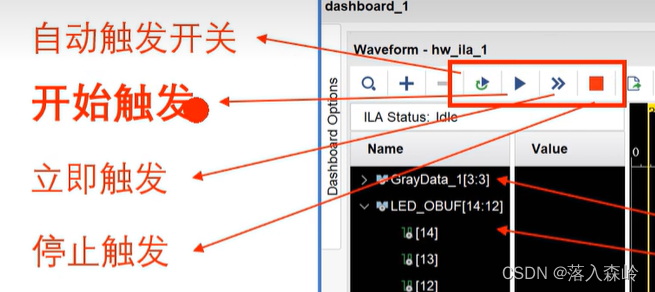

代码烧入到FPGA开发板后,立马弹出波形窗口,这些按钮的意义是:

波形图上可以看到sum的数值

代码如下:

module Add(

input clk,

input [7:0] sw,

output [3:0]an,

output dp,

output [6:0] seg

);

wire [3:0] a;

wire [3:0] b;

wire [4:0] sum;

assign a = sw[3:0];

assign b = sw[7:4];

add8 instance_add8 (

.A(a), // input wire [7 : 0] A

.B(b), // input wire [7 : 0] B

.CLK(clk), // input wire CLK

.S(sum) // output wire [8 : 0] S

);

seg7 instance_seg(

.clk(clk),

.a(a),

.b(b),

.s(sum),

.an(an),

.dp(dp),

.seg(seg)

);

ila_0 instance_ILA (

.clk(clk), // input wire clk

.probe0(sum) // input wire [4:0] probe0

);

endmodule

调用了seg7.v,其代码如下:

/*

数据a显示在第一个数码管上

数据b显示在第一个数码管上

数据s显示在第三、四个数码管上

*/

module seg7(

input clk,

//需要输入的数据

input [3:0]a,

input [3:0]b,

input [4:0]s,

output [3:0]an,

output dp,

output [6:0] seg

);

parameter T = 500000; //100MHZ-->200HZ

reg [19:0] cnt;

//动态扫描

reg [3:0] data;

reg [1:0] sel;

reg [3:0]an_r;

reg [6:0] seg_r;

always @(posedge clk) begin

if(cnt == T-1)

cnt <= 'b0;

else

cnt <= cnt+1'b1;

end

always @(posedge clk) begin

if(cnt == 'b0)

sel <= sel+1'b1;

else

sel <= sel;

if(sel == 2'b00) begin

data <= a;

an_r <= 4'b0111;

end

else if(sel == 2'b01) begin

data <= b;

an_r <= 4'b1011;

end

else if(sel == 2'b10)begin

data <= s[4];

an_r <= 4'b1101;

end

else begin

data <= s[3:0];

an_r <= 4'b1110;

end

end

always @(*) begin

case(data)

'h0: seg_r = 7'h40;

'h1: seg_r = 7'h79;

'h2: seg_r = 7'h24;

'h3: seg_r = 7'h30;

'h4: seg_r = 7'h19;

'h5: seg_r = 7'h12;

'h6: seg_r = 7'h02;

'h7: seg_r = 7'h78;

'h8: seg_r = 7'h00;

'h9: seg_r = 7'h10;

'hA: seg_r = 7'h08;

'hB: seg_r = 7'h03;

'hC: seg_r = 7'h46;

'hD: seg_r = 7'h21;

'hE: seg_r = 7'h06;

'hF: seg_r = 7'h0e;

default:seg_r = 7'h7f;

endcase

end

assign dp=1'b1;

assign an = an_r;

assign seg = seg_r;

endmodule

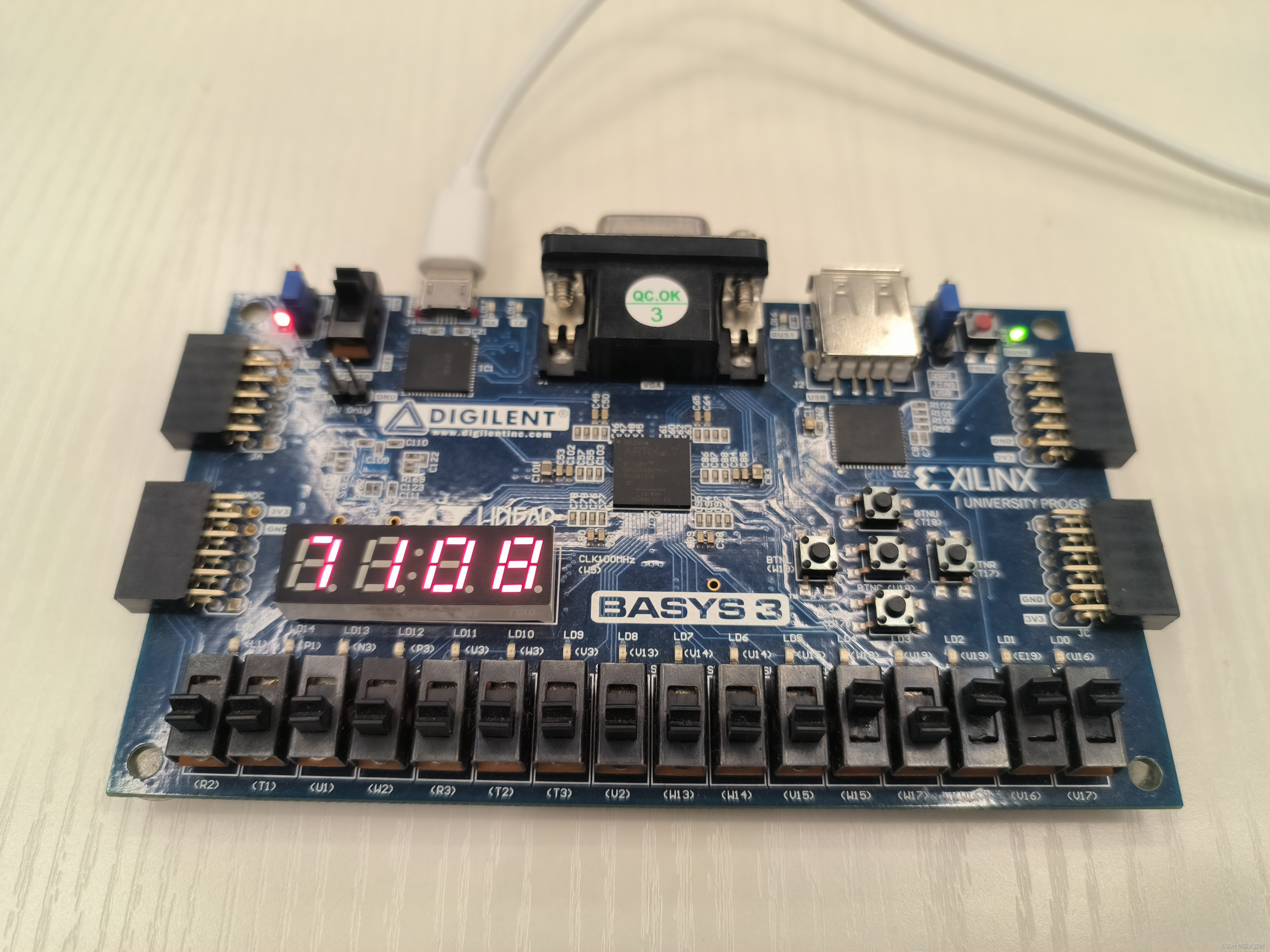

basys3 开发板显示

补充

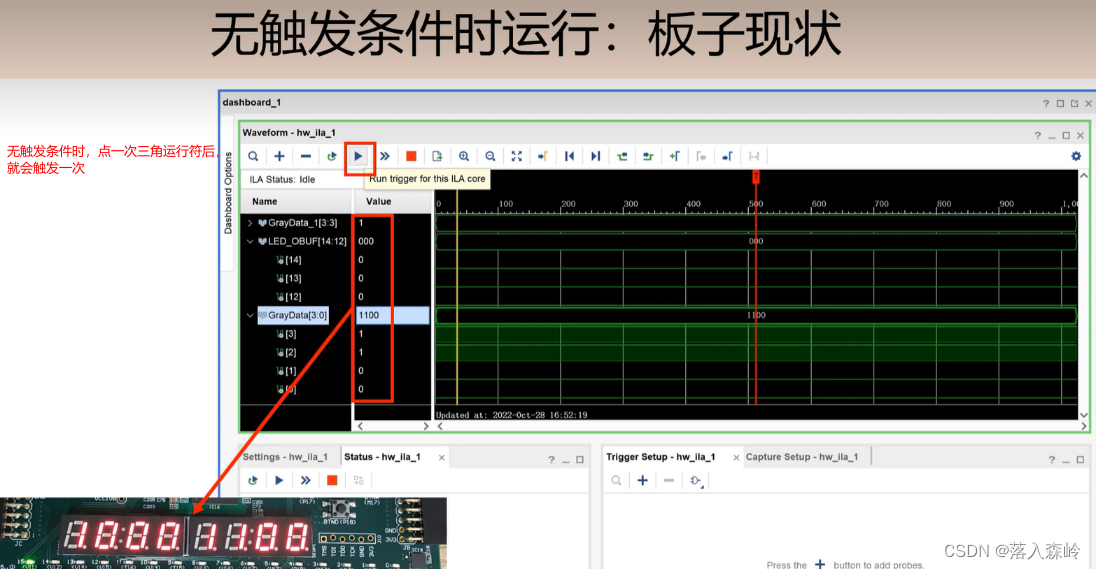

不设置触发条件/设置触发条件

766

766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?