软件版本:VIVADO2017.4

操作系统:WIN10 64bit

硬件平台:适用米联客 ZYNQ系列开发板

米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!!

19.1 概述

本课介绍一种基于PL端BRAM的方式,进行PS和PS之间的数据交互。适用于在PS和PL之间传输少量,地址不连续,且长度不规则的数据,比如,配置参数,变量,控制信息等。

19.2 基本原理

在本例程中,在PL端设计了1个4KB(位宽32,深度1024)的BRAM。首先,PS通过M_AXI_GP口向BRAM中1024个地址依次存入1024个32位的数据。PS每向BRAM完成写入1个32位数据后通过AXI GPIO输出1个上升沿信号,PL捕获上升沿后立即将PS写入的32位数据读出,然后加2,再存入原地址中。存储完成后,PL通过AXI GPIO向PS输入1个翻转信号,每翻转1次,AXI GPIO便向PS触发1次中断。PS触发中断后,再从BRAM中读出该数据,判断是否被加了2,若不一致,则报错。

以上过程重复1024次,便将BRAM的所有地址都进行了遍历。之后,则不断重复这个过程。

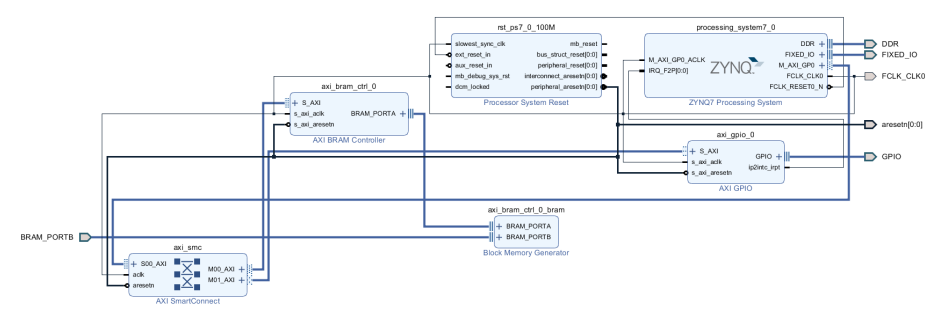

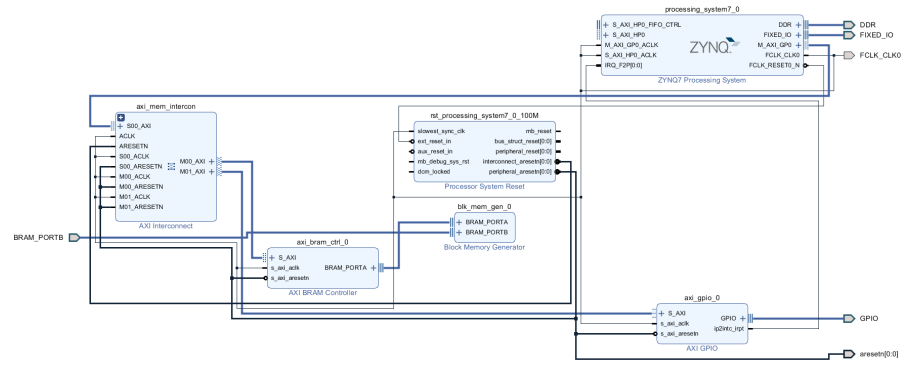

19.3 FPGA BD工程

VIVADO 2017.4开始可以使用axi_smc IP这个IP和AXI_interconnect IP功能类似,但是没有AXI_interconnect IP强大,在一些高带宽的要求下,还是要用AXI_interconnect IP,VIVADO2017.4自动连线会优先使用axi_smc IP。

以下是VIVADO 2016.4版本以前的自动联系,只会采用AXI_interconnect IP。所以从VIVADO2017.4开始我们多了axi_smc IP进行AXI4总线接口的互联。

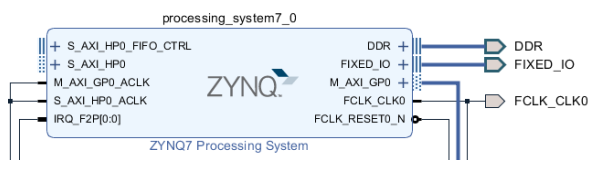

19.3.2 PS配置

PS的配置如下图所示。使能M_AXI_GP0口,将FCLK_CLK0设为100MHz,使能PL至PS的中断。

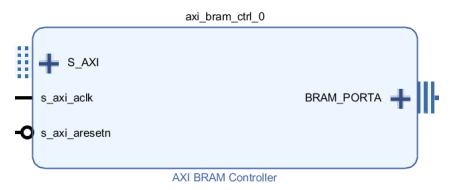

19.3.3 AXI BRAM Controller

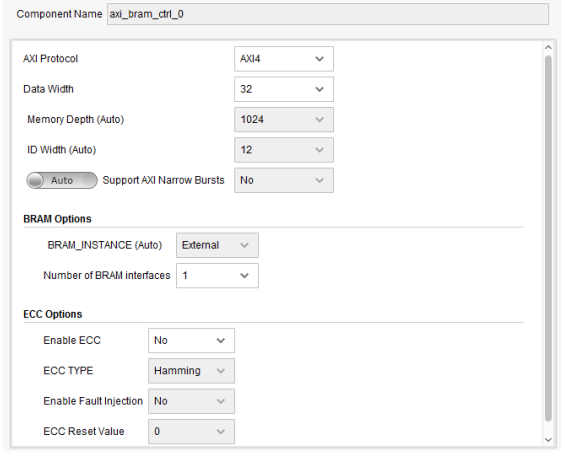

AXI BRAM Controller是本例程中的关键,该IP核连接PS的M_AXI_GP0口和BRAM,完成AXI接口至BRAM接口的转换。设置如下图所示。

19.3.4 Block Memory Generator

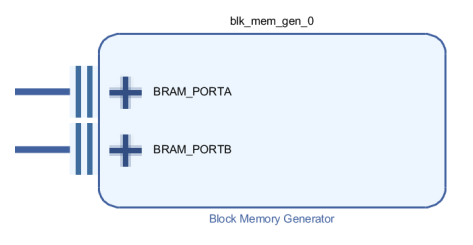

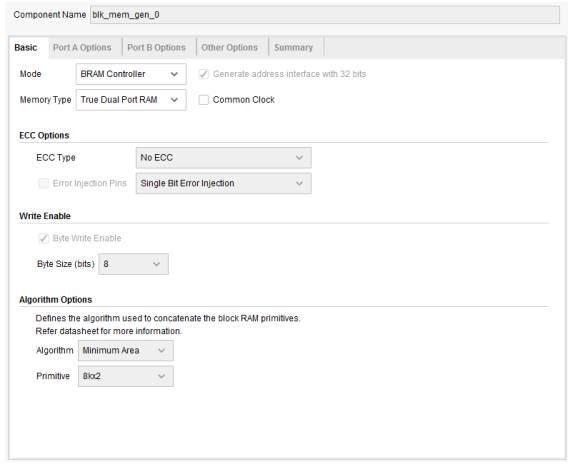

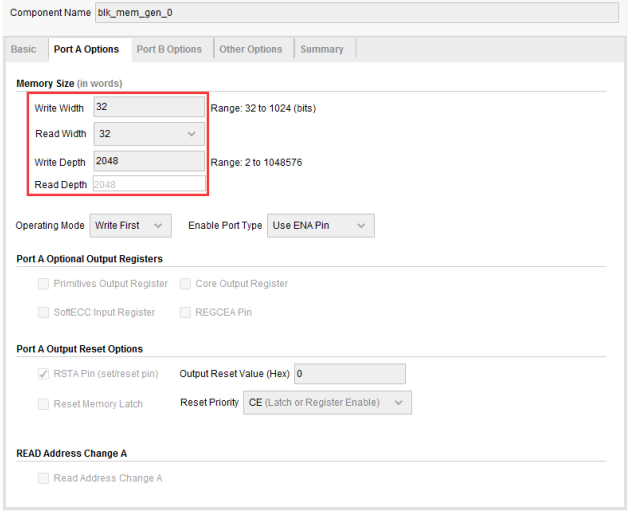

添加BRAM,将BRAM设置为双口RAM,将PORTA与AXI BRAM Controller连接,PS通过PORTA读写BRAM,另外,将PORTB引出至外部模块,PL通过PORTB读写BRAM。如下图所示。

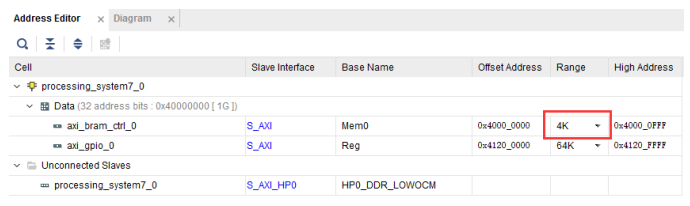

由于要与AXI BRAM Controller进行连接,BRAM接口的位宽固定为32位。BRAM的深度无法在该IP中进行设置,需要在所有模块连接完成后,在Address Editor里对AXI BRAM Controller的地址范围进行设置,本例程中设置为4KB。该地址范围即对应BRAM的深度,如下图所示。

例如,4KB=32bit×1024,因此BRAM的深度为1024。如下图所示。

去掉Enable Safety Circuit

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3828

3828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?