软件版本:VIVADO2017.4

操作系统:WIN10 64bit

硬件平台:适用米联客 ZYNQ系列开发板

米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!!

24.1 概述

MT9V034是美国Aptina公司推出的一款宽动态、低照度、具有全局快门的一款相机,常用于机器视觉领域的开发。本节课程将为大家讲解如何在ZYNQ平台下面驱动MT9V034,讲解了使用IIC对摄像头的分辨率进行修改。

MT9V034提供的测试历程输出显示分辨率是640X480。

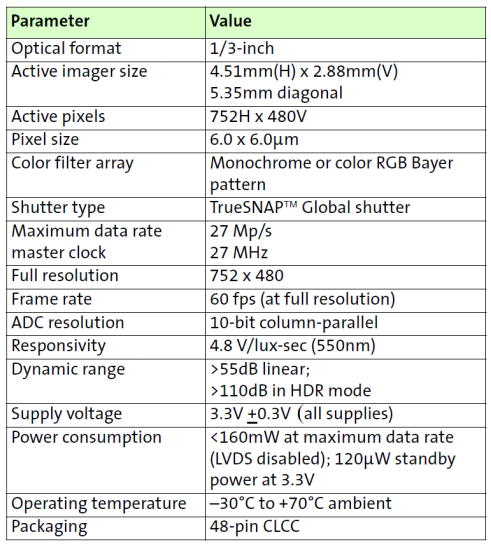

24.2 MT9V034摄像头参数

MT9V034作为机器视觉领域的一款人气sensor,由于其宽动态、低照度、成像质量优秀等原因得以大量的采用。在我们的提供的源文件夹当中,包含了它的产品技术手册,MT9V034的主要参数如下表所示:

从表格中我们可以看到,MT9V034全分辨率输出752x480@60FPS,最大像素时钟27MHZ(典型值实际为24MHZ),10bit数据输出,功耗120uw(3.3V电源)。

MT9V034的驱动十分简单,如果不需要指定分辨率输出,以全分辨率752x480分辨率输出则不需要配置内部的寄存器,Sensor内部将以默认的配置输出。因此,在设计过程中,可以直接省略寄存器配置这一步,直接设计采集部分时序即可。但是,在实际应用中,有时候可能要对sensor的寄存器做一些相应的改动,因此本章加入ZYNQ IP自带的IIC接口,对sensor寄存器进行修改。为了验证IIC对寄存器配置有效,我们这里测试设置MT9V034输出的分辨率是640X480。

24.3 MT9V034图像采集传输系统

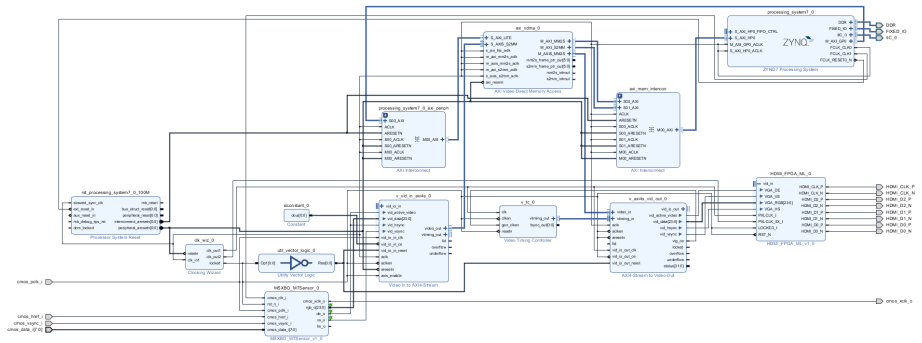

本章的框架大体思路是:MT9V034以默认分辨率(752x480@60FPS)采集输出,为了将采集的数据送至VDMA缓存,需要将视频流数据转换为AXI4-Stream信号,因此需要一个Video in to AXI4-stream IP完成这一功能,VDMA缓存之后,因为MT9V034输出的是一个不规则的分辨率,因此我们采取在1280x720图像尺寸的基础上截取640x480的区域来显示MT9V034采集的图像,这个功能是可以由PS端控制,最后由AXI4-Stream to video out重新由AXI信号转换为显示所需的视频流数据,这个IP所需要的时钟和时序分别由PLL和VTC提供。整体的电路框架如下图所示:

24.4 FPGA工程 IP配置

24.4.1采集输入IP

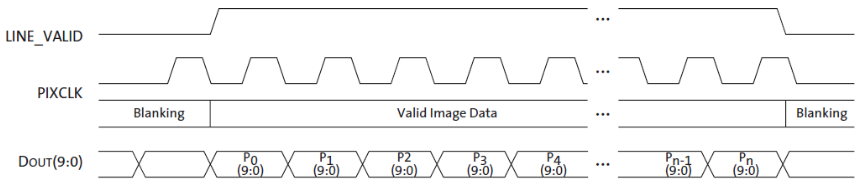

24.4.1.1 MT9V034时序

在MT9V034的数据手册中,找到其数据输出的时序描述:

MT9V034的数据输出与像素时钟pclk同步输出,当LV(实际为HS,MT公司将其称为Line Vaild信号)输出为高的时候,数据将在每个pclk同步输出。其时序图如下图所示:

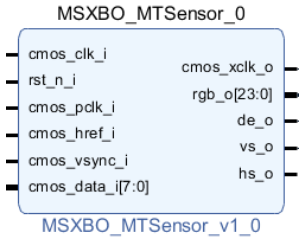

24.6.1.2 MTSensor 自定义IP

MT9V034是属于输出灰度的Sensor(另外有输出Bayer的sensor),因此,将采集部分输入部分的8bit灰度数据用拼接为了24bit的数据即可。

接口说明

| 接口 |

I/O |

说明 |

| cmos_clk_i |

I |

输入时钟,通常接24MHZ 或者25MHZ |

| rst_n_i |

I |

低电平复位 |

| cmos_pclk_i |

I |

摄像头时钟输入时钟 |

| cmos_href_i |

I |

摄像头行同步输入, 高电平代表行数据有效 |

| cmos_vsyns_i |

I |

摄像头场同步输入,上升沿代表场同步开始 |

| cmos_data[7:0] |

I |

摄像头数据输入 |

| cmos_xclk_o |

O |

摄像头工作,通常直接把cmos_clk_i连接到cmos_xclk_o |

| rgb_o[23:0] |

O |

RGB输出数据 |

| de |

O |

保留,暂时不配置 |

| hs_o |

O |

输出的行数据有效 |

| vs_o |

O |

输出的场同步信号 |

MSXBO_MTSensor IP源码

| `timescale 1ns / 1ps // Company: cz123 milinker // Engineer: tjy // bbs:http://www.osrc.cn // taobao:http://osrc.taobao.com // Create Date: 2019/02/27 22:09:55 // Design Name: MSXBO_MTSensor // Module Name: MSXBO_MTSensor // Project Name: MSXBO_MTSensor // Copyright: msxbo Copyright (c) 2019 // Revision 0.01 - File Created // Additional Comments: // module MSXBO_MTSensor( input cmos_clk_i,//cmos senseor clock. input rst_n_i,//system reset.active low. input cmos_pclk_i,//input pixel clock. input cmos_href_i,//input pixel hs signal. input cmos_vsync_i,//input pixel vs signal. input [7:0]cmos_data_i,//data. output cmos_xclk_o,//output clock to cmos sensor. output [23:0] rgb_o, output de_o, output vs_o, output hs_o );

assign cmos_xclk_o = cmos_clk_i; reg cmos_href_r; reg cmos_vsync_r; reg [7:0]cmos_data_r; |

本文档介绍了如何在ZYNQ SoC平台上利用AXI VDMA驱动MT9V034摄像头,详细阐述了摄像头参数、采集传输系统、FPGA IP配置以及PS部分的IIC驱动,最终通过测试验证了640x480分辨率的图像采集成功。

本文档介绍了如何在ZYNQ SoC平台上利用AXI VDMA驱动MT9V034摄像头,详细阐述了摄像头参数、采集传输系统、FPGA IP配置以及PS部分的IIC驱动,最终通过测试验证了640x480分辨率的图像采集成功。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2600

2600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?