一、前言

什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。

周期约束就是告诉软件我们的时钟周期是多少,让它PAR后要保证在这样的时钟周期内时序不违规。大多数的约束都是周期约束,因为时序约束约的最多是时钟。

两个概念

- 发起端/发起寄存器/发起时钟/发起沿:指的是产生数据的源端

- 接收端/接收寄存器/捕获时钟/捕获沿:指的是接收数据的目的端

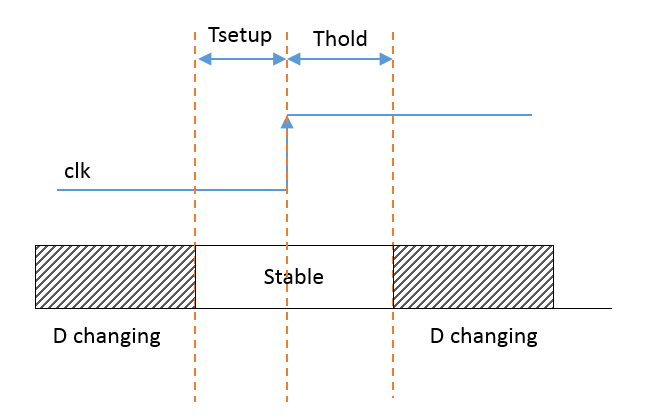

二、建立/保持时间

- 在clk上升沿到来之前,数据提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间;

- 在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间。

三、时序路径与时序模型

3.1 时序路径

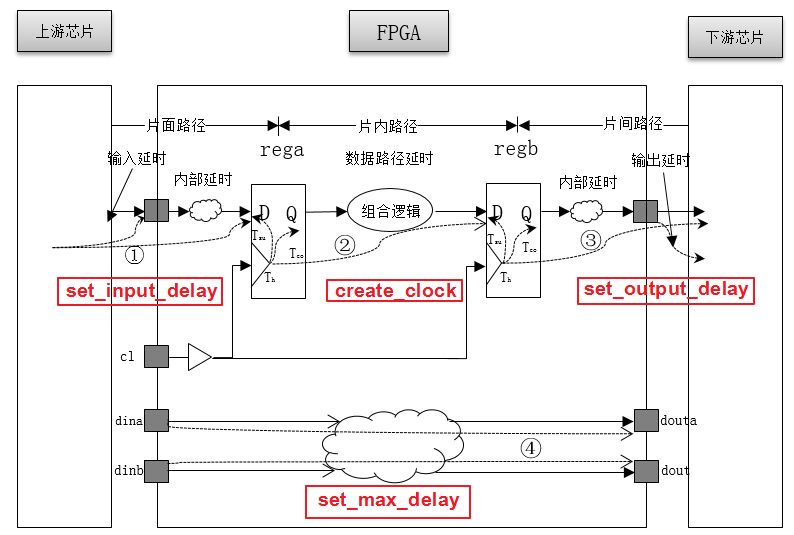

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

对于所有的时序路径,要明确其起点和终点,这4类时序路径的起点和终点分别如下表。

其中对于路径②是时序约束中重点关注的对象。

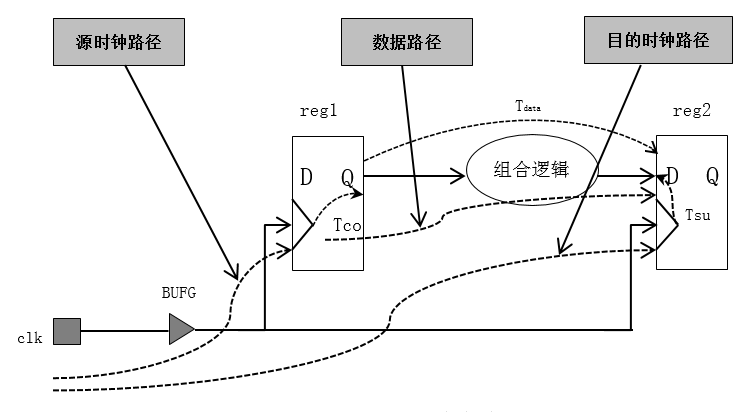

3.2 时序模型

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

该时序模型的要求为:

Tclk ≥ Tco + Tlogic + Trouting + Tsu - Tskew (1)

Tdata = Tco + Tlogic + Trouting

在时钟沿到达之后,数据要保持Thold的时间,因此,要满足:

Tco + Tlogic + Trouting ≥ Tskew + Thold (2)

其中,Tco为发端寄存器时钟到输出时间;Tlogic为组合逻辑延迟;Trouting为两级寄存器之间的布线延迟;Tsu为收端寄存器建立时间;Thold为保持时间;Tskew为两级寄存器的时钟歪斜,其值等于时钟同边沿到达两个寄存器时钟端口的时间差;Tclk为系统所能达到的最小时钟周期。

四、其他

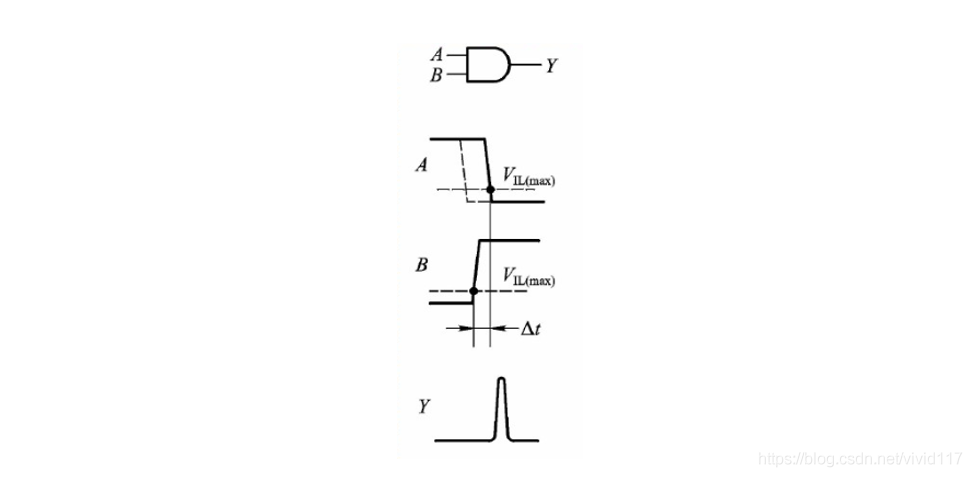

4.1 竞争冒险

两个输入信号同时向相反方向的逻辑电平跳变的现象(即一个由1- > 0, 另一个从0 -> 1),称为竞争。

因竞争导致在输出端可能产生尖峰脉冲的现象,称为冒险。

通俗一点的说,信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险。

竞争表现在输出波形上,则是出现0电平或者1电平的尖峰,称 “毛刺”。

如何消除?

1.加滤波电容,消除毛刺的影响;2.加选通信号,避开毛刺;3.增加冗余项,消除逻辑冒险。

4.2 恢复时间/移除时间

异步复位电路中:

1. 异步复位信号释放(对低电平有效的复位来说就是上跳沿)与紧跟其后的第一个时钟有效沿之间,有一个必须间隔的最小时间称为Trecovery(recovery time,恢复时间)。

举例:如果异步复位释放后马上来了一个时钟有效边沿,触发器输出端的值将是不确定的,可能是高电平也可能是低电平,可能处于高低电平之间,也可能处于震荡状态,这就是亚稳态。如上所示。

2. 时钟有效沿与紧跟其后的异步复位信号释放之间所必须的最小时间称为tremoval(removal time消除时间)。小于这个时间,则触发器的输出端的值将是不确定的,可能是高电平,可能是低电平,可能处于高低电平之间,也可能处于震荡状态,并且在未知的时刻会固定到高电平或低电平。这种状态就称为亚稳态。

举例:如果时钟有效沿到来后,马上来了异步复位信号的上升沿(复位信号释放)触发器处于亚稳态。如上图所示。

参考:https://blog.csdn.net/dongdongnihao_/article/details/79827076

6999

6999

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?