chapter 0: 开发工具和环境

开发环境:ISE Design suite 14.7 WebPack(x64)

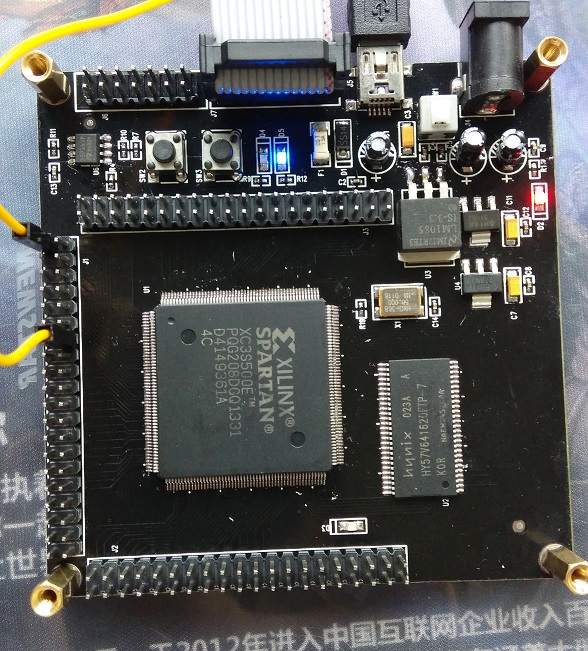

目标板:xilinx spartan-3e fpga 最小系统开发板 (主芯片:Spartan-3E系列XC3S500PQE208)

下载器:xilinx platform cable usb

chapter 1: 创建工程

(1)在桌面快捷方式或开始→所有程序→Xilinx Design Tools→Xilinx ISE Design Suite 14.7→ISE Design Tools中打开64-bit Project Navigator。

(2)单击New Project...出现下图所示对话框。填写上项目名称,选择好项目存储路径,然后单击下一步。

(3)出现下图的对话框,主要设置Family、Device和Package三个选项,由于现在所使用的芯片是Spartan XC3S500E PQG208,所以按下图的设置。

(4)单击Next,确认信息,然后单击Finish。

chapter 2: 编写代码

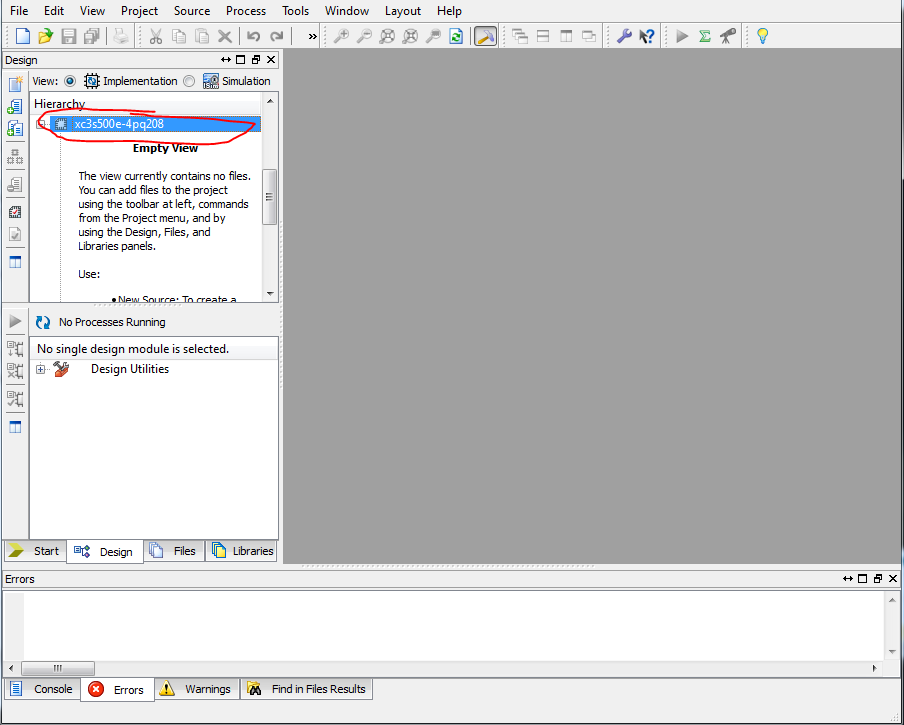

(1)在顶层,如图中红色所示的地方右键,选择New source

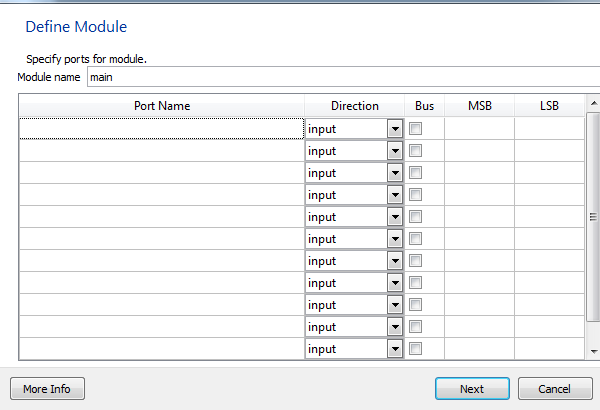

(2)出现下面的对话框,选择Verilog Module类型,然后输入文件名。单击下一步。

(3)继续单击下一步,不在这里设置io。

(4)单击Finish完成创建文件。

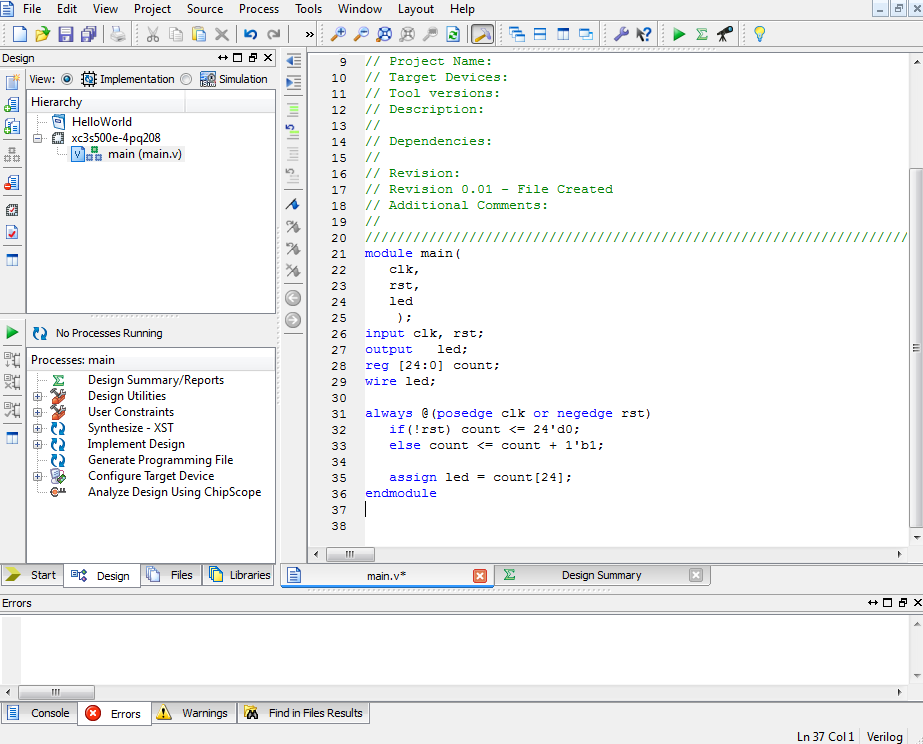

(5)默认会帮我们写一些代码

(6)修改代码,修改后的代码功能是让d_out在1秒内高低电平变换一次。

(7)添加约束文件,同样也是右键选择New source

(8)选择类型,输入文件名,然后单击Next,出现下面的界面,单击Finish

(9)添加约束代码(这里要根据开发板的资料来选择,时钟和复位一般是固定的)

chapter 3: 配置编译

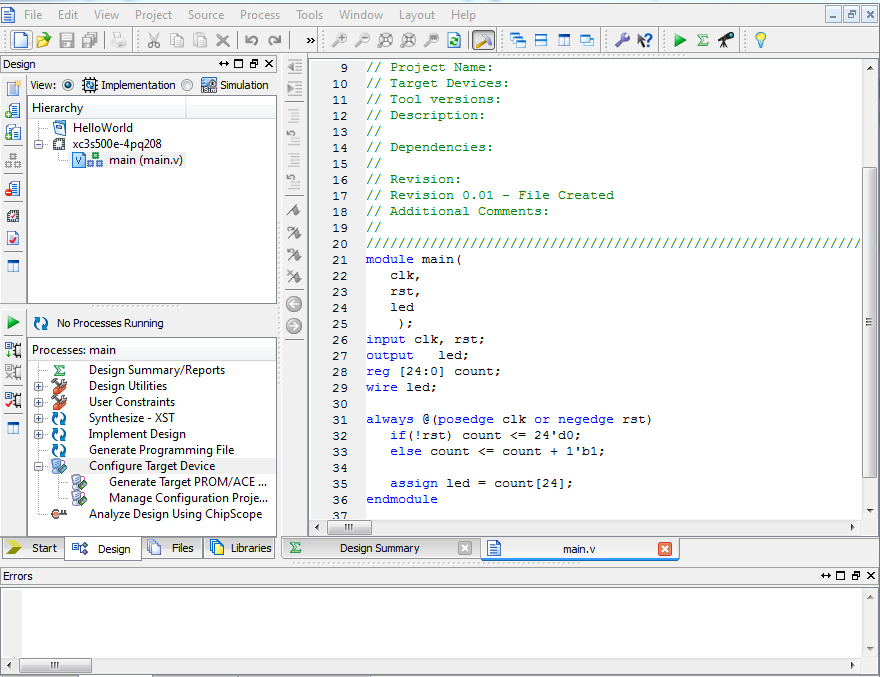

(1)在Design栏选中main.v,下面会出现如图的几个选项,双击Configure Target Device,开始编译配置

(2)弹出对话框,单击OK

(3)弹出如下对话框,双击Create ROM File

(4)双击后弹出下面的对话框,按图中的顺序依次选择各个选项。(根据开发板资料来选择具体配置)

(5)完成后会弹出下面的提示框,选择OK

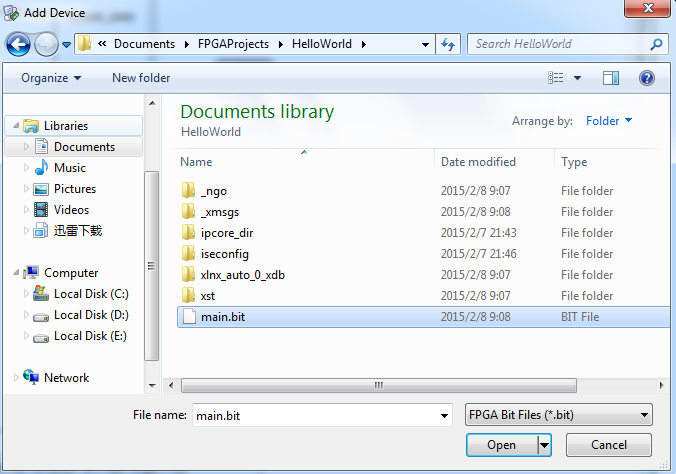

(6)在弹出的对话框里选择前面编译产生的bit文件

(7)又弹出一个对话框,这次选择No

(8)选择OK

(9)双击左下的Generate File ...开始生成mcs文件

chapter 4: 烧写程序

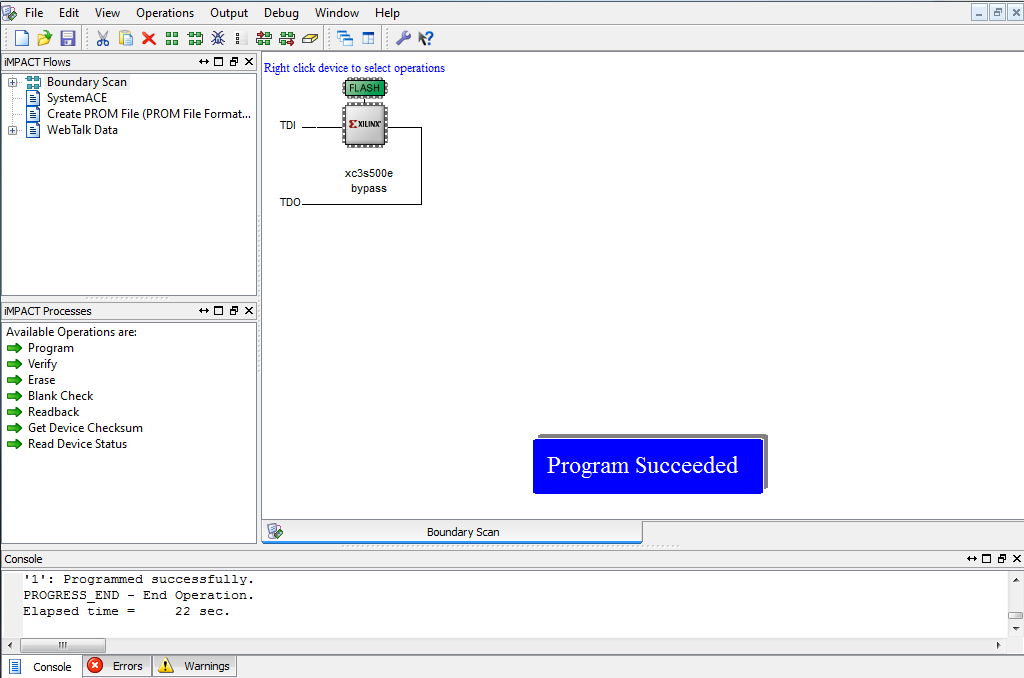

(1)双击,左上的Boundary Scan

(2)单击红色标注的按钮

(3)选择No,然后在弹出的对话框,选择OK

(4)双击蓝色虚线表示的SPI BPI符号

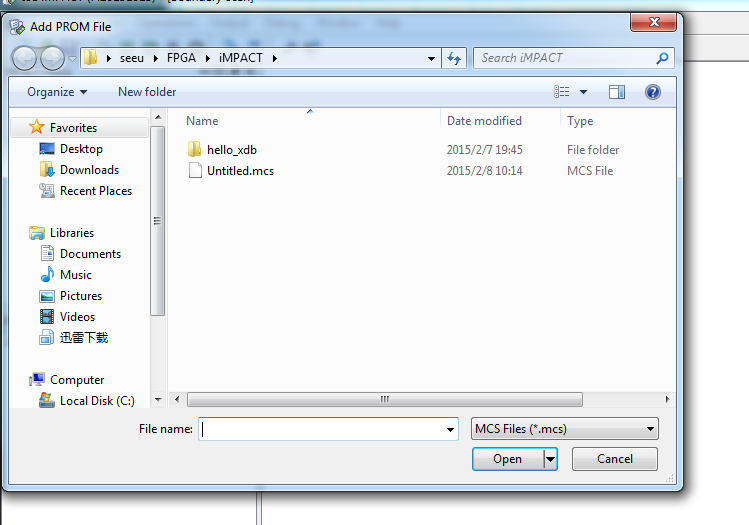

(5)在弹出的对话框中选择前面生成好的mcs文件

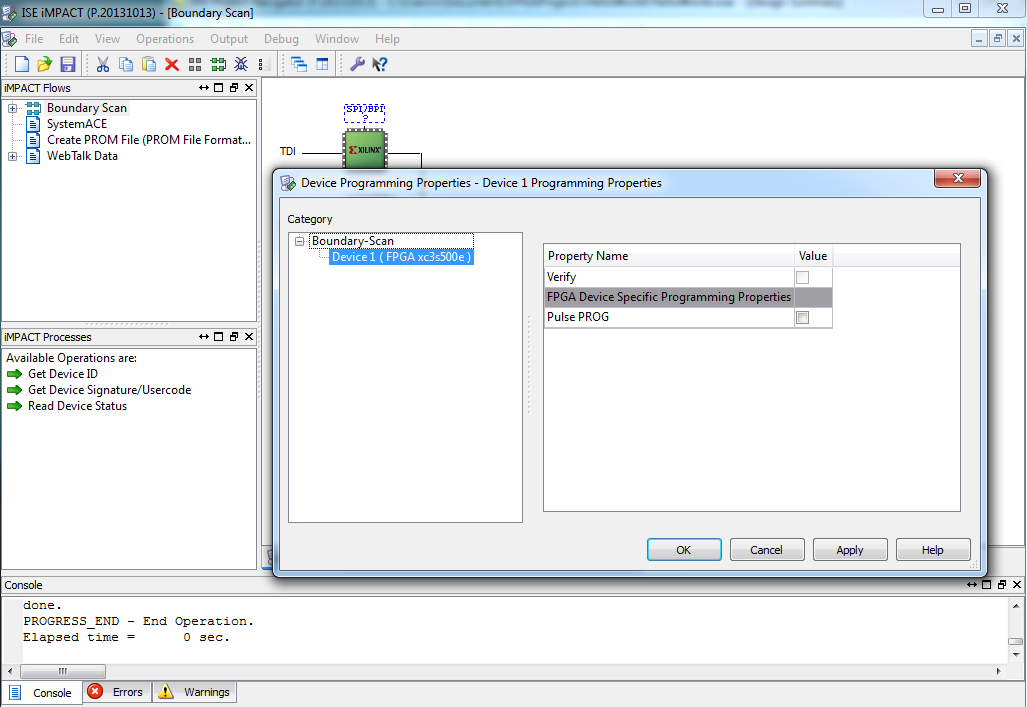

(6)选择如下图的配置,然后单击OK(配置要根据不同的ROM来选择,一般开发板所带资料里面会有)

(7)左键单击选中下图绿色所示的SPI部分,然后右键单击,在弹出的菜单里选择Program

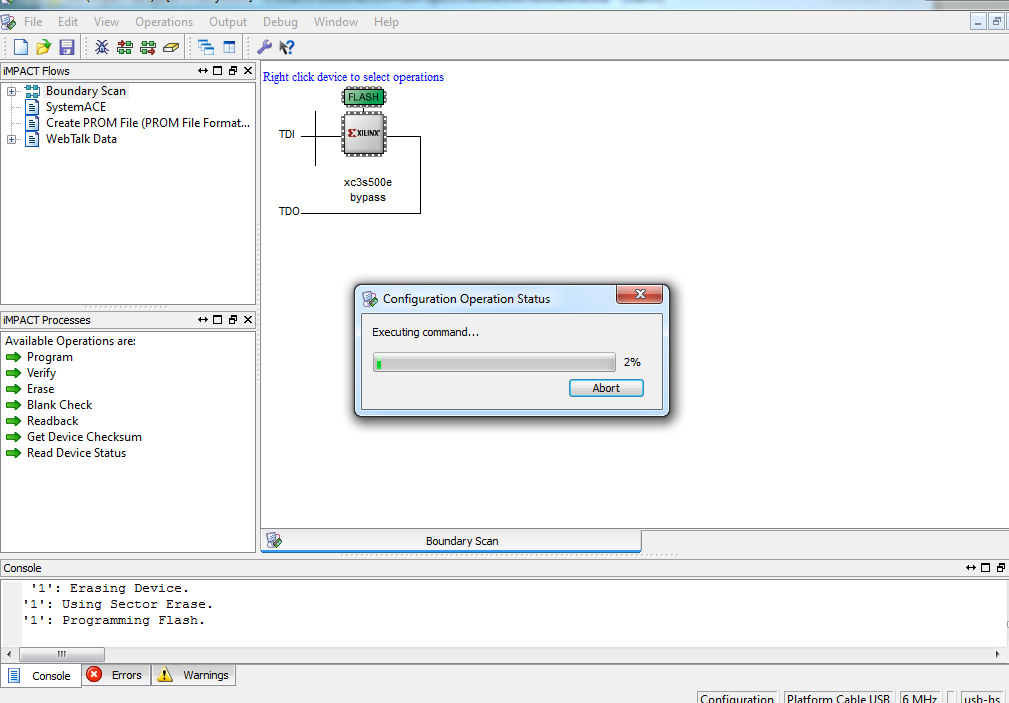

(8)下载中。。。

(9)下载结束,出现提示

完成:

小灯在闪烁,由于设置输出到P2口,所以根据开发板电路图将P2连接到LED对应的管脚。

752

752

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?