目录

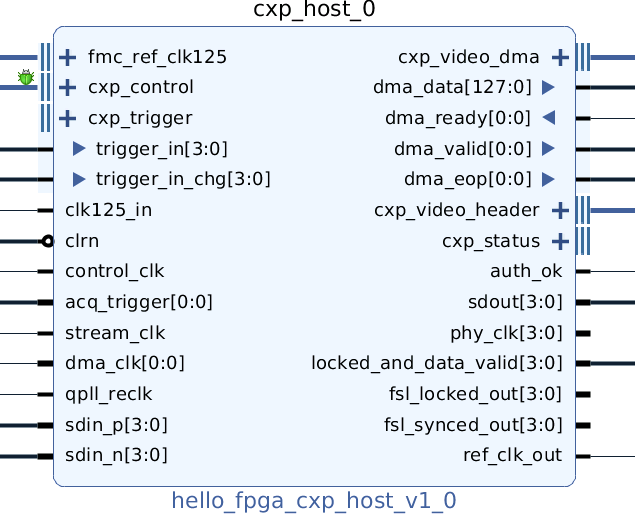

图 1‑4 CXP HOST PCIe Block Design 5

图 1‑7 KC705搭载Hello-FPGA CoaXPress 2.0 FMC子卡 7

说明

本手册针对Helllo-FPGA的CoaXPress 2.0 HOST FPGA IP Core PCIe demo工程,用于演示IP的使用方法、配置流程,使用上位机采集到相机真实的图像并在界面上完成显示。通过该demo提供了1个较为完整的系统级演示,方便用户更加直观的评估IP

Demo 特点功能如下:

- Demo 分为FPGA工程与Windows 驱动及其应用程序,利用XDMA搭建PCIe接口,并利用PCIe接口及其驱动,实现对CoaXPress HOST IP的配置、数据读取。

- 当前代码适用于Xilinx KC705 评估板,其它评估板请联系我们咨询;

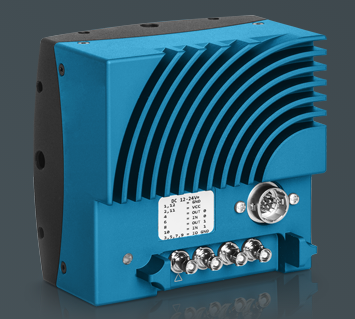

- 使用KC705 FMC HPC接口,搭载Hello-FPGA 4 channel receiver 子卡;

- 使用EoSens® 2.0CXP2 系列相机进行演示;

- 使用VIVADO 2017.3(我们测试了2019.1和2020.2,PCIe IP使用有问题,暂时仅支持2017.3)、Windows10台式计算机;

- VIVADO 工程使用block design形式提供;

- LINK配置为1个相机,4个LINK,设备发现阶段使用0x38配置,即3.125Gbps,设备采集阶段使用0x48配置,即6.125Gbp,如果相机不支持对应速率,请修改代码后进行测试,请注意KC705不支持10Gbps和12.5Gbps速率,KU/ZU等支持;

- 使用vs2022或者其它版本调试windows驱动与应用程序;

- IP使用网表形式提供,参数无法修改,如需不同LINK配置,请联系Info@hello-fpga ;

- 其它相关IP使用加密方式提供;

文件列表:

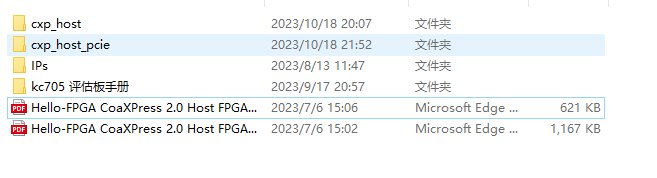

顶层文件夹

cxp_host_pcie 示例FPGA工程

IPs 工程依赖的IP文件

Kc705评估板手册

user manual

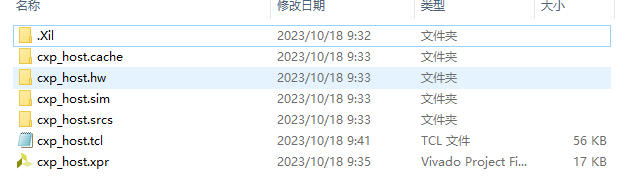

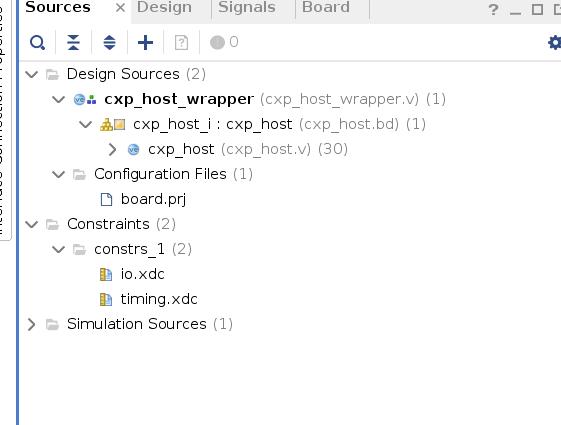

下图展示了cxp_host_pcie内部的目录结构,直接使用VIVADO 2017.3打开 *.xpr工程文件即可。

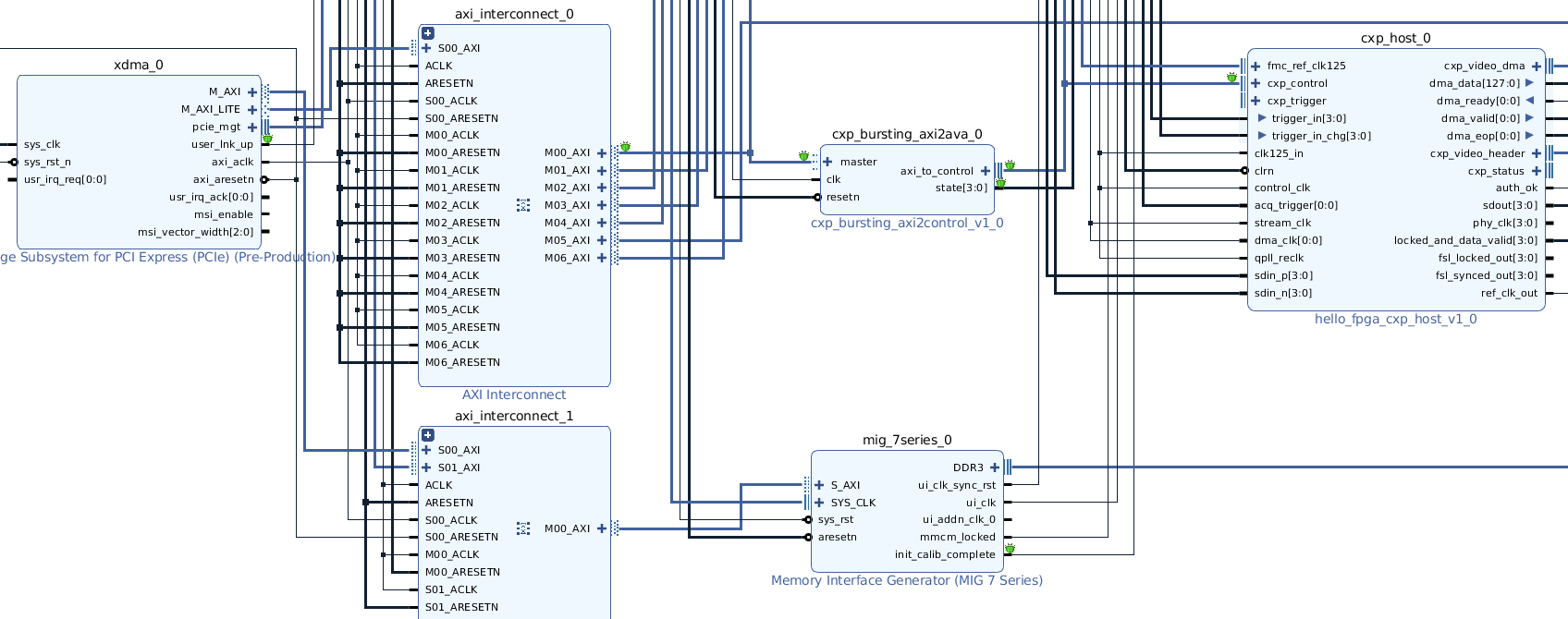

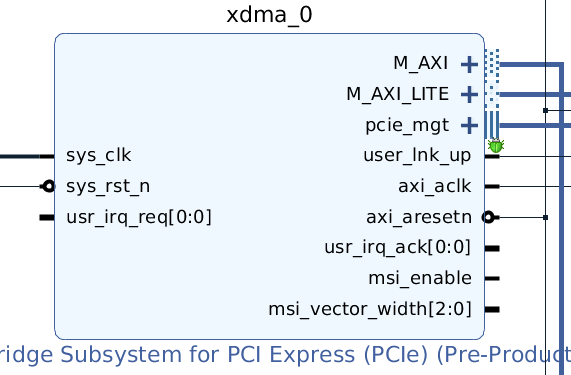

利用XDMA Subsystem 构建PCIe 及其DMA控制器,MIG DDR作为板上缓存,用于缓存高速图像数据并完成DMA操作,AXI Interconnect作为系统总线树,CoaXPress IP以及MIG等均挂载在总线树上,方便XDMA灵活方位其内存完成寄存器读写、DMA读写操作。

图 ‑4 CXP HOST PCIe Block Design

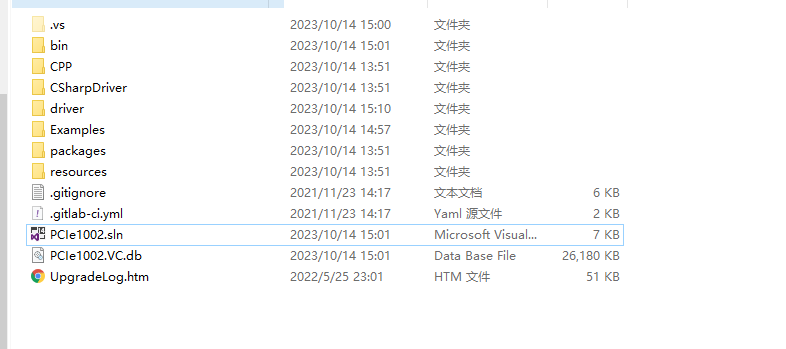

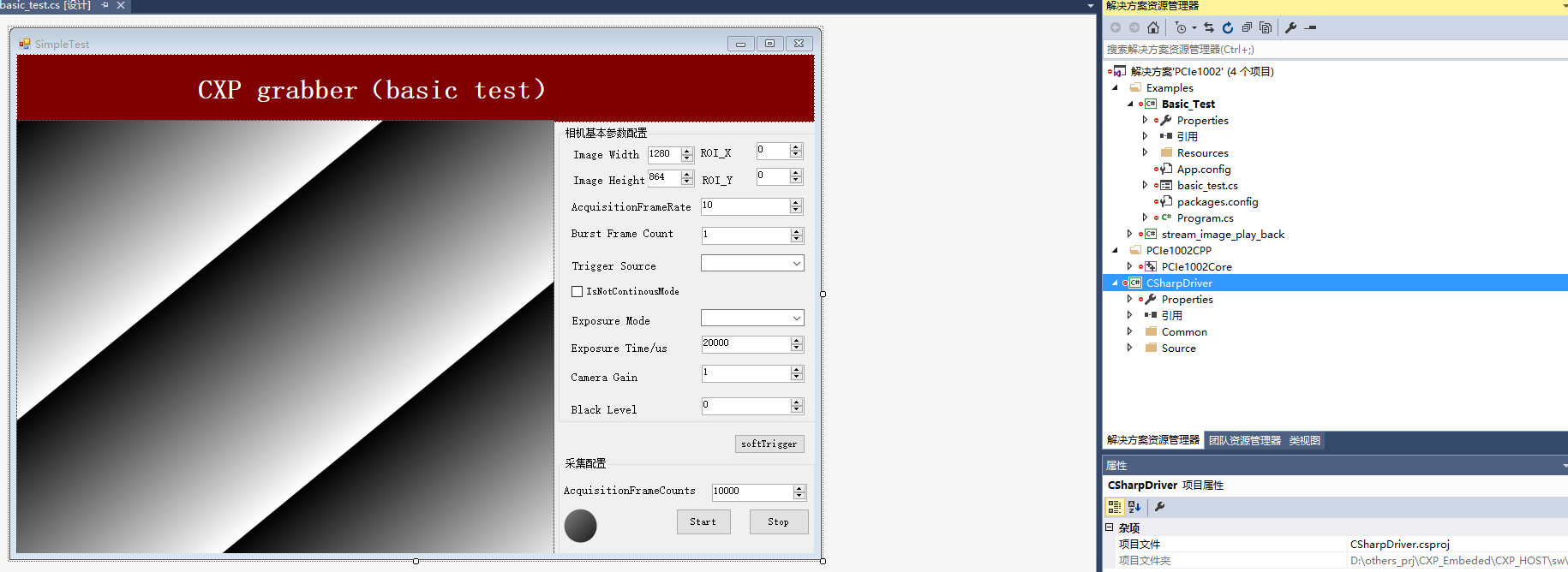

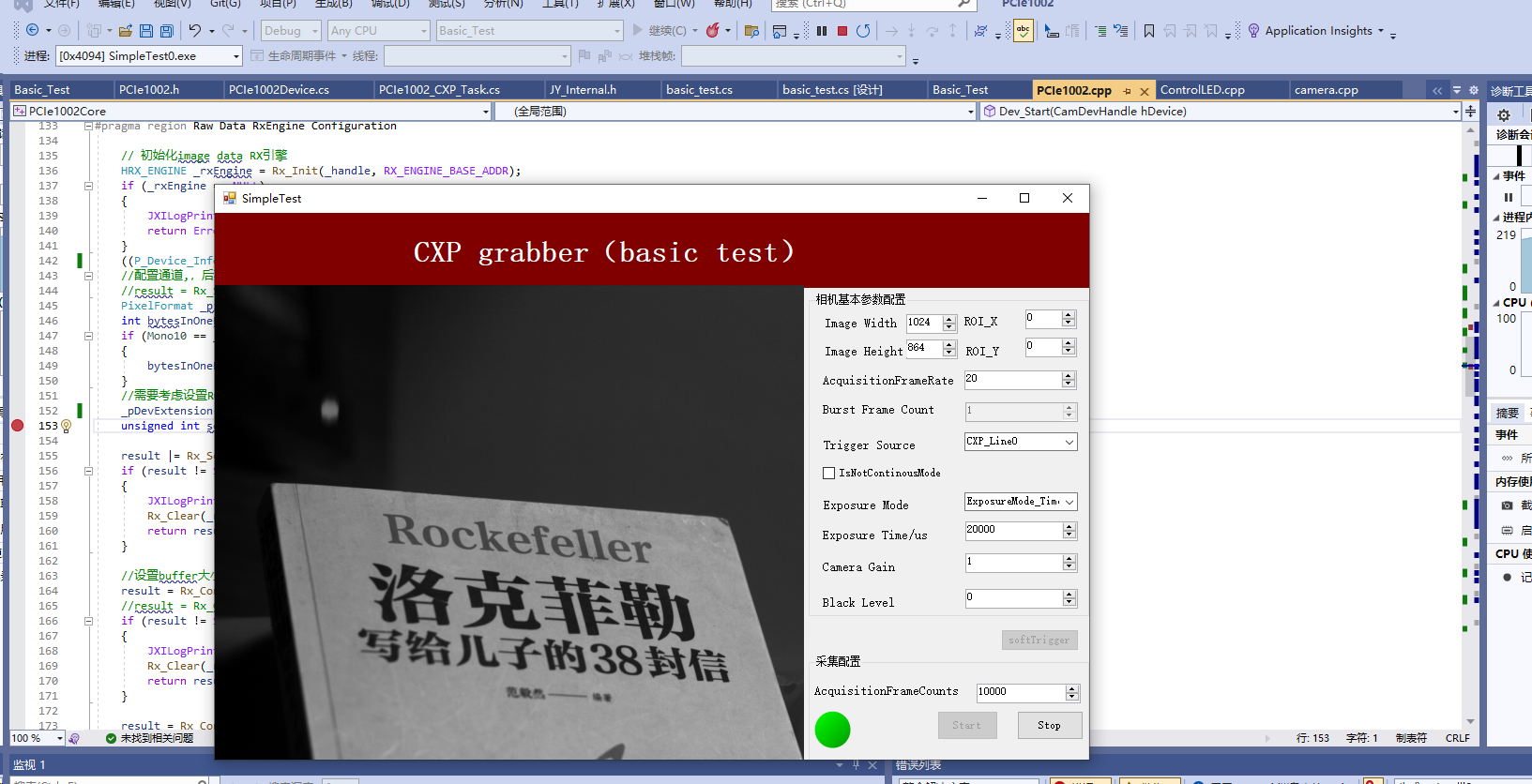

VS工程采用C++面向过程驱动、C#面向对象驱动以及C# 应用程序组成,C++驱动负责具体功能实现,C# 应用程序最终通过C# 驱动调用C++ API实现相机的连接、配置、图像读取、图像显示等功能,用于用户更加直观的评估IP。

图 ‑7 KC705搭载Hello-FPGA CoaXPress 2.0 FMC子卡

| 速率配置 | Downlink速率 | 最大速率 |

| 0x28 | 1.250 Gbps | 1.000 Gbps |

| 0x30 | 2.500 Gbps | 2.000 Gbps |

| 0x38 | 3.125 Gbps | 2.500 Gbps |

| 0x40 | 5.000 Gbps | 4.000 Gbps |

| 0x48 | 6.250 Gbps | 5.000 Gbps |

| 0x50 (1) | 10.000 Gbps | 8.000 Gbps |

| 0x58 (1) | 12.500 Gbps | 10.000 Gbp |

设备连接

设备包含:

- Camera,camera 请按照厂商要求连接电源,FMC子板提供了对应POE功能,但是KC705开发板供电能力不足,因此依然需要连接相机电源;

- Camera 与CXP HOST FMC子卡连接,请注意LINK 序号一一对应,使用CXP同轴线缆完成连接;

- Demo使用JTAG启动模式,PCIe lane size对应选择X8模式;

- Demo需要将KC705插入台式计算机的PCIe插槽内,注意KC705不是标准3U板卡,需要注意其机械尺寸,使用合适的机箱;

VIVADO FPGA工程

使用VIVADO 2020.2 打开。

如下图所示,系统使用Xilinx XDMA控制器作为PCIe与DMA核心,使用PCIe Gen2x8配置。

调试说明

连接好硬件后,烧录bit文件,安装PCIe内核驱动,然后重启计算机,打开VS工程重新编译,运行basic test C#应用程序,然后即可看到相机连接成功、拍摄图像正常。Demo软件使用源码方式提供,用户可以任意修改参数完成调试。

122

122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?