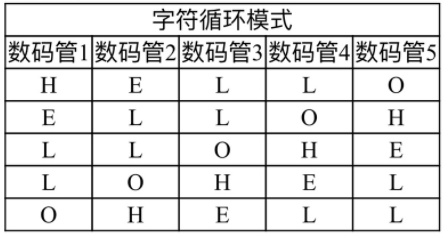

名称:基于FPGA的利用DE2-115实验平台上的5个7段的数码管循环显示英文“ HELLO”VHDL代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:VHDL

代码功能:

利用DE2-115实验平台上的5个7段的数码管循环显示英文“ HELLO”。(提示:可以先考虑如何在1个7

段数码管上显示字母H、E、L、O,再利用5选1多路选择器来完成)

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

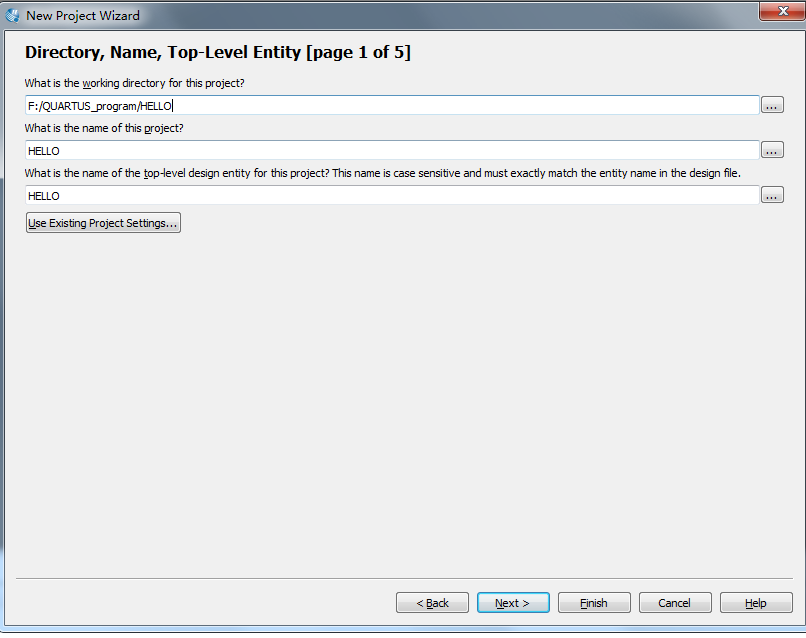

1. 新建工程

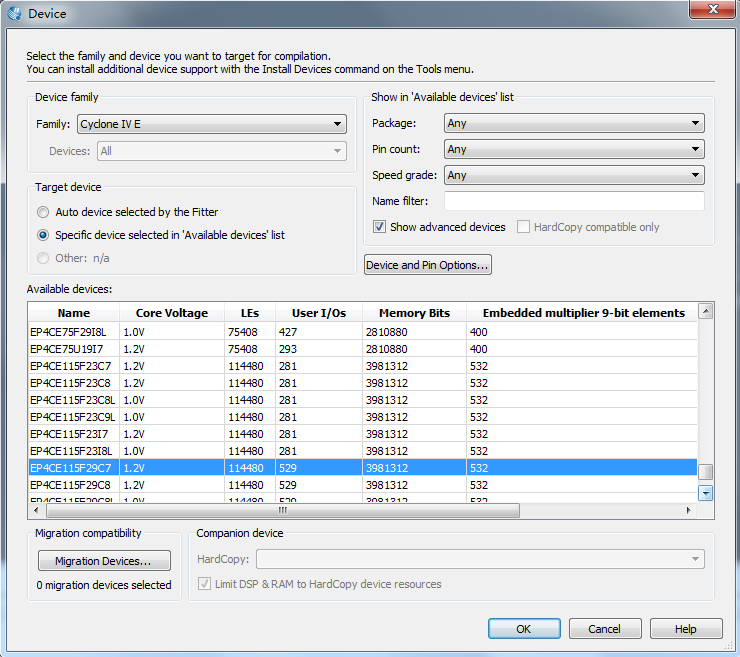

2. 选择芯片型号

3. 工程文件

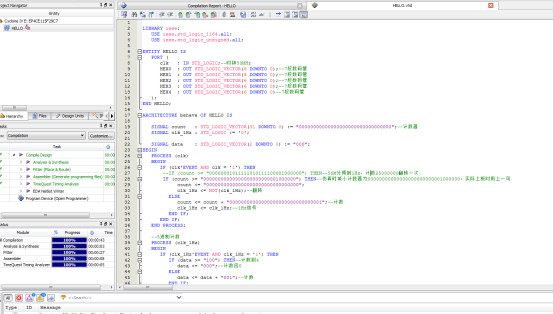

4. 程序文件

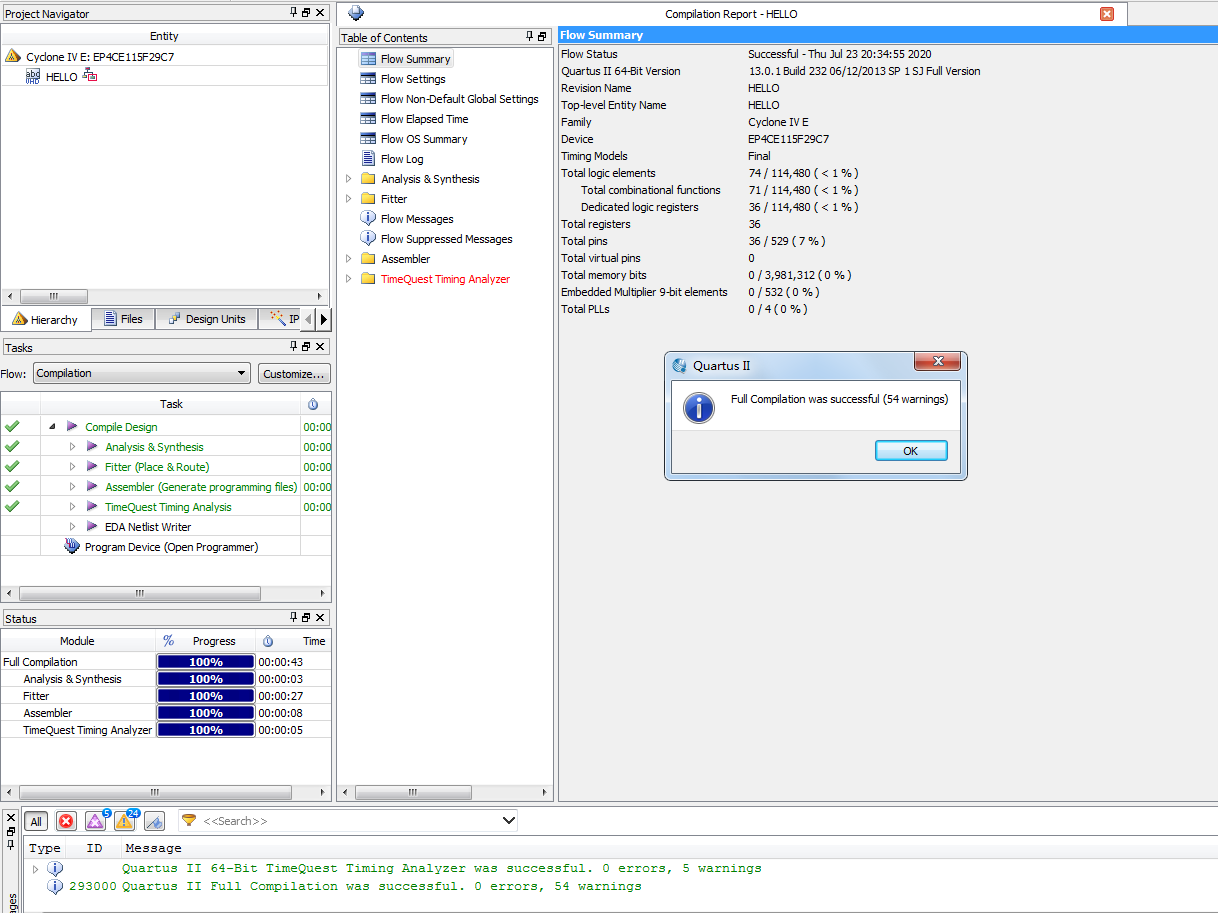

5. 程序编译

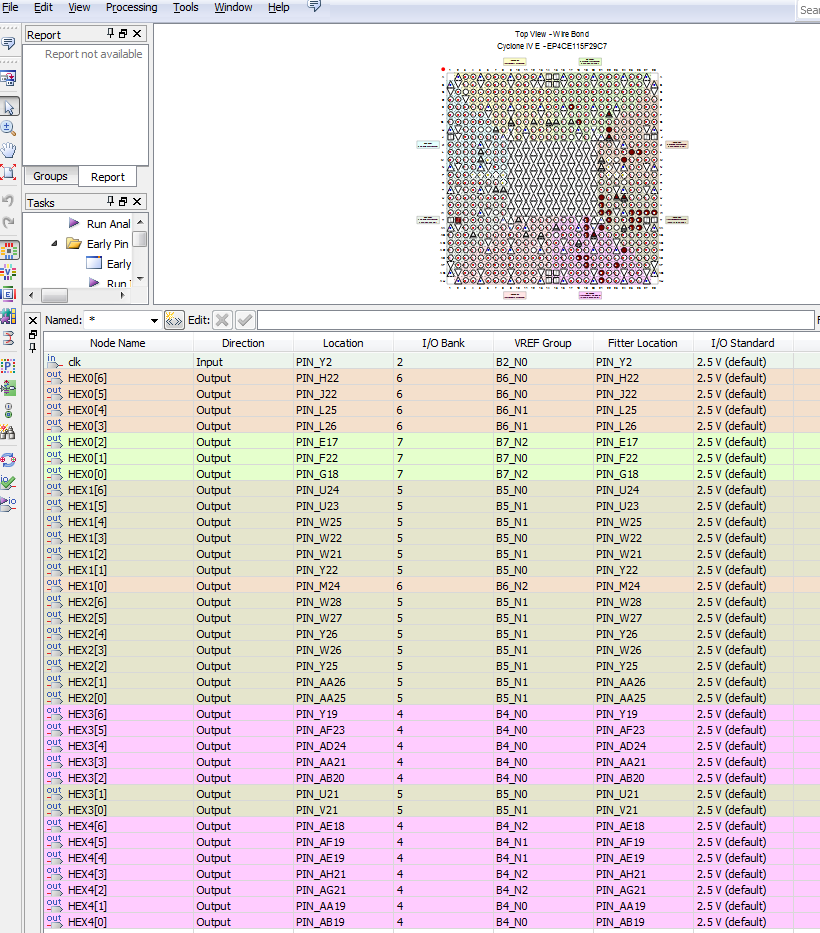

6. 管脚分配

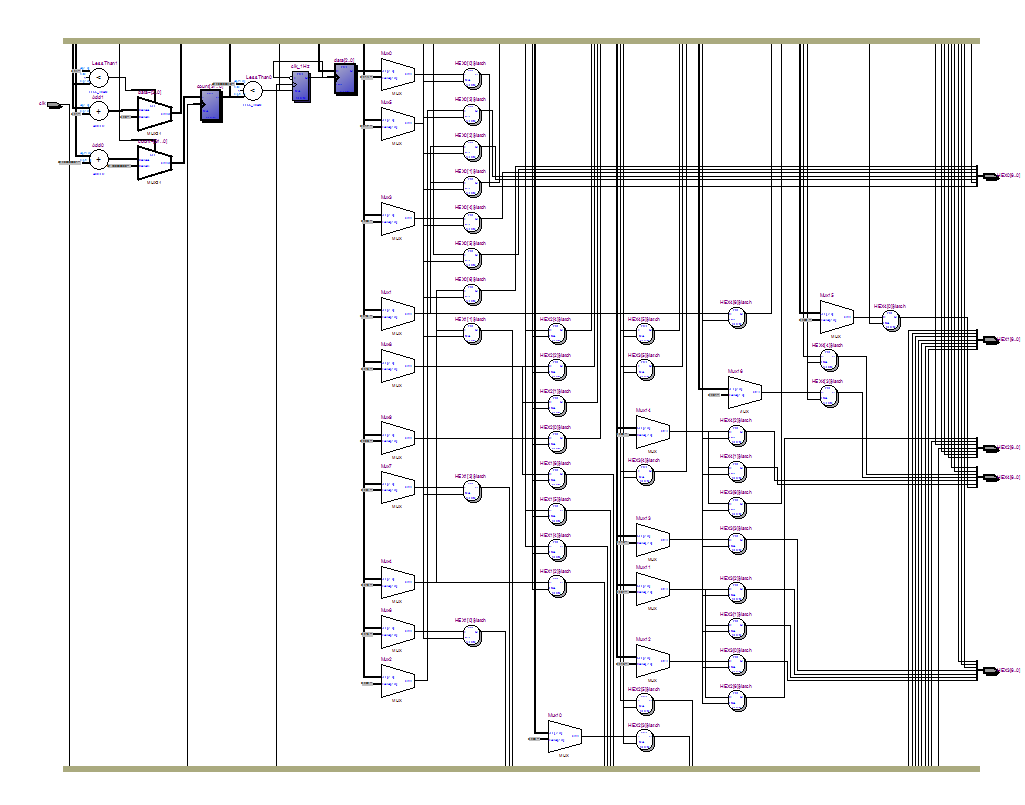

7. RTL图

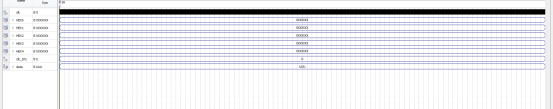

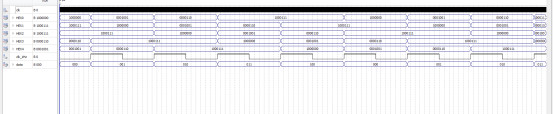

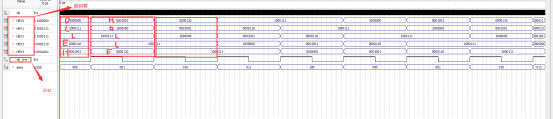

8. VWF文件

9. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY HELLO IS PORT ( clk : IN STD_LOGIC;--时钟50MHz HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段数码管 HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段数码管 HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段数码管 HEX3 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段数码管 HEX4 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)--7段数码管 ); END HELLO; ARCHITECTURE behave OF HELLO IS SIGNAL count : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000";--计数器 SIGNAL clk_1Hz : STD_LOGIC := '0'; SIGNAL data : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN --IF (count >= "00000001011111010111100001000000") THEN--50M分频到1Hz,计数25000000翻转一次 IF (count >= "00000000000000000000000001000000") THEN--仿真时减小计数器为00000000000000000000000001000000,实际上板时用上一句 count <= "00000000000000000000000000000000"; clk_1Hz <= NOT(clk_1Hz);--翻转 ELSE count <= count + "00000000000000000000000000000001";--计数 clk_1Hz <= clk_1Hz;--1Hz信号 END IF; END IF; END PROCESS; --5进制计数 PROCESS (clk_1Hz) BEGIN IF (clk_1Hz'EVENT AND clk_1Hz = '1') THEN IF (data >= "100") THEN--计数到4 data <= "000";--计数回0 ELSE data <= data + "001";--计数 END IF; END IF; END PROCESS; --5选1,字母1秒移位一次 PROCESS (data) BEGIN CASE data IS--7段数码管,低电平亮 WHEN "000" => HEX4 <= "0001001";--显示H HEX3 <= "0000110";--显示E HEX2 <= "1000111";--显示L HEX1 <= "1000111";--显示L HEX0 <= "1000000";--显示O WHEN "001" => HEX0 <= "0001001";--显示H HEX4 <= "0000110";--显示E HEX3 <= "1000111";--显示L HEX2 <= "1000111";--显示L HEX1 <= "1000000";--显示O WHEN "010" =>

源代码

扫描文章末尾的公众号二维码

本文详细描述了如何使用VHDL在Quartus环境下,通过DE2-115实验平台实现5个7段数码管循环显示英文单词HELLO的过程,包括计数器设计、多路选择器的选择以及管脚分配等步骤。

本文详细描述了如何使用VHDL在Quartus环境下,通过DE2-115实验平台实现5个7段数码管循环显示英文单词HELLO的过程,包括计数器设计、多路选择器的选择以及管脚分配等步骤。

4301

4301

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?