目录

一、概念

数字电路按照逻辑功能一般可以分为组合逻辑和时序逻辑。组合逻辑电路是指不含有任何存储器件(一般指寄存器)的电路,它的输出只和当前电路的输入有关;时序逻辑电路含有存储器件,可以含有组合逻辑,它的输出不仅和当前输入值有关,也和电路上一时刻状态有关。

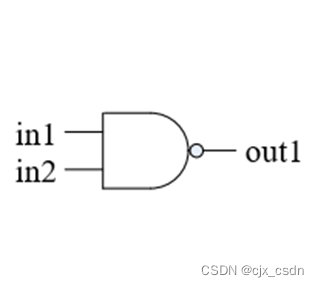

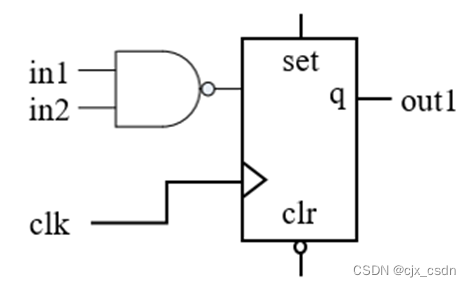

如图1和图2所示,图1为组合逻辑,图2为时序逻辑。

图1中,输入信号in1和in2发生变化时,输出信号out1也会立刻发生变化(忽略电路延迟),而在图2时序逻辑电路中,只有在输入时钟信号clk上升沿(或下降沿)到来后,输出信号out1才会发生变化。当然,对于时序逻辑电路在时钟沿到来时,输入信号必须保持稳定(满足建立时间和保持时间要求),否则会导致亚稳态现象。

二、区别

总的来讲,组合逻辑和时序逻辑有以下区别:

- 组合逻辑的输出与输入直接相关,时序逻辑的输出和原有状态也有关;

- 组合逻辑立即反应当前输入状态,时序逻辑还必须在时钟上升沿触发后输出新值;

- 组合逻辑容易出现竞争、冒险现象,时序逻辑一般不会出现竞争、冒险现象;

- 组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛,时序逻辑更可控;

- 组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路。

在如今的数字系统应用中,几乎不可能只采用组合逻辑来实现一个复杂功能的应用,时序逻辑在时钟驱动下,能够按部就班的完成各种复杂的任务,也能够非常便利的达到时序要求,并且能够解决各种异步处理带来的亚稳态问题。

"FPGA Zone" 专注 FPGA 知识学习与工程应用,欢迎 FPGA 爱好者关注公众号,领取 200G+ FPGA 相关学习资料!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?