目录

一、建立时间和保持时间

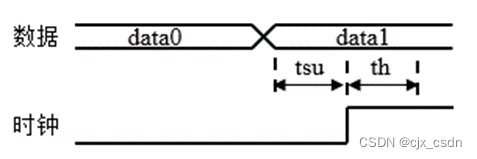

如图1所示,建立时间(set up time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器,建立时间决定了该触发器之间的组合逻辑的最大延迟。

保持时间(hold time)是指在触发器时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器,保持时间决定了该触发器之间的组合逻辑的最小延迟。

二、亚稳态

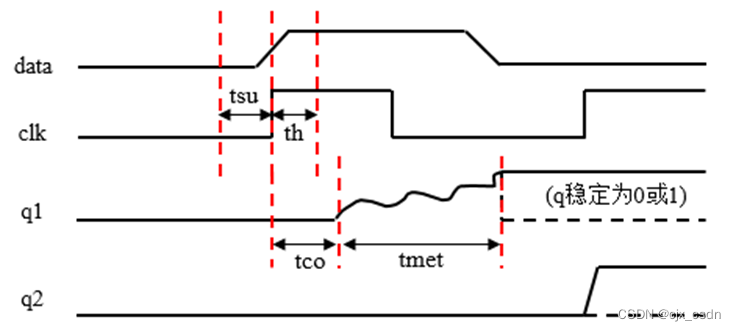

亚稳态是指寄存器无法在短时间段内到达一个稳定状态,例如图2所示,当寄存器不满足建立时间和保持时间,导致寄存器输出有一段时间不稳定状态(输出为0和1的中间电平),就是亚稳态。

亚稳态一般产生于数据跨时钟域传输、异步复位电路,以及其它异步逻辑电路中,产生亚稳态后,寄存器输出在稳定(0或1)下来之前可能是毛刺、振荡、固定的某一电压值,这将导致后续电路也会出现亚稳态,进而导致电路所实现的功能与设计不符。

三、避免亚稳态策略

1. 用反应更快的触发器;

2. 引入同步逻辑;

3. 改善时钟质量,用边沿变化快的时钟。

四、多级寄存器阻断亚稳态传播

在FPGA设计中,如果不可避免要使用异步逻辑,通常采用两级寄存器完成对单bit异步信号采样,如图3所示。

采用两级寄存器对异步信号采集,当tco + tmet+ tsu(第二级寄存器)<= T(一个时钟周期)时,第二级寄存器就可以稳定的采样。这就相当于多给寄存器一个时钟周期时间来恢复稳定状态,从而大大减少亚稳态传播几率。这里需要注意的地方是,增加第二级寄存器并非避免亚稳态的“发生”,而是防止亚稳态的“传播”。

还必须注意的是,虽然这种方法可以以防止亚稳态的传播,但是并不能保证两级触发器之后的数据是正确的。通常这种电路都有一定数量的错误电平数据,所以仅适用于少量对于错误不敏感的地方。对于敏感的电路,或者多bit信号跨时钟域传输,可以采用双口 RAM 或 FIFO。

"FPGA Zone" 专注 FPGA 知识学习与工程应用,欢迎 FPGA 爱好者关注公众号,领取 200G+ FPGA 相关学习资料!

6103

6103

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?