Verilog坑很多

今天看到一个以前一直没有想清楚的地方,所以在这里记录一下。

阻塞赋值:

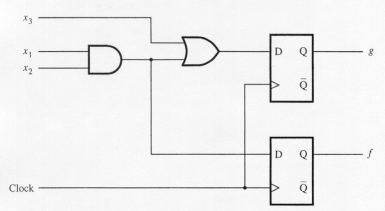

<span style="white-space:pre"> </span>reg f, g;<span style="font-size: 14.5pt;"><span style="white-space: pre;"> </span>always @(posedge Clock)</span><span style="white-space:pre"> </span>begin<span style="white-space:pre"> </span>f = x1 & x2;<span style="white-space:pre"> </span>g = f | x3;<span style="white-space:pre"> </span>end 综合产生的是:

阻塞赋值产生的 D flip-flop是并列的。

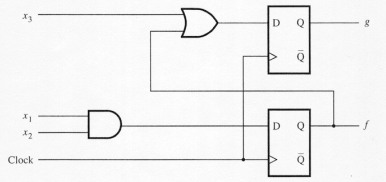

而非阻塞赋值产生的反而是级联的:

<span style="white-space:pre"> </span>always @(posedge Clock)

<span style="white-space:pre"> </span>begin

<span style="white-space:pre"> </span>f <= x1 & x2;

<span style="white-space:pre"> </span>g <= f | x3;

<span style="white-space:pre"> </span>end

1637

1637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?