Allegro如何生成光绘文件

导出gerber文件步骤

Cadence如何输出BOM、原理图打印

allegro更改字体和大小(丝印,位号等)

利用Excel快速创建多引脚元器件

如何让引脚倒序排列

如何隐藏管脚名称

如何更新原理图中的元件符号

如何给原理图元件添加封装

如何修改焊盘并在pcb中更新

如何查看元件的所有页面,以及切换页面

如何引用其他工程里的元件或者信息栏

快捷键的设置

修改部分原理图位号

更改原理图页面大小

表格复制帮助ORCAD快速建库\将别人的元件保存到自己的库中

Allegro消除元件本身的引脚间距过小造成的DRC错误

如何生成钻孔表

allegro如何查看具体的DRC错误原因

分裂元件的正确使用、位号如何为一组

如何改变原点位置到安装孔中心

Cadence Allegro DXF导入与生成板框的方法

Allegro导入dxf使用Z-Copy提示”Not a closed polygon or CLine. Element ignored!”解决办法

layout时修改过孔参数

设置差分对

out of date shapes原因及解决方法

修改单块铜皮与通孔的连接方式为全连接

在quick place器件时显示cannot find symbol

利用Excel快速创建多引脚元器件

(1)选中所有管脚,右键edit properties

(2)点击表格左上角,按快捷键Ctrl+Insert将表格完整复制到Excel表格中

(3)修改D列引脚名和引脚类型

(4)点击Excel表格左上角,按快捷键Shift+Insert将Excel表格完整复制到表格中即可

右键edit properties也可以直接在表中批量修改管脚信息

如何让引脚倒序排列

(1)拉长虚线框

(2)把右列的管脚移到左列

(3)选中那些管脚,右键cut,再右键paste粘贴到右列

(4)调整虚线框到合适大小即可

如何隐藏管脚名称

options-part properties-pin names visible-FALSE-OK

如何更新原理图中的元件符号

方法1:通过add part的方式,记得先把原理图中原先的元件符号删掉,再放置新的元件符号,否则会报错。

方法2:右键library cache中的元件符号名称,点击update cache,yes即可。

如何给原理图元件添加封装

(1)library里双击封装打开页面,options-package properties-输入封装名-OK-save保存

(2)design cache里右键update cache更新封装,再replace cache,选择replace schematic part properties,勾选preserve refdes,保存。

(3)打开原理图页面,双击元件查看封装是否添加。

如何修改焊盘并在pcb中更新

在pad designer软件中修改焊盘并保存,在pcb的封装界面中点击tools-padstack-refresh,在窗口点击refresh即可。

如何查看元件的所有页面,以及切换页面

菜单栏view-package查看所有页面。

快捷键Ctrl+N切换下一个页面,Ctrl+B返回上一个页面。

如何引用其他工程里的元件或者信息栏

先design cache右键copy,然后olb右键paste。

快捷键的设置

(1)打开env文件:找到cadence软件安装路径D:\Cadence\SPB_Data\pcbenv\env文件,用写字板打开。

(2)一连串的alias区域就是快捷键设置的地方,在下边设置快捷键。例如funckey d add connect

(3)保存文件,重启cadence软件即可。

快捷键设置:26个大小写英文字母+0~9数字组合, ~代表Ctrl键。

不能设置x,y,i,因为xy是坐标,i是偏移。

修改部分原理图位号

但是很多情况下我们并不需要从头对所有元器件编号,大多数情况下我们只需要对一部分元器件进行位号修改即可。

比如我们把上图中的R1手动修改成R5(直接用用鼠标点击位号进行手动修改),这时候位号下面就会多一条横线,代表这个位号被操作者修改过了。

这时如果我们想把剩余的电阻和运放的位号重新排序一下,就可以这么做:

选中原理图,点击Tool>Annotate,在弹出的窗口中重点关注勾选圈中的地方,

这里勾选的地方意思是保持操作者更改的地方不变,也就是我们带下划线的R5不会变,其他元器件的位号会变。

更改原理图页面大小

第一步:右键页面,选择schematic page properties

第二步:设置单位和页面大小,点击确定即可。

表格复制帮助ORCAD快速建库、将别人的元件保存到自己的库中

表格复制帮助ORCAD快速建库、将别人的元件保存到自己的库中

Allegro消除元件本身的引脚间距过小造成的DRC错误

1、Edit->property或shift+F2选中元件

2、添加Nodrc_Sym_Same_Pin属性

3、选择true后点击apply添加,OK,DRC错误消失

如何生成钻孔表

Manufacture->NC.->Drill Legend ,生成如下钻孔信息

PS:如果放不下去,提示Design extents not sufficient, select origin again. 就在

setup->Design Paraments Editor->Deisign 选项卡里将Extents里的width和height加大

[allegro如何查看具体的DRC错误原因]

在约束规则管理器里面点击DRC即可查看

分裂元件的正确使用、位号如何为一组

1、options-part properties

2、命名、编号

3、原理图中dsn右键annotate,勾选action第三项,再将physical packaging中最后一个花括号的内容改为上图中的name

4、原理图中dsn右键annotate,勾选action第一项即可。

如何改变原点位置到安装孔中心

1、setup-change drawing origin

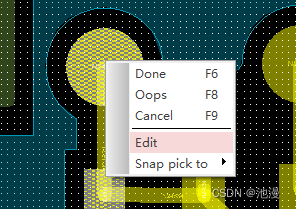

2、在安装孔中心范围内右键,snap pick to-symbol center即可。

Cadence Allegro DXF导入与生成板框的方法

Allegro导入dxf使用Z-Copy提示”Not a closed polygon or CLine. Element ignored!”解决办法

Allegro导入dxf使用Z-Copy提示”Not a closed polygon or CLine. Element ignored!”解决办法

layout时修改过孔参数

- tools菜单

- 右键想要修改的过孔

- 修改后更新并退出

设置差分对

out of date shapes原因及解决方法

修改单块铜皮与通孔的连接方式为全连接

- 选择“Shape”

- 点击需要修改的铜皮

- 右键选择“Parameters”

- 选择Thermal relief connects,在Thru pins选择Full centact;

- 点击Apply;即可设置当前铜皮为全连接方式,而不影响其他铜皮的连接属性。

在quick place器件时显示cannot find symbol

一个器件都没有摆放,并且导入网表时没有出错,那么请检查psm的路径和pad路径中的第一项$ p s m p a t h 和 psmpath和psmpath和 $padpath是否删除。没有删除也会导致cannot find symbol。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?