一、简介:

74LS192D 是一款常用的 同步十进制可逆计数器(Synchronous Up/Down Decade Counter),属于 74LS系列 的 TTL 逻辑集成电路。

二、基本功能

-

计数器类型:同步、可逆(双向)计数器,支持 加法计数(UP) 和 减法计数(DOWN)。

-

计数范围:十进制(0~9),通过外部连接也可实现二进制计数。

-

同步工作:所有触发器在时钟脉冲边沿同步触发,避免异步计数器的毛刺问题。

三、关键引脚

-

CLK_UP(引脚 5):加法计数时钟输入(上升沿触发)。

-

CLK_DOWN(引脚 4):减法计数时钟输入(上升沿触发)。

-

QA~QD(引脚 3,2,6,7):4 位二进制输出(BCD 码)。

-

MR(引脚 14):异步复位(高电平有效,直接清零)。

-

PL(引脚 11):并行加载控制(低电平有效,预置数)。

-

DATA A~D(引脚 15,1,10,9):并行数据输入(用于预置初始值)。

-

TCU(引脚 12):加法计数进位输出(计数到 9 后输出脉冲)。

-

TCD(引脚 13):减法计数借位输出(计数到 0 后输出脉冲)。

四、工作模式

-

加法计数:时钟信号从

CLK_UP输入,计数从 0→9,满 9 后TCU输出进位脉冲。 -

减法计数:时钟信号从

CLK_DOWN输入,计数从 9→0,到 0 后TCD输出借位脉冲。 -

预置数:当

PL=0时,将DATA A~D的值直接加载到计数器。 -

复位:

MR=1时,计数器立即清零(异步操作)。

五、典型应用

-

数字时钟、计时器、频率分频器。

-

工业控制中的计数与序列生成。

-

与其他 74 系列芯片(如 74LS47 BCD-译码器)配合驱动数码管显示。

六、电源与封装

-

电源电压:+5V(典型 TTL 电平)。

-

封装:DIP-16(双列直插)或 SOIC 封装(74LS192D 中的 "D" 通常表示 SOIC 封装)。

七、注意事项

-

时钟输入需满足 TTL 电平(高电平 ≥2V,低电平 ≤0.8V)。

-

避免未使用的输入引脚悬空,建议上拉或下拉处理。

-

与 CMOS 器件连接时需注意电平匹配。

八、74LS192D 真值表

| MR (复位) | PL (预置) | CLK_UP (加法) | CLK_DOWN (减法) | 工作模式 | 输出 QA~QD |

|---|---|---|---|---|---|

| 1 (H) | X (任意) | X | X | 异步复位 | 0000 (立即清零) |

| 0 (L) | 0 (L) | X | X | 并行加载 | 等于 DATA A~D 输入 |

| 0 (L) | 1 (H) | ↑ (上升沿) | 1 (H) | 加法计数 | 0→9 循环 |

| 0 (L) | 1 (H) | 1 (H) | ↑ (上升沿) | 减法计数 | 9→0 循环 |

| 0 (L) | 1 (H) | 1 (H) | 1 (H) | 保持 | 保持当前值 |

九、关键说明:

-

MR(复位)优先级最高:

-

当

MR=1时,立即清零输出(QA~QD=0000),其他信号无效。

-

-

PL(预置):

-

当

PL=0且MR=0时,并行加载输入数据(DATA A~D)到输出端。

-

-

计数模式:

-

加法计数:

CLK_UP上升沿触发,CLK_DOWN保持高电平。 -

减法计数:

CLK_DOWN上升沿触发,CLK_UP保持高电平。 -

计数到 9(加法)或 0(减法)时,分别通过

TCU或TCD输出进位/借位脉冲。

-

-

无效状态:

-

若

CLK_UP和CLK_DOWN同时为上升沿,结果不确定(应避免)。

-

十、输出与进位信号:

-

TCU(加法进位):

-

当加法计数从

1001(9)→0000(0)时,TCU输出一个低电平脉冲。

-

-

TCD(减法借位):

-

当减法计数从

0000(0)→1001(9)时,TCD输出一个低电平脉冲。

-

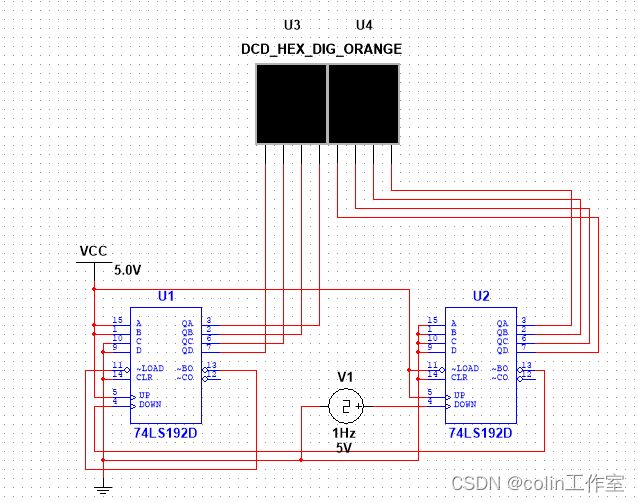

十一、仿真原理图:

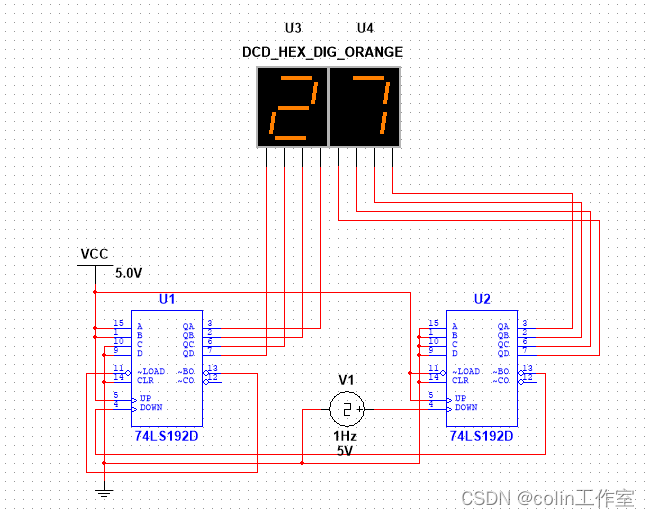

十二、仿真效果:

5434

5434

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?