计算机总线

总线 (BUS)

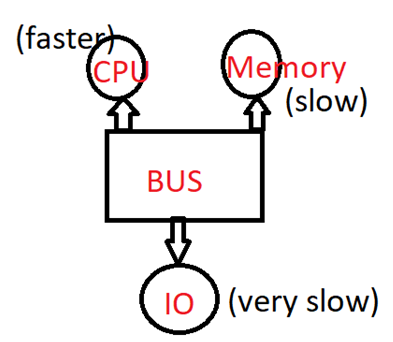

A bus is a communication channel which is used between the different nodes for providing the communication. The bus which is used to provide the communication between the CPU, Memory and IO components it is called as a system bus.

总线是在不同节点之间用于提供通信的通信通道。 用于在CPU,内存和IO组件之间提供通信的总线称为系统总线。

A set of connected lines is also called a bus. Basically, a bus is a bundle of wires that are grouped together to serve a single purpose in the microprocessor, in which there are three set of communication lines that are called buses. The system bus is categorized on the basis of lines in three different formats for providing the effective communication.

一组连接的线路也称为总线。 基本上,总线是一束电线,这些电线被组合在一起以在微处理器中用于单一目的,在其中有三套称为总线的通信线。 系统总线基于线路以三种不同的格式进行分类,以提供有效的通信。

1. Address lines

1.地址行

These lines are used to carry the address towards memory and IO components. Address lines are unidirectional. Based on the number of the address lines we can able to determine the capacity of the memory system.

这些行用于将地址传送到内存和IO组件。 地址线是单向的。 根据地址线的数量,我们可以确定存储系统的容量。

Example: In 8085 microprocessors there are 16 address lines are present which means it contains 64 K memory locations.

示例:在8085微处理器中,存在16条地址线,这意味着它包含64 K个存储单元。

2. Data lines

2.数据线

These lines are used to carry the binary sequence between the CPU, Memory and IO. So data lines are bidirectional. Based on the number of data lines we can determine word length of the processor and basis on the word length we can determine the performance of the processor.

这些行用于在CPU,内存和IO之间传送二进制序列。 因此,数据线是双向的。 根据数据线的数量,我们可以确定处理器的字长,并根据字长可以确定处理器的性能。

3. Control lines

3.控制线

These lines are used to carry the control signal and timing signal. In which control signal indicates the type of operation and timing signal are used to synchronize the memory and IO operation with processor clock.

这些线用于承载控制信号和定时信号。 其中,控制信号指示操作的类型,时序信号用于使存储器和IO操作与处理器时钟同步。

巴士仲裁 (Bus Arbitration)

A bus has several units like (memory, IO and processor) which are connected to it. At any point of time any of these units may want to start a transaction. Arbitration is a process of deciding which unit will get access to the bus for driving the transaction. There are basically three bus arbitration mechanisms which are as follows here:

总线具有多个与之相连的单元(内存,IO和处理器)。 在任何时候,这些单位中的任何一个都可能要开始交易。 仲裁是决定哪个单位可以访问总线以驱动交易的过程。 总线仲裁机制基本上有以下三种:

1. Daisy chaining

1.菊花链

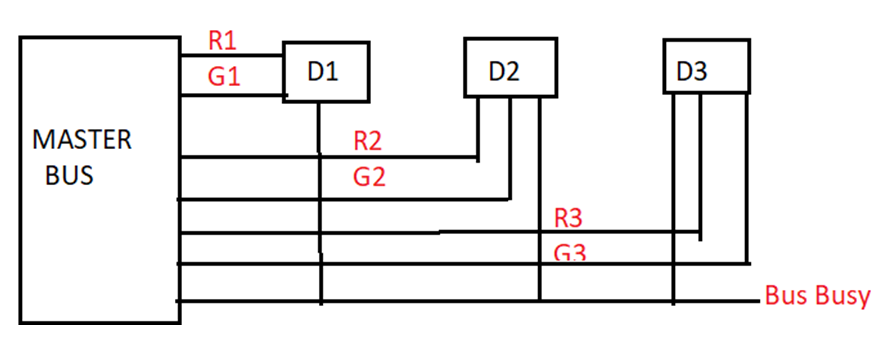

In this mechanism there are three bus lines which are Bus busy, Bus request and Bus grant which are arranged in daisy chaining fashion. This is simple to achieve and only contains three extra bus lines. This method has the poor fault tolerance and has the hardwired priority.

在这种机制中,有3条以菊花链方式排列的总线,它们分别是Bus Bus,Bus Request和Bus Grant。 这很容易实现,仅包含三个额外的总线。 此方法的容错性较差,并且具有硬连线优先级。

Steps to achieve daisy chaining mechanism:

实现菊花链机制的步骤:

Each devices checks, if bus is not busy then make bus request to the master.

每个设备检查总线是否不忙,然后向主设备发出总线请求。

Then master see the bus request like high, and then it activates the bus grant.

然后主人看到总线请求很高,然后激活总线授权。

Then bus grant line travel from one device to another, in this time if a device gets a bus grant, mark the bus busy.

然后,总线授权线路从一个设备移动到另一台设备,这时如果设备获得了总线授权,则将总线标记为繁忙。

2. Polling

2.轮询

This is slightly a better mechanism. There is no such disadvantage of daisy chaining. It has the possibility of dynamic priority. In this mechanism we have the log n number of polling lines for n devices. Disadvantage of this mechanism is that, they contain extra poll lines and they have a polling delay.

这是一个更好的机制。 菊花链没有这种缺点。 它具有动态优先级的可能性。 在这种机制下,我们有n个设备的n个轮询行数。 这种机制的缺点是,它们包含额外的轮询行,并且具有轮询延迟。

Steps to achieve polling mechanism

实现轮询机制的步骤

If bus is not busy, make bus request.

如果总线不忙,请提出总线请求。

Master polls by placing device on polling lines. In this master decides priority.

通过将设备放在轮询线上来进行主轮询。 主人决定优先权。

If device gets access to the bus, mark bus busy.

如果设备可以访问总线,请将总线标记为忙。

3. Independent request

3.独立要求

This is the fastest mechanism in which also dynamic priority is possible. This is a mechanism in which we have request and grant lines for each of the devices with master. This mechanism has 2n lines for the n devices.

这是最快的机制,其中动态优先级也是可能的。 这是一种机制,在这种机制中,我们为每个具有主控设备的设备提供了请求和授权行。 该机制为n个设备提供2n条线。

Steps to achieve independent request mechanism

实现独立请求机制的步骤

If bus is not busy, make bus request.

如果总线不忙,请提出总线请求。

Master decides who to grant access, and indicates through grant lines.

主人决定授予访问权限的人,并通过授予行进行指示。

If device gets bus grant, make bus busy.

如果设备获得总线许可,请使总线繁忙。

翻译自: https://www.includehelp.com/cso/bus-computer-science-organization.aspx

计算机总线

2363

2363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?