引脚描述

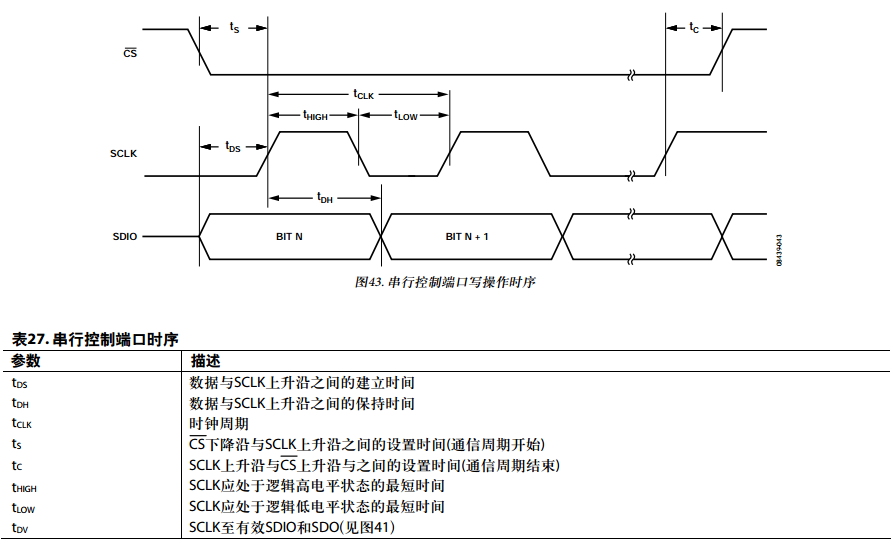

SCLK(串行时钟)是串行移位时钟,此引脚为输入。 SCLK用来使串行控制端口的读写操作同步。写入数据位记录在该时钟的上升沿,读出数据位记录在下降沿。此引脚由一个40 kΩ电阻内部下拉至地。SDIO(串行数据输入/输出)是一个两用引脚,既可以仅用作输入(单向模式),也可以同时用作输入和输出(双向模

式)。 AD9523默认采用双向I/O模式。

SDO(串行数据输出)仅用于单向I/O模式,作为回读数据的独立输出引脚。 SDO始终有效,因此多从机环境不应使用单向I/O模式。

CS(片选引脚信号)是低电平有效控制,用来选通读写周期。当CS为高电平时, SDIO处于高阻态。此引脚由一个40kΩ电阻内部上拉至VDD3_REF。

SPI工作模式

SPI模式支持单字节和多字节传输,以及MSB优先和LSB优先传输格式。 AD9523串行控制端口可以针对一个双向I/O引脚(仅 SDIO)或两个单向 I/O引脚 (SDIO/SDO)配置。

当传输三个或更少字节的数据(加上指令数据)时(见表24),支持CS空闲高电平模式。在此模式中, CS引脚可以在任何字节边界上暂时返回高电平,使系统控制器有时间处理下一个字节。 CS仅可以在字节边界上进入高电平;但它可以在传输的任一阶段(指令或数据)进入高电平。

在此期间,串行控制端口状态机进入等待状态,直到所有数据发送完毕。如果数据尚未发送完毕,而系统控制器决定中止传输,必须完成剩余传输,或者使CS返回低电平并至少保持一个完整的SCLK周期(但少于8个SCLK周期),使状态机复位。在非字节边界上拉高CS引脚将终止串行传输并刷新缓冲器。

在流模式中(见表24),可以连续流形式传输任意数量的数据字节,寄存器地址自动递增或递减(见SPI MSB/LSB优先传输部分)。在传输最后一个字节结束时,必须拉高CS,从而结束流模式。

通信周期—指令加数据

AD9523的通信周期可分为两个部分。第一部分是在前16个SCLK上升沿将一个16位指令字写入AD9523。该指令字向AD9523串行控制端口提供有关数据传输(即通信周期的第二部分)的信息,明确即将发生的数据传输是读操作还是写操作,数据传输的字节数,以及数据传输中第一个字节的起始寄存器地址。

写操作

如果指令字定义了一个写操作,则第二部分便是将数据传输至AD9523的串行控制端口缓冲器。数据位记录在SCLK的上升沿。

传输长度(1/2/3字节或流模式)由指令字节中的两位(W1和W0)表示。当传输1、 2或3字节(但不是流模式)时,在每个8位序列之后可以拉高CS,使总线空闲,但最后一个字节之后除外,此时会结束通信周期。当总线空闲时,如果CS变为低电平,就会恢复串行传输。在非字节边界上拉高CS引脚将复位串行控制端口。在写操作期间,流模式不会跳过保留或空白字节,用户可以向保留寄存器地址写入0x00。由于数据是写入串行控制端口缓冲区,而不是直接写入AD9523的实际控制寄存器,因此需要额外的操作来将串行控制端口缓冲内容传输到AD9523的实际控制寄存器,从而使其有效。更新寄存器操作包括将自清零位IO_Update(寄存器0x234的位0,见表56)置1。执行更新寄存器操作之前,可以改变任意数量的数据字节。更新寄存器会同时激活上次更新以来所有已写入缓冲器的寄存器变化。

读操作

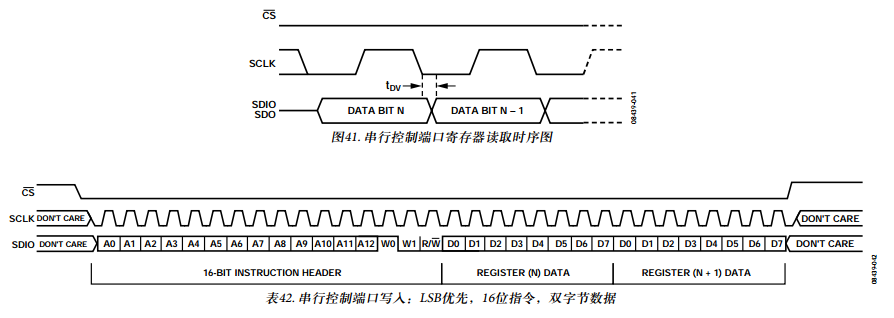

AD9523仅支持长指令模式。如果指令字定义了一个读操作,在接下来的N × 8个SCLK周期,数据从指令字所规定的地址逐个输出,其中N为1至3,由位[W1:W0]确定。如果N = 4,读操作将为流模式,持续至CS变为高电平。流模式不会跳过保留或空白寄存器。回读数据在SCLK的下降沿有效。

AD9523串行控制端口的默认模式是双向模式。在双向模式中,发送数据和回读数据均出现在SDIO引脚上。也可以将AD9523设置为单向模式。在单向模式中,回读数据出现在

SDO引脚上。回读请求读取串行控制端口缓冲区或有效寄存器中的数据(见图37)。

SPI指令字(16位)

指令字的MSB为R/W,表示该指令是读操作还是写操作。接下来的两位([W1:W0])表示传输长度,单位为字节。最后13位([A12:A0])是读或写操作的起始地址。对于写操作,指令字之后是位[W1:W0]所代表的数据字节数(见表24)。

位[A12:A0]选择通信周期数据传输阶段写入或读取的寄存器地址(寄存器映射范围内)。只需使用位[A11:A0]就能涵盖AD9523所用的全部0x234寄存器。位A12必须始终为0。对于多字节传输,此地址是起始字节地址。在MSB优先模式中,后续字节会递减该地址。

SPI MSB/LSB优先传输

AD9523指令字和字节数据可以是MSB优先或LSB优先。写入寄存器0x000的任何数据都必须进行镜像:位7镜像到位0,位6镜像到位1,位5镜像到位2,位4镜像到位3。这使得LSB优先或MSB优先事实上是一样的。 AD9523的默认设置为MSB优先。

当寄存器0x000的位1和寄存器0x000的位6设置LSB优先时,它会立即生效,因为这只影响串行控制端口的操作,而不需要执行更新。

当MSB优先模式有效时,指令和数据字节必须按照从MSB到LSB的顺序写入。采用MSB优先格式的多字节数据传输由一个包括高数据字节寄存器地址的指令字节开始。后续数据字节必须按照从高地址到低地址的顺序传输。在MSB优先模式下,多字节传输周期每传输一个数据字节,串行控制端口的内部地址产生器便递减1。

当LSB优先模式有效时,指令和数据字节必须按照从LSB到MSB的顺序写入。采用LSB优先格式的多字节数据传输由一个包括低数据字节寄存器地址的指令字节开始,其后是多个数据字节。在多字节传输周期中,每传输一个字节,串行端口的内部字节地址产生器便递增1。如果MSB优先模式有效(默认), AD9523串行控制端口的寄存器地址将从刚才向控制寄存器0x000写入多字节I/O操作的寄存器地址开始递减。如果LSB优先模式有效,串行控制端口的寄存器地址将从刚才向控制寄存器0x234写入多字节I/O操作的寄存器地址开始递增。这些操作不会跳过不用的地址。

在MSB优先模式中,对于跨过地址0x234或0x000的多字节访问, SPI内部禁用对后续寄存器的写操作,对后续寄存器读操作则返回0。

在流模式下,如果跨过地址边界,则传输终止(见表25)。

1688

1688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?