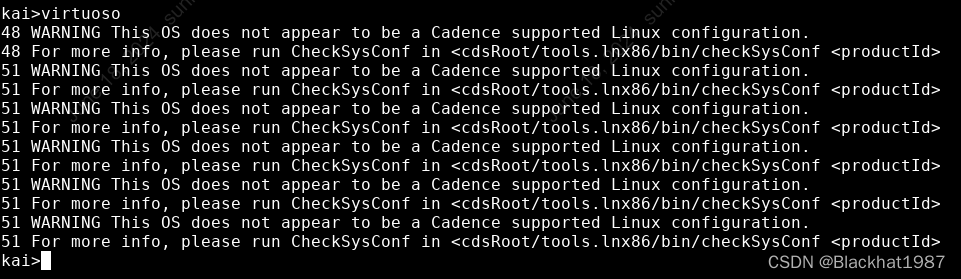

错误描述:

WARNING This OS does not appear to be a cadence supported Linux configuration.

For more info, please run checkSysConf in <cdsRoot/tools.lnx86/bin/checkSysconf

操作系统:centos 7.9

升级IC617之前没有类似错误,前几天打了两个补丁包(hotfix 702和721 )后出现以上错误,查到一些解决办法似乎都不太能简单快捷的解决,然实际/cadence/IC617/share/oa/bin/sysname 文件中的内核版本中看着已经包含RHEL7的OS兼容性。

有看到一些大神去修改sysname的OS兼容列表和处理libfontconfig版本等思路。

但是我都不用选。。。

问了一个道友,方案很简单。。。。你不就是check嘛 ,只是个warning 又不是不能用,那么吧check关掉就好了。

所以修改环境变量:

csh :setenv W3264_NO_HOST_CHECK 1

bash:export W3264_NO_HOST_CHECK=1

649

649

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?