终于来到了第三章,过了一个春节,第二章讲了什么感觉已经记不得了(不愧是我),但是感觉第二章的内容需要的时候再去看也可以,有一个大致的架构就行,先这么安慰自己吧,看看后面打不打脸。

人啊,不能颓,一颓一直爽,一直颓一直爽。

终于来到了第三章的3.1,存储器与CPU的关系 2021.2.22

复习:

存储器=存储体+MAR+MDR

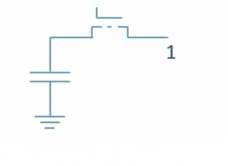

由下图控制

存储元

由下图实现,下图为存储元,

写的时候,先把信号1放在数据寄存器,时序控制逻辑控制开关元件(就是上图虚线的部分)打开,电路连通,就可以写上了。

存储体

一个存储体由多个存储元来构成

如图:

,每一行的存储元是存储单元,矩阵组成了存储体。存储字长是8个,就是8bit=1Byte

存储器芯片

当读的时候,红色的线的信号是1,电路连通,电容的信息就顺着流到绿色的线流出去。

红色的线控制读,所以只能有一根是1,其他都是0,否则会冲突。如果是8根线,只有一个信号,太浪费,所以采用译码器来表示哪根是读。

同时也要提供一个控制电路来表示读还是写。

片选线:开关,两种模式:高电平有效,低电平有效

把他们组装起来就是一个存储器芯片

地址线对应MAR(行数),数据线对应MDR(列数)

总容量=存储单元个数*存储字长=*8bit=8B

8*8位的存储芯片

寻址

按照字节寻址和字寻址有什么不一样呢:

按照字节寻址,如图的话字长是4B,把每个存储单元分成4份,每4份是一个组,如绿色的格子。就需要10根地址线,有1K种地址,每四个为一组,有共同点。

按照字寻址的话,每个存储单元是一份。

多字节连续存放:大端方式与小端方式

半导体存储芯片

片选线:有多个存储芯片,片选线恶意确定哪个芯片被选中。可用于容量的扩充

注意箭头的方向,地址线是单向的,数据线是双向的

随机存取存储器

从给出地址信号到取出这个单元的时间是一样的,即电流流动的时间,访问这个单元的时间跟其所在的物理位置没有关系。RAM

RAM分为静态随机存储器和动态随机存储器

电容很不稳定,充上电之后会缓慢的流失。

其两个都需要有电,如果停电了,信息会丢失。

电容是破坏性读数,因为是检测电流,如果有电流则是1,但是电荷会运动走,电容就没电了,就是0了,所以就需要刷新。

关于DRAM的几个问题

采用行列地址,可以有效的减少选通线。比如一开始需要256根选线,排列成矩阵之后仅仅需要32根。

DRAM的刷新

思路一:2ms内刷新一次就够了,分散刷新刷新了多次,思路一的时间变长了;

思路二:我们可以用思路二进行集体刷新,一共128行,就需要128*0.5=64微秒的时间刷新,这一阶段存储器是不对外开放的,就是死区,就是自己默默的刷新。

思路三:128次的刷新请求均匀的分散刷新,2ms/128=15.6微秒,每15.6就有0.5是死区。

这个刷新过程是不需要CPu来控制的,以行为单位,存储器中的芯片同时刷新

SARAM的读周期

CS是片选线,上面有一杠,代表低电平有效

第一根红线-第二根红线:地址稳定的过程,因为是电流,所以速度不一样,所以隔一段时间才打开芯片的开关

第二根红线-第三根红线:打开开关,数据从存储矩阵中被调出来

第三根红线-第四根红线:调出来也需要时间稳定

第四根红线-第五根红线:到数据线上稳定一会,就是恢复时间

SARAM的写周期

第一根红线-第二根红线:地址稳定的过程,因为是电流,所以速度不一样

第二根红线-第三根红线:写的过程

第三根红线-第四根红线:写完了需要稳定一会

ROM存储系统

在电脑中,大家都知道有内存和硬盘之说,其实内存就是一种RAM技术,而ROM则类似于硬盘技术,两者都是存储器,只是RAM的速度要远远高于ROM的速度。

在手机中,RAM是指手机内存,属于手机内部存储器,属于随机存储,速度高于ROM,对于手机配置性能起着重要的决定性,另外掉电后,数据被清空,比如手机运行着QQ与其它软件,重启手机后,软件就没有处于登录状态。

辅存,他是不会直接和CPU直接进行通信的,是通过I/O接口与CPU进行通信的,控制I/O接口的指令存储在RAM中。

我们需要一个直接和CPU进行通信的存储器,而且不会一断电就丢失信息,就是只读存储器,比如:它可以指出操作系统在辅存的哪个位置,然后通过I/O接口调到RAM中。

ROM可以存放一些开机之后必要的信息。

存储器的基本概念的总结和补充

存储器分为两种,一种可以直接和CPU进行交流,叫主存=RAM+ROM,或内存

另一种是辅存(外存)

又为了提高效率,增加了cache。

这些都是用来存储二进制信息的,可以使用不同的材料。

直接存取是先定位一个小区域,在这个小区域内进行顺序存取,介于另外两种形式之间

再整理一下

存储器的性能指标

存储器的层次化问题

Cache和主存主要解决CPU和主存速度不匹配的问题,CPU的运算速度很快,主存读写的速度跟不上CPU的数据吞吐速度,所以需要Cache,现在一般都有好几级的Cache,由硬件自动完成。

1648

1648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?