STM32 FSMC驱动SRAM

文章目录

1. 简介

正点原子战舰 / 探索者开发板 板载一颗 1M 字节容量的SRAM芯片:XM8A51216,满足大内存使用需求。

16位宽512K(512*16,即1M字节),使用8080并口时序

- 高速:具有最高访问速度15ns

- TTL电平兼容

- 低功耗:80MHz时55mA,待机电流 20mA

- 全静态操作:不需要刷新和时钟电路

- 三态输出

- 字节控制功能:支持高/低字节控制

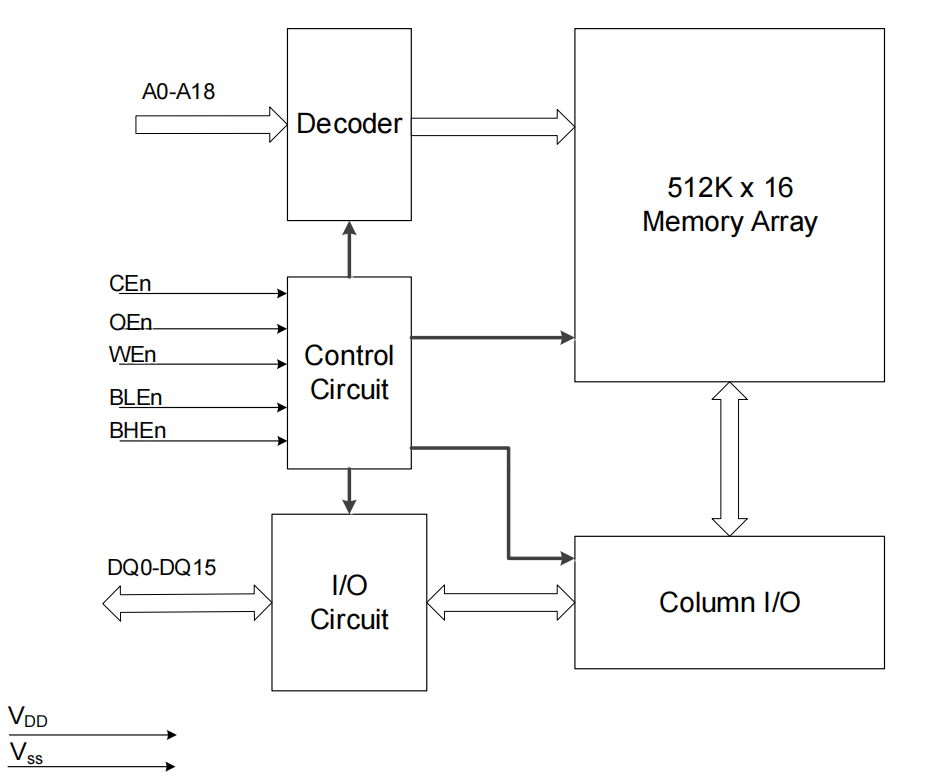

2.结构框图

每个地址存放16Bit数据,总容量1MB

- A0~18:19根地址线,2^19 = 512K

- DQ0~15:16根数据线,输入/输出

- CEn:芯片使能信号,低电平有效

- OEn:输出(读)使能信号,低电平有效

- WEn:写使能信号,低电平有效

- BLEn:低字节控制信号(DQ0~7有效)

- BHEn:高字节控制信号(DQ8~15有效)

3. 8080时序

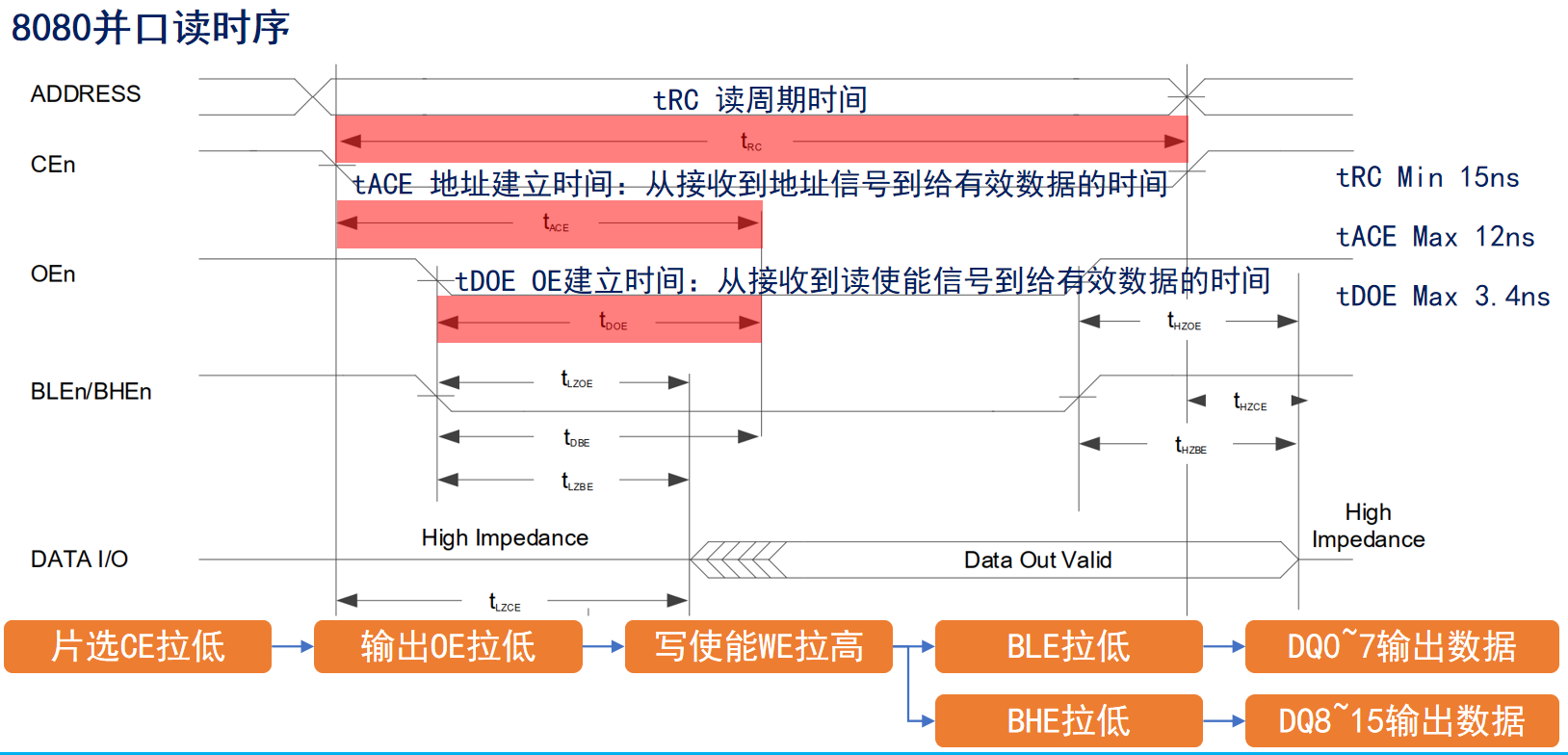

3.1 读时序

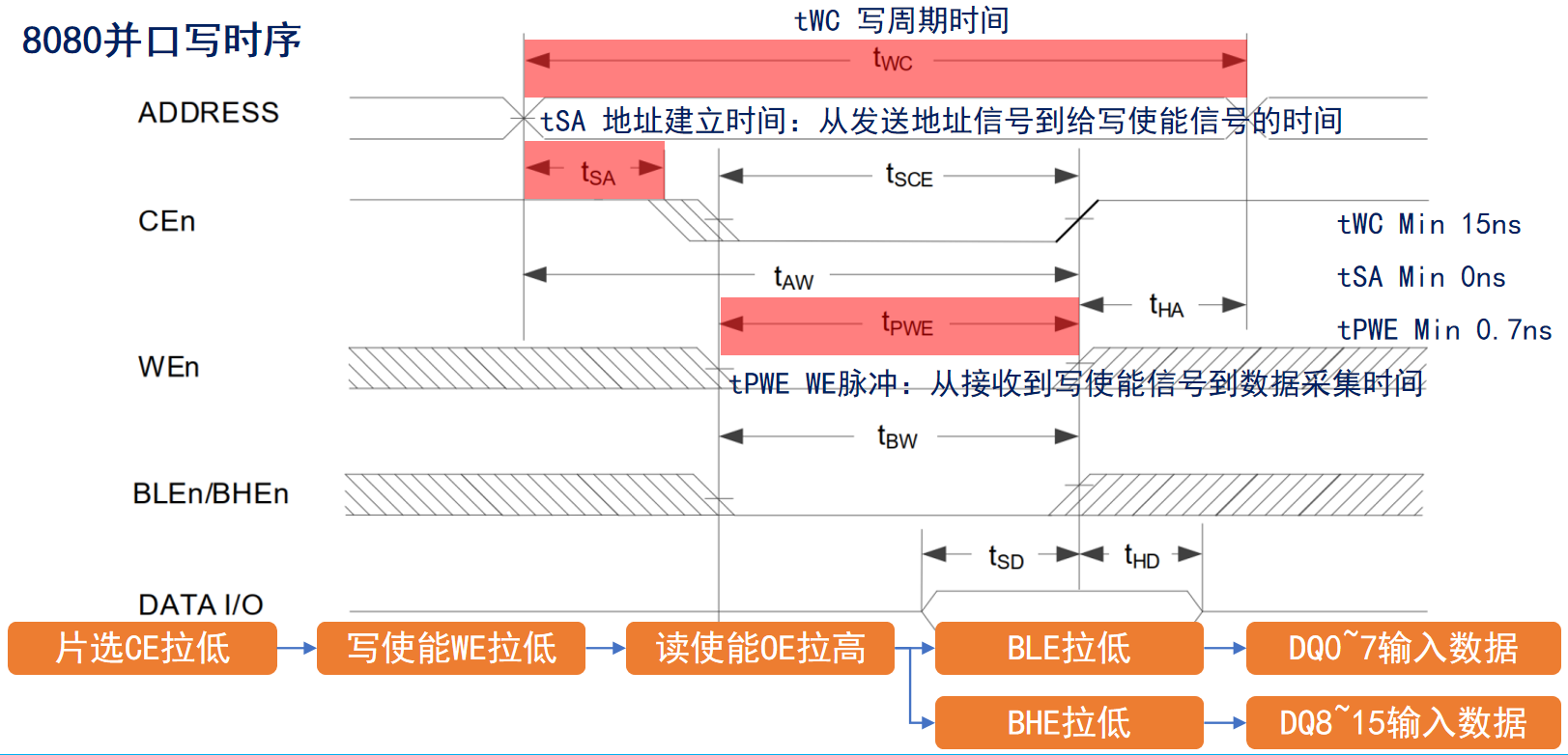

3.2 写时序

4. SRAM 读写操作步骤

- 设置地址信号线:发出要访问的存储器目标地址

- 控制片选信号:选中器件

- 决定数据操作方式:读操作,控制读使能信号OE表示读数据;写操作,控制写使能信号WE表示写数据

- 设置获取数据方式:掩码信号BLE和BHE指示要访问目标地址的高、低字节部分

- 获取数据:读过程,存储器通过数据线向主机输出目标地址数据;写过程,使用数据线向存储器目标地址写入目标数据

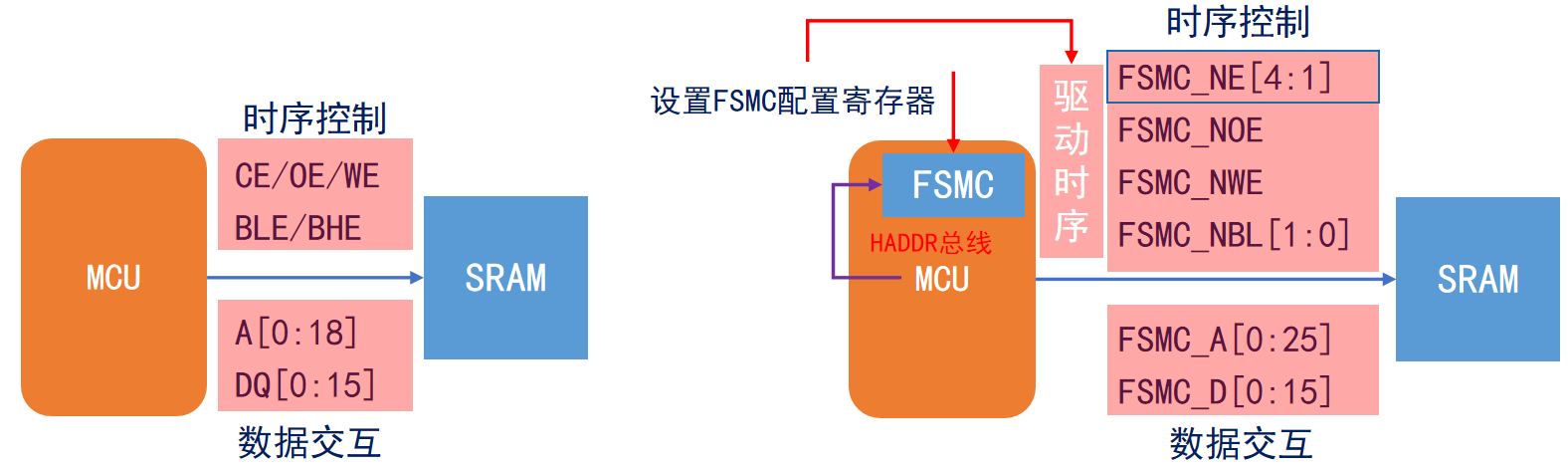

5. FSMC驱动SRAM

如图可见,我们可以通过IO口模拟出时序驱动SRAM,也可以通过配置FSMC驱动SRAM

FSMC时序介绍

| 访问模式 | 对应的外部存储器 | 设置参数 |

|---|---|---|

| 模式1 | SRAM/CRAM | ADDSET、DATAST |

| 模式A | SRAM/PSRAM(CRAM) | ADDSET、DATAST |

| 模式B/2 | NOR FLASH | ADDSET、DATAST |

| 模式C | NOR FLASH | ADDSET、DATAST |

| 模式D | 带地址扩展的异步操作 | ADDSET、DATAST、ADDHLD |

此处我们选择模式A

5.1 配置FSMC时序

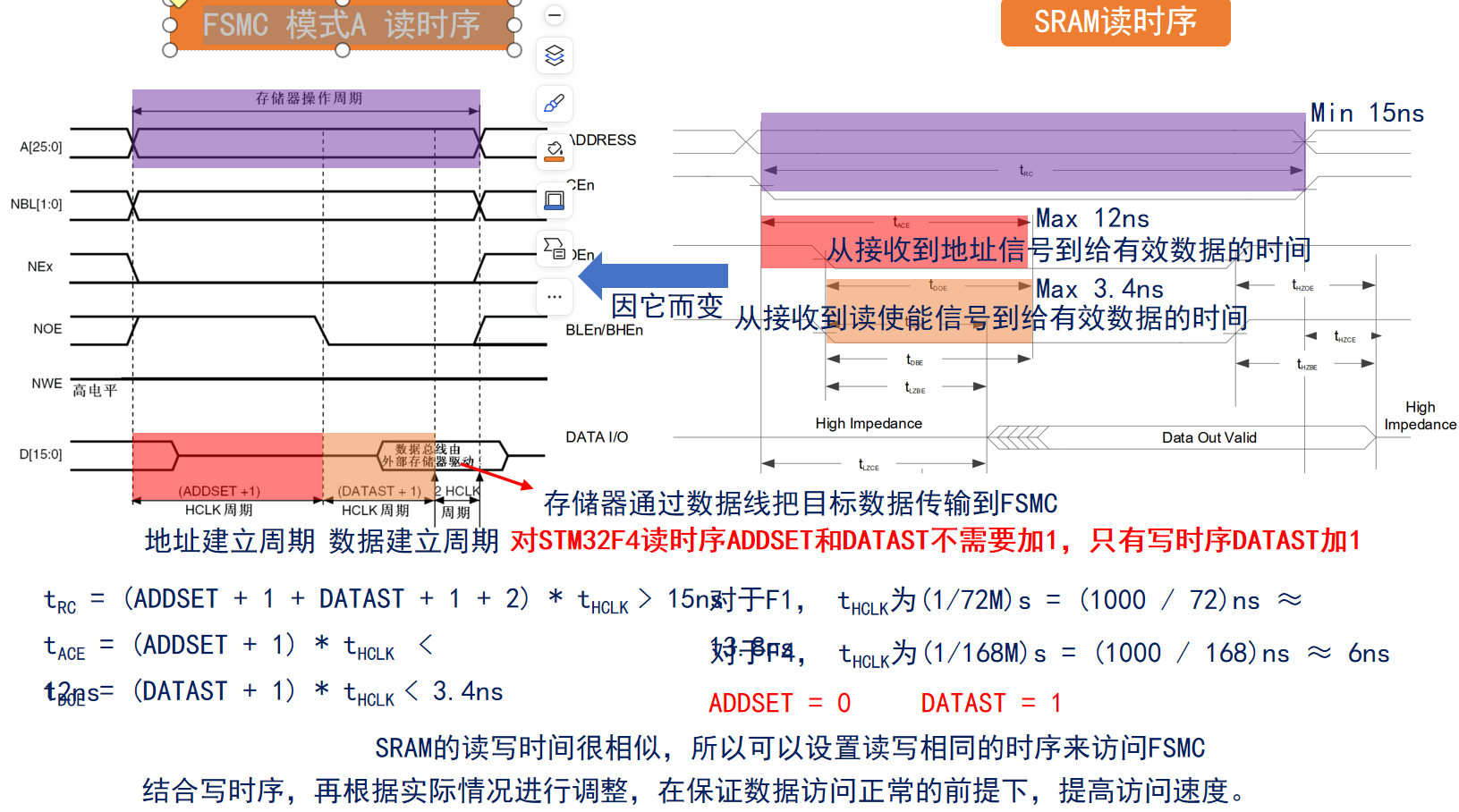

5.1.1 FSMC 模式A 读时序

通过配置ADDSET=0,DATAST=1,就可以成功模拟出读时序

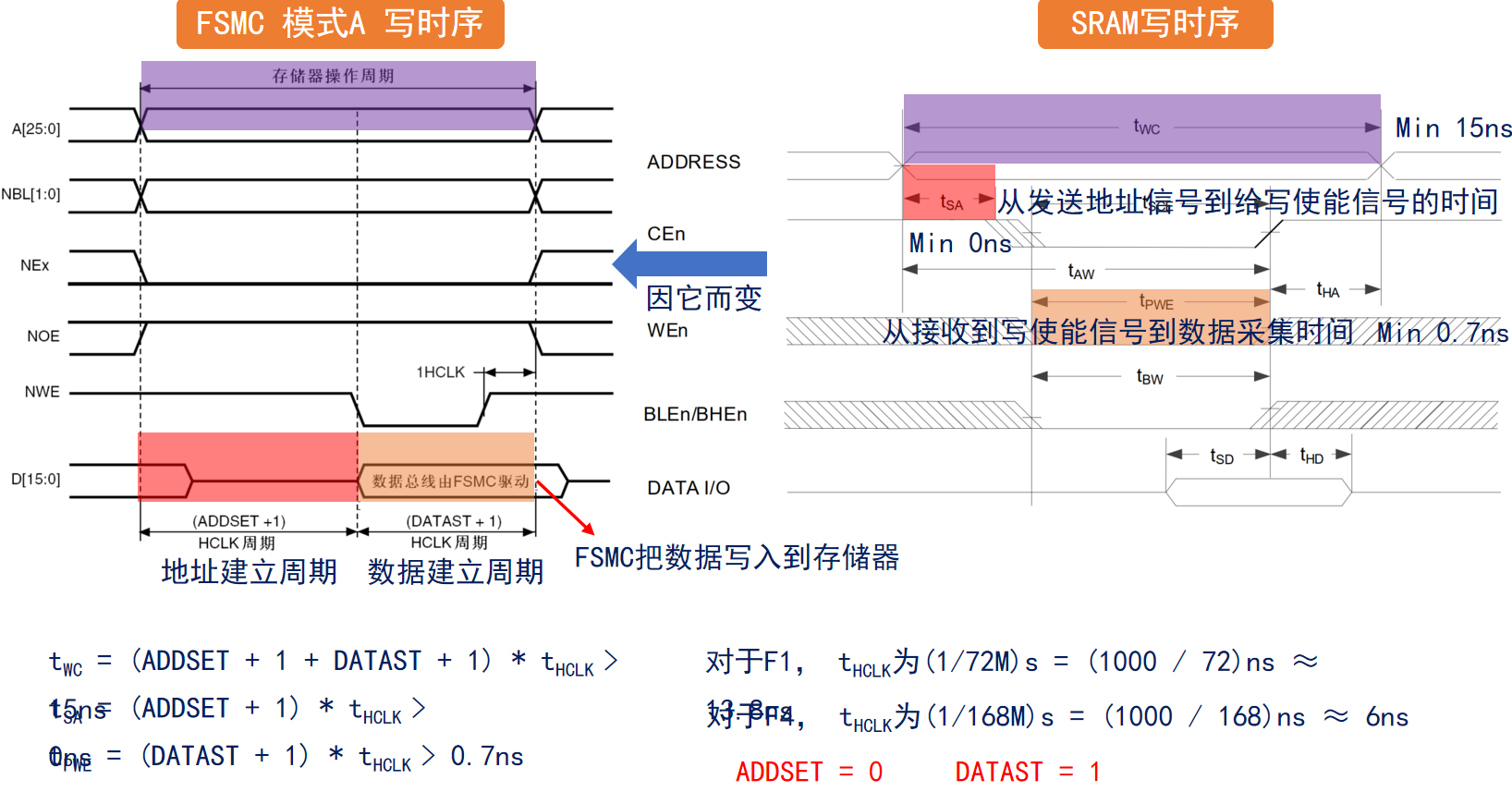

5.1.2 FSMC 模式A 写时序

通过配置ADDSET=0,DATAST=1,就可以成功模拟出写时序

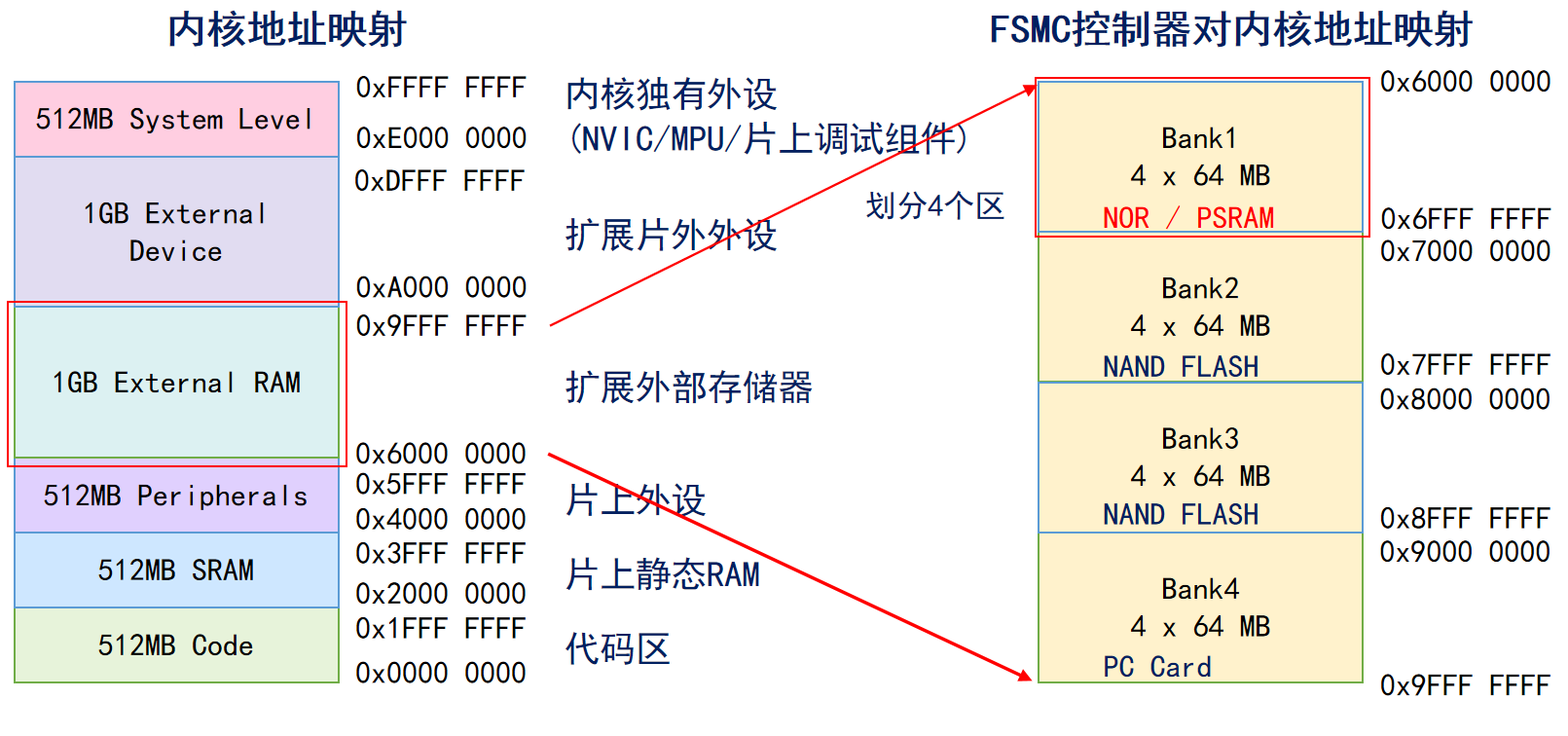

5.2 内核地址映射

从图上我们可以看出,STM32将0x6000 0000 - 0x9FFF FFFF地址划分为扩展外部存储器区域,这个区域就是由FSMC进行地址映射。

SRAM选择Bank1,通过对FSMC映射出来的地址进行读和写操作,就能控制SRAM芯片进行读和写

*(uint16_t *)(SRAM_BASE_ADDR + addr) = data; 向SRAM某个地址写入数据

data = *(uint16_t *)(SRAM_BASE_ADDR + addr);向SRAM某个地址读取数据

SRAM_BASE_ADDR 为0x6000 0000 -0x6FFF FFFF之间区域的一个地址 addr为地址偏移量

6. 配置驱动代码实例

通过HAL_SRAM_Init函数进行配置FSMC

HAL_StatusTypeDef HAL_SRAM_Init(SRAM_HandleTypeDef *hsram, FSMC_NORSRAM_TimingTypeDef *Timing, FSMC_NORSRAM_TimingTypeDef *ExtTiming)

我们接下来看一下他的传参

第一个传参SRAM_HandleTypeDef *hsram

#if (USE_HAL_SRAM_REGISTER_CALLBACKS == 1)

typedef struct __SRAM_HandleTypeDef

#else

typedef struct

#endif /* USE_HAL_SRAM_REGISTER_CALLBACKS */

{

FSMC_NORSRAM_TypeDef *Instance; /* 寄存器基地址 */

FSMC_NORSRAM_EXTENDED_TypeDef *Extended; /* 扩展模式寄存器基地址 */

FSMC_NORSRAM_InitTypeDef Init; /* SRAM初始化结构体*/

HAL_LockTypeDef Lock; /*!< SRAM locking object */

__IO HAL_SRAM_StateTypeDef State; /*!< SRAM device access state */

DMA_HandleTypeDef *hdma; /*!< Pointer DMA handler */

#if (USE_HAL_SRAM_REGISTER_CALLBACKS == 1)

void (* MspInitCallback)(struct __SRAM_HandleTypeDef *hsram); /*!< SRAM Msp Init callback */

void (* MspDeInitCallback)(struct __SRAM_HandleTypeDef *hsram); /*!< SRAM Msp DeInit callback */

void (* DmaXferCpltCallback)(DMA_HandleTypeDef *hdma); /*!< SRAM DMA Xfer Complete callback */

void (* DmaXferErrorCallback)(DMA_HandleTypeDef *hdma); /*!< SRAM DMA Xfer Error callback */

#endif

} SRAM_HandleTypeDef;

我们主要配置*Instance,*Extended,Init

其中FSMC_NORSRAM_InitTypeDef Init配置如下

typedef struct

{

uint32_t NSBank; /* 存储区块号 */

uint32_t DataAddressMux; /* 地址/数据复用使能 */

uint32_t MemoryType; /* 存储器类型 */

uint32_t MemoryDataWidth; /* 存储器数据宽度 */

uint32_t BurstAccessMode; /* 设置是否支持突发访问模式,只支持同步类型的存储器 */

uint32_t WaitSignalPolarity; /* 设置等待信号的极性 */

uint32_t WrapMode; /* 突发模式下存储器传输使能 */

uint32_t WaitSignalActive; /* 等待信号在等待状态之前或等待状态期间有效 */

uint32_t WriteOperation; /* 存储器写使能 */

uint32_t WaitSignal; /* 是否使能等待状态插入 */

uint32_t ExtendedMode; /* 使能或者禁止使能扩展模式 */

uint32_t AsynchronousWait; /* 用于异步传输期间,使能或者禁止等待信号 */

uint32_t WriteBurst; /* 用于使能或者禁止异步的写突发操作 */

uint32_t PageSize; /* 设置页大小 */

} FSMC_NORSRAM_InitTypeDef;

我们只需要配置NSBank,DataAddressMux,MemoryType,MemoryDataWidth,WriteOperation,ExtendedMode即可

接下来看第二个参数FSMC_NORSRAM_TimingTypeDef *Timing

typedef struct

{

uint32_t AddressSetupTime; /* 地址建立时间 */

uint32_t AddressHoldTime; /* 地址保持时间,模式A无效 */

uint32_t DataSetupTime; /* 数据建立时间 */

uint32_t BusTurnAroundDuration; /* 总线周转阶段的持续时间 */

uint32_t CLKDivision; /* CLK时钟输出信号的周期 */

uint32_t DataLatency; /* 同步突发NOR FLASH的数据延迟 */

uint32_t AccessMode; /* 异步模式配置 */

} FSMC_NORSRAM_InitTypeDef;

将配置ADDSET = 0,DATAST = 1,AccessMode=FSMC_ACCESS_MODE_A

2663

2663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?