名称:16位原码乘法器设计Verilog代码Quartus AC101-EDA开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

请基于FPGA(芯片可自选)设计一个16位原码乘法器(即输入信号都为16bits的数据),要求其利用简单的加法运算、逻辑运算移位运算实现乘法运算功能,且原码乘法器的输入由上位机通过串口提供,并将运算结果通过串口发送回上位机进行显示。各部分分数(总分100分)如下:

(1)完成电路功能仿真;(50分)

(2)完成原码乘法器的电路性能分析,包括系统主频、资源消耗电路功耗(10分)

(3)完成电路时序仿真;(10分)

(4)完成电路的板级实现与验证(30分)

本代码已在AC101-EDA开发板验证,AC101-EDA开发板如下,其他开发板可以修改管脚适配:

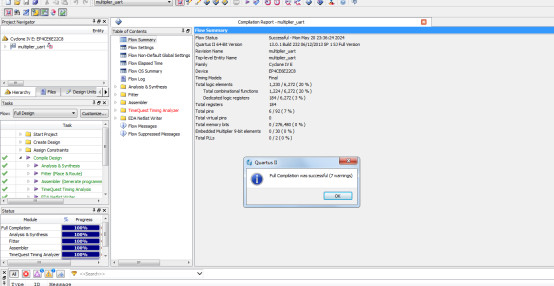

1.工程文件

2.程序文件

3.程序编译

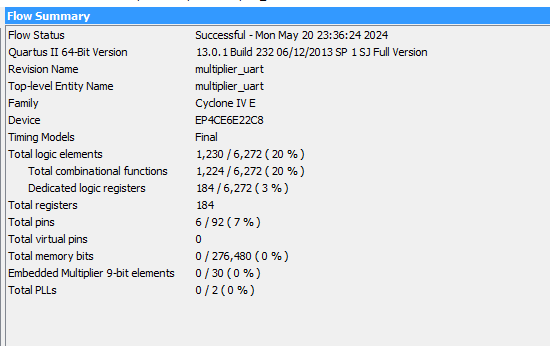

资源消耗

系统主频:50MHz

电路功耗:58.83mW

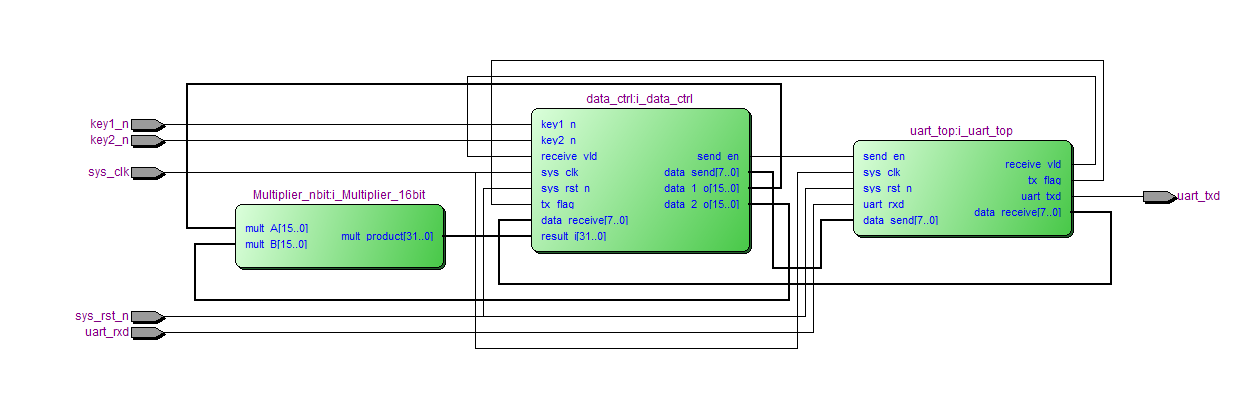

4.RTL图

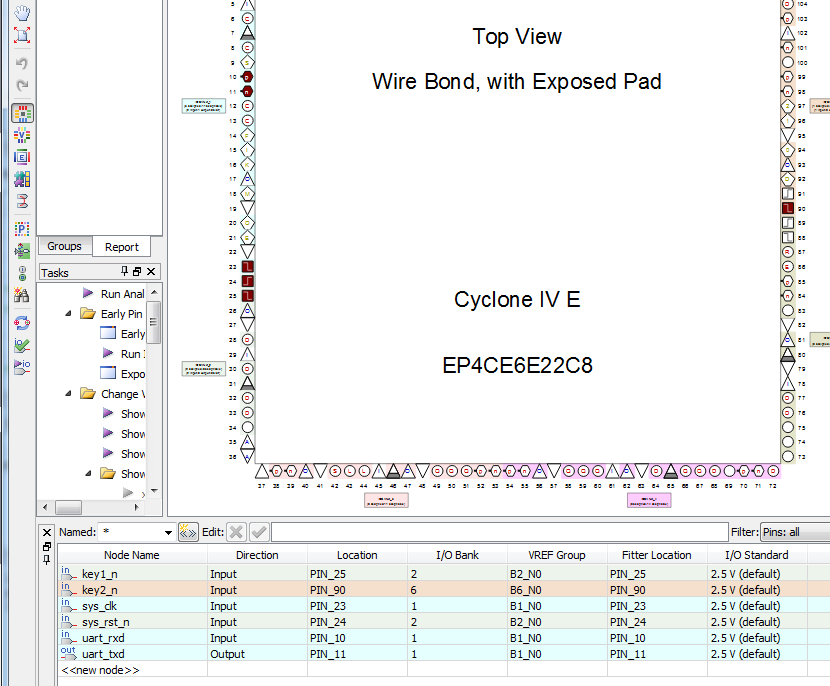

5.管脚分配(约束)

6.仿真图

乘法器仿真

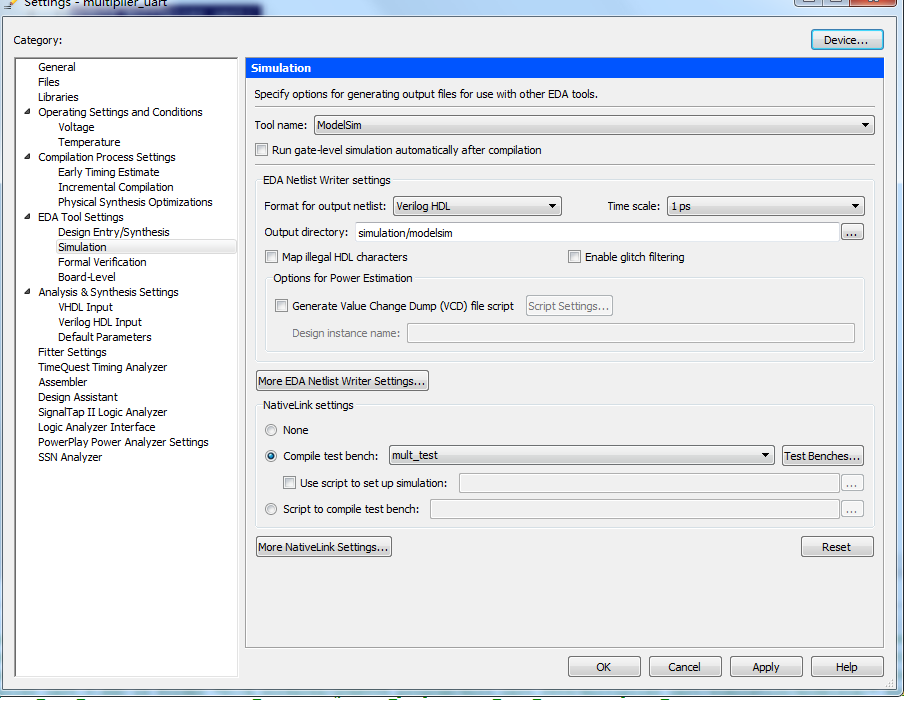

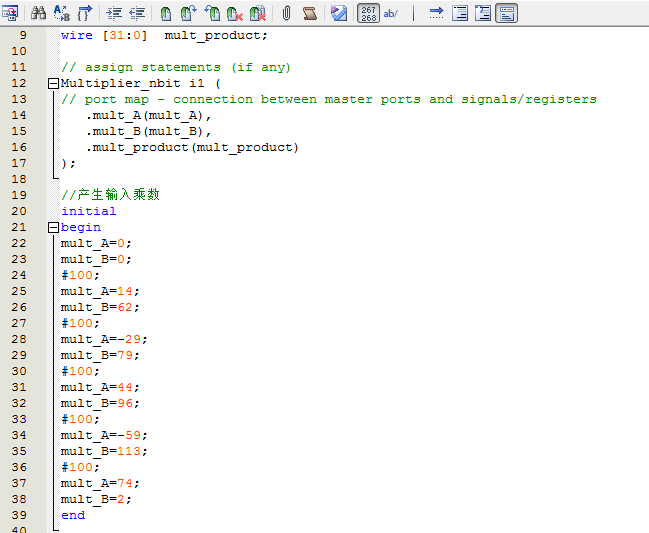

Testbench(仿真脚本)

仿真图

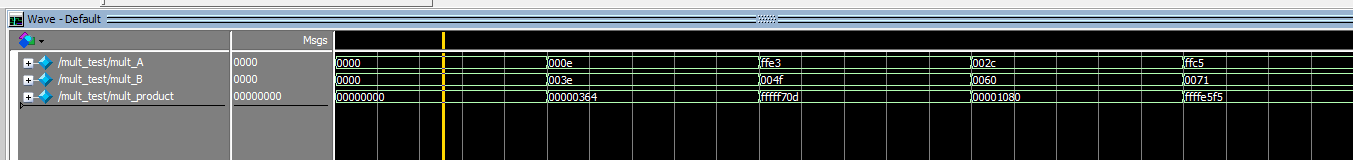

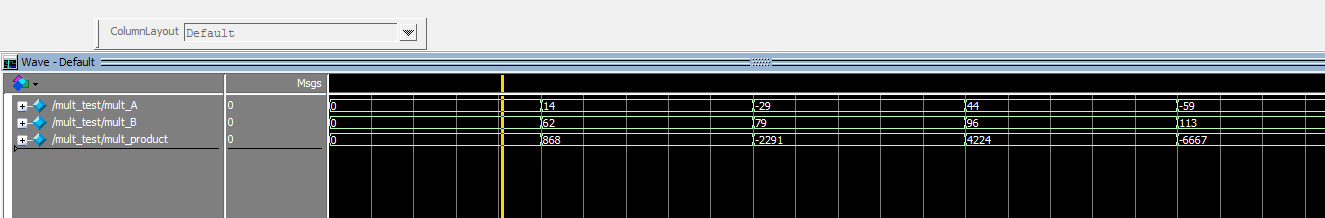

十六机制显示

十进制显示

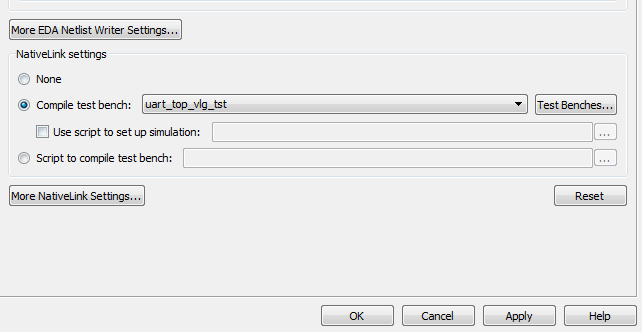

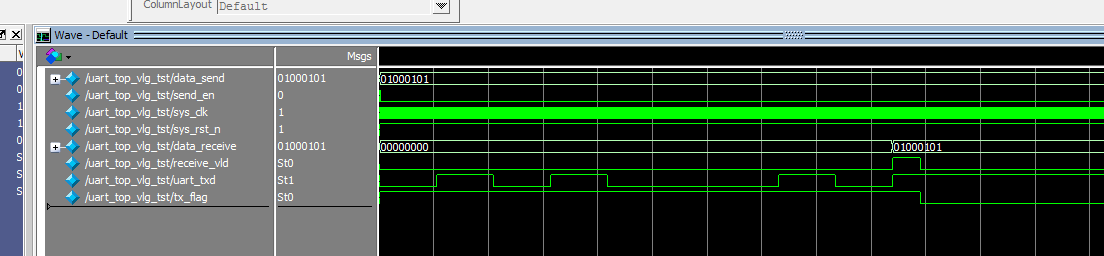

串口收发仿真

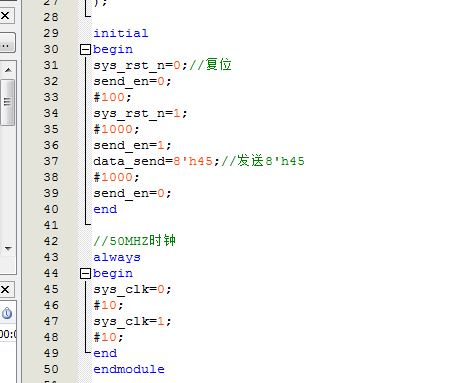

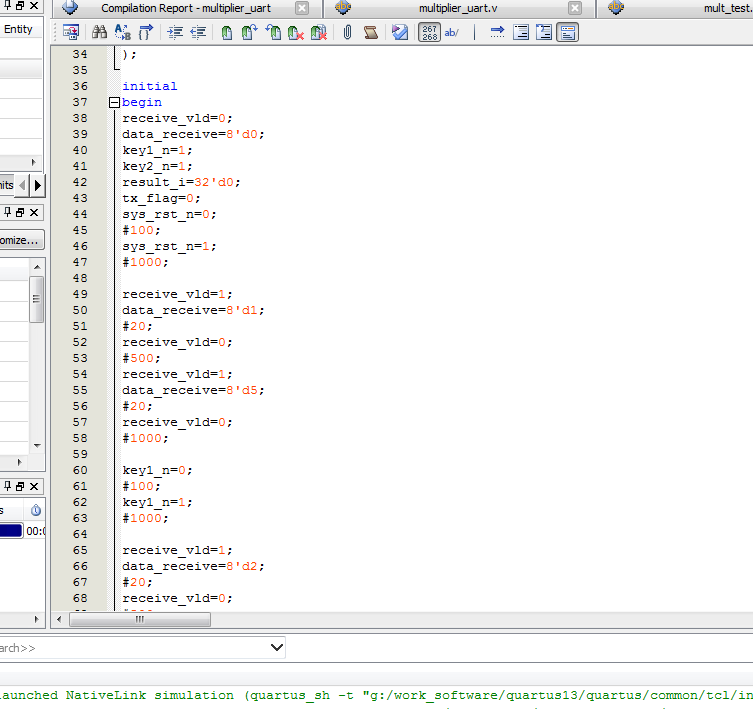

Testbench(仿真脚本)

仿真图

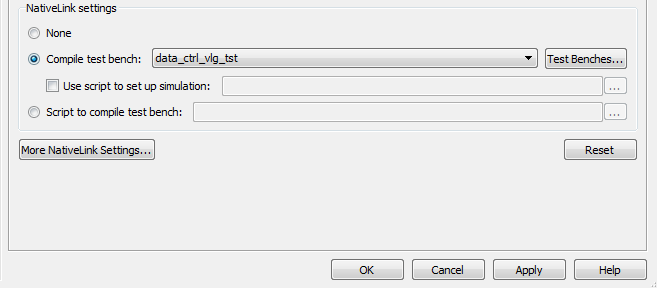

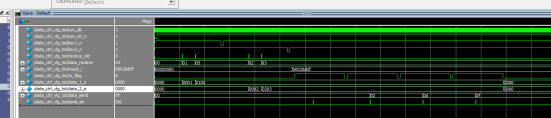

数据处理模块仿真

Testbench(仿真脚本)

仿真图

十六进制显示

部分代码展示:

//booth算法原理

//假设乘数和被乘数均为 n 位,那么 Booth 算法的具体执行过程以下六个步骤:

//(1) 设置一个 2n+1 位的 p 空间,并将初始化为 0;

//(2) 将乘数填入 p[n:1]中;

//(3) 从 p 空间的最低位依次开始向左扫描,每次扫描两位,并判断所扫描的两位二进制数为何种情况;

//(4) 判断 p[2n]位,如果是逻辑 0 右移一位补 0,如果是逻辑 1 就右移一位补 1;

//(5) 重复步骤(3) ,循环 n 次;

//(6) 最终 p 空间的 p[2n:1]就是乘数和被乘数的乘积。

//32位乘法器

module Multiplier_nbit(mult_A, mult_B, mult_product);

parameter width=16;

input [width-1:0] mult_A;//输入乘数A

input [width-1:0] mult_B;//输入乘数B

output [width+width-1:0] mult_product;//乘积

reg [width+width-1:0] mult_product;

integer Count;

reg [width+width:0] PA,right;//设置一个 2n+1 位的 p 空间

always @ (mult_A or mult_B)

begin

PA[width+width:0]={16'b0,mult_A,1'b0}; //将乘数{mult_product, mult_A, 1'b0}填入 p[n:1]中

for(Count=0;Count<width;Count=Count+1)//循环width次

begin

case(PA[1:0])

2'b10:-mult_B,右移一位(有符号数移位)

begin

//PA=PA-mult_B ;

PA[width+width:width+1]=PA[width+width:width+1] - mult_B[width-1:0];//PA=PA-mult_B ;

right=(PA[width+width]==0)?{1'b0,PA[width+width:1]}:{1'b1,PA[width+width:1]};//判断 p[2n]位,如果是逻辑 0 右移一位补 0,如果是逻辑 1 就右移一位补 1

end

2'b01://+mult_B,右移一位(有符号数移位)

begin

//PA=PA+mult_B

PA[width+width:width+1]=PA[width+width:width+1] + mult_B[width-1:0]; //PA=PA+mult_B

right=(PA[width+width]==0)?{1'b0,PA[width+width:1]}:{1'b1,PA[width+width:1]};//判断 p[2n]位,如果是逻辑 0 右移一位补 0,如果是逻辑 1 就右移一位补 1

end

default://右移一位(有符号数移位)

right=(PA[width+width]==0)?{1'b0,PA[width+width:1]}:{1'b1,PA[width+width:1]};//判断 p[2n]位,如果是逻辑 0 右移一位补 0,如果是逻辑 1 就右移一位补 1

endcase

PA=right;

end

mult_product[width+width-1:0]=PA[width+width:1];//最终 p 空间的 p[2n:1]就是乘数和被乘数的乘积

end

endmodule

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?