各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们说到在电源完整性分析的目标就是要做到电源的干净、稳定和快速响应,以及针对不同噪声处理的实现方法。今天我们来看看去耦电容的摆放要遵循什么规则。

去耦电容的摆放

在PCB的设计中,使用去偶电容能够有效滤除电源中包含的噪声,电容的摆放是根据容值大小确定,电容的去耦作用是有一定的距离要求,满足去耦半径问题,若电容距离IC的摆放距离超出电容的去耦半径,则电容将失去去耦作用。

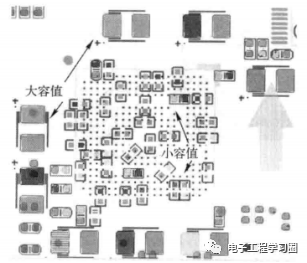

大电容的去耦半径大,小电容的去耦半径小,因此小电容应距离IC的供电引脚尽可能近,大电容可距离IC适当远些,各个规格的去耦电容布局时要均匀布置在IC周围,这样可以使IC所在区域的各电源等级均匀去耦。如下图举例所示:

去耦电容的合理布局

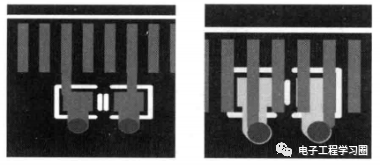

引脚去耦适用于IC引脚较少,且电源引脚与地引脚之间距离较小的情况,如下图所示:

引脚去耦

引脚去耦时,要尽可能缩短焊盘和去耦电容之间引线的长度,避免引入额外的寄生电感。

平面去耦适用于电源引脚与地引脚较多且分布分散的IC去耦,BGA类的IC一般都采用平面去耦方式

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?