目录

1、R52内核架构

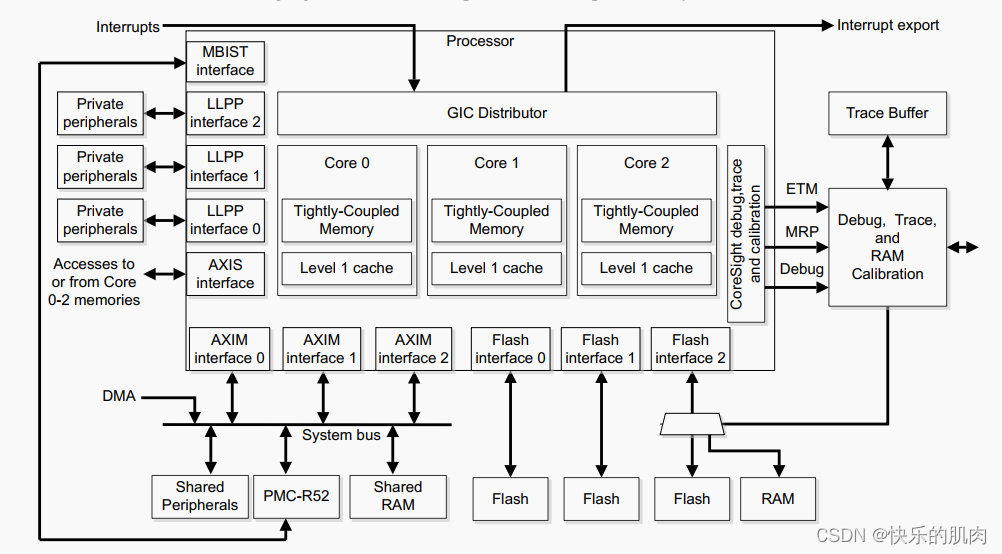

Cottex-R52是一个中等性能的处理器,主要用于汽车以及其他工业领域。其内核架构是Armv8-R AArch32,如下图:

今天我们先来聊聊ArmV8架构。

1.1 ArmV8架构基本概念

Arm本身是精简指令集(Reduced Instruction Set Computer)架构,这种架构:

- 大量统一的寄存器

- load/store架构,其中数据处理操作只对寄存器内容进行操作,而不直接对memory内容进行操作(注意这个特性,特别是在有Cache的时候)

- 简单的寻址模式,所有的加载/存储地址仅由寄存器内容和指令字段决定。

Arm架构支持两个执行状态,AArch64--64bit执行状态,支持A64指令集;AArch32--32bit执行状态在,支持T32和A32指令集。同时Arm根据核的不同定义了三种不同的架构:

- A Application Armv8-A:VMSA(Virtual Memory System Arch)

- R Real-time Armv8-R:基于MPU支持PMSA(Protected Memory system Arch);支持VMSA

- M Microcontroller Armv8-M:仅支持T32

PS:A32:使用32位指令编码的固定长度指令集

T32:这是一个可变长度的指令集,使用16位和32位指令编码

现在我们对V8架构有了初步的认识,知道是干什么的呢?那具体还有什么特性呢?对于V8架构有哪些拓展?进一步的,V7\V8\V9架构之间有什么不同?这些会在以后慢慢阐述,今天主要了解,重点在R52系统寄存器这块。

2、系统寄存器描述

参考Arm® Cortex®-R52 Processor TRM,我们来看看系统寄存器

系统寄存器主要用于控制核的功能实现和状态信息,根据功能,可以分为如下几类:

- 整体系统控制和配置

- MPU的管理和配置

- Cache管理和配置

- 系统性能监测

- GIC CPU接口的管理和配置

在R52中,系统寄存器只能由协处理器(coproc = 0b1111)使用指令MCR\MRC\MRRC\MCRR进行访问。下面来看下系统寄存器的字段定义

| 类别 | 描述 |

| CRn | 系统控制主寄存器号 |

| Op1 | 寄存器访问指令参数 |

| CRm | |

| Op2 | |

| Name | 寄存器或操作名 |

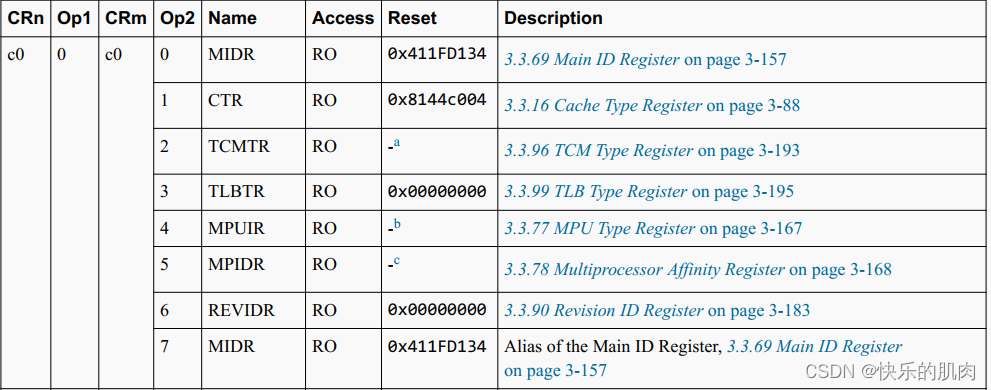

从手册上看,系统寄存器包括C0-C15、AArch32 等寄存器多达几十个,我们这里选用一个来举例说明

例如,MIDR,用于描述设备ID等,该寄存器属于只读,那么该如何访问该寄存器呢?

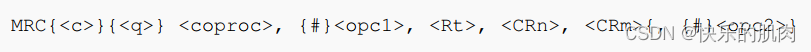

格式如下:

MRC p15,0,<Rt>,c0,c0,0

根据内核手册语法格式,

我们来一一对应,<coproc> = p15,opc1 = 0,Rt = 返回值,CRn = c0,CRm = C0,opc2 = 0

如果想要访问MPIDR呢,汇编应该这样写

MRC p15,0,<Rt>,c0,c0,5

3、代码解析

在上述基础上,可以得出一个规律,访问系统寄存器的汇编可以封装出一个公共函数

例如

#define __set_CP(cp, op1, Rt, CRn, CRm, op2) __ASM volatile("MCR p" # cp ", " # op1 ", %0, c" # CRn ", c" # CRm ", " # op2 : : "r" (Rt) : "memory"

357

357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?