LIBRARY IEEE; --调用库

USE IEEE.STD_LOGIC_1164.ALL; --调用库

ENTITY selection IS --开始定义电路模块

PORT(a1,a2,a3,s0,s1 : IN STD_LOGIC; --输入信号

ou : OUT STD_LOGIC); --输出信号

END ENTITY selection; --定义结束电路模块

ARCHITECTURE Muxk OF selection IS --结构体

SIGNAL y1:STD_LOGIC; --定义一个全局变量(信号),负责传输选择器1的结果

BEGIN --结构体开始

Mux21a1:PROCESS(s0,a2,a3) --要把所有定义的变量写在进程的括号内

BEGIN --进程开始

CASE s0 IS --case语句开始

WHEN '0' => y1<=a2;--如果s0为0则,y1为a的值

WHEN '1' => y1<=a3;--如果s0为1则,y1为b的值

END CASE; --case语句结束

END PROCESS Mux21a1;

Mux21a2:PROCESS(s1,a1,y1) --要把所有定义的变量写在进程的括号内

BEGIN --进程开始

IF(s1='0') THEN ou<=a1;

ELSIF(s1='1') THEN ou<=y1;

END IF;

END PROCESS Mux21a2;

END ARCHITECTURE Muxk;代码用的语言是VDHL。

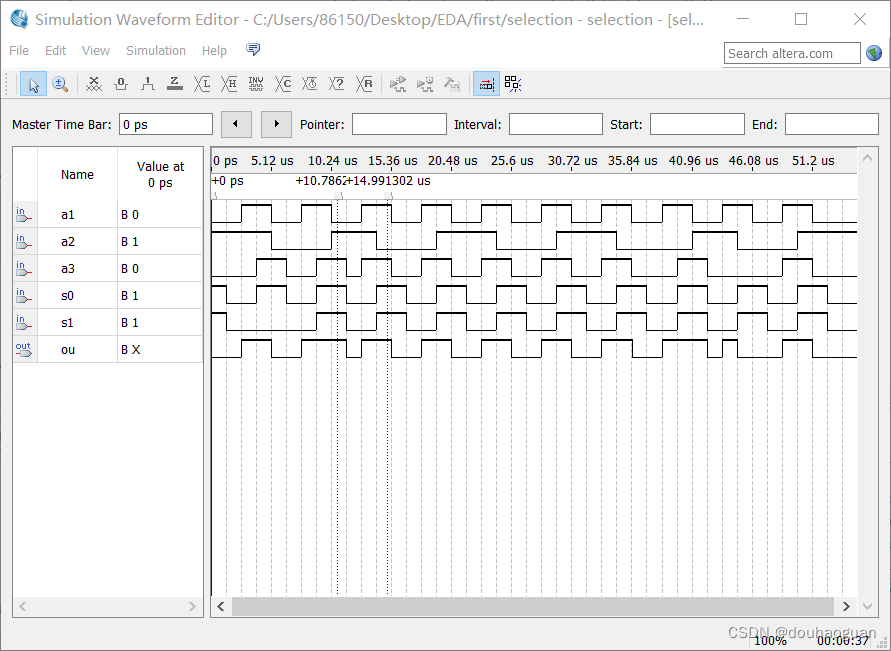

上图为仿真波形图。

代码如有错误欢迎指正。

275

275

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?