设计

功能分析

三个输入,一个输出

信号sel为1时,输出为b,否则为a

新建工程

file–new–verilog HDL

代码段

module mux2_1 (

sel,

a,

b,

out

);

input sel;

input a;

input b;

output out;

assign out = sel?b:a;

endmodule

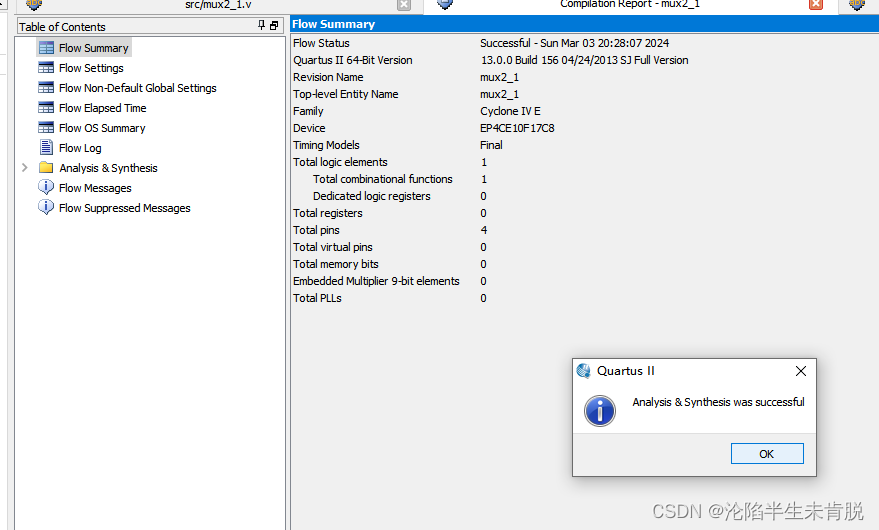

CTRL + K 开始分析综合

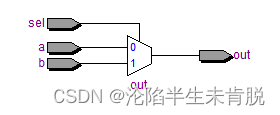

综合电路图

Tools – Netlist Viewers ==RTL Viewer 可查看综合后的电路图

仿真

tb即testbench,测试平台,想象设计的代码放在一个平台上测试

功能仿真代码(前仿真)

给不同时刻的sel不同电平,看输出是否符合预期

timescale 1ns/1ns 设置仿真时间精度,单位为1ns,精度(最小刻度)也是1ns timescale 1ns/1ns

module mux2_1_tb;

reg s0,s1,s2;

wire led;

mux2_1 inst0(

.a(s0),

.b(s1),

.sel(s2),

.out(led)

) ; #将设计的mux2_1模块例化为inst0,原来的input例化为reg型,output例化为 wire 型

initial begin

s2 = 0;s1=0;s0=0;

#20;

s2 = 0;s1=0;s0=1;

#20;

s2 = 0;s1=1;s0=0;

#20;

s2 = 0;s1=1;s0=1;

#20;

s2 = 1;s1=0;s0=0;

#20;

s2 = 1;s1=0;s0=1;

#20;

s2 = 1;s1=1;s0=0;

#20;

s2 = 1;s1=1;s0=1;

#20;

end

endmodule

仿真设置

Assignment–settings – EDA Tool Settings – Simulation

compile test bench – new --Test bench and simulation files --选择tb

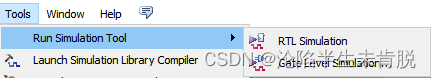

运行仿真

Tools --Run simulation tool --RTLsimulation

隐藏变量的路径

波形分析

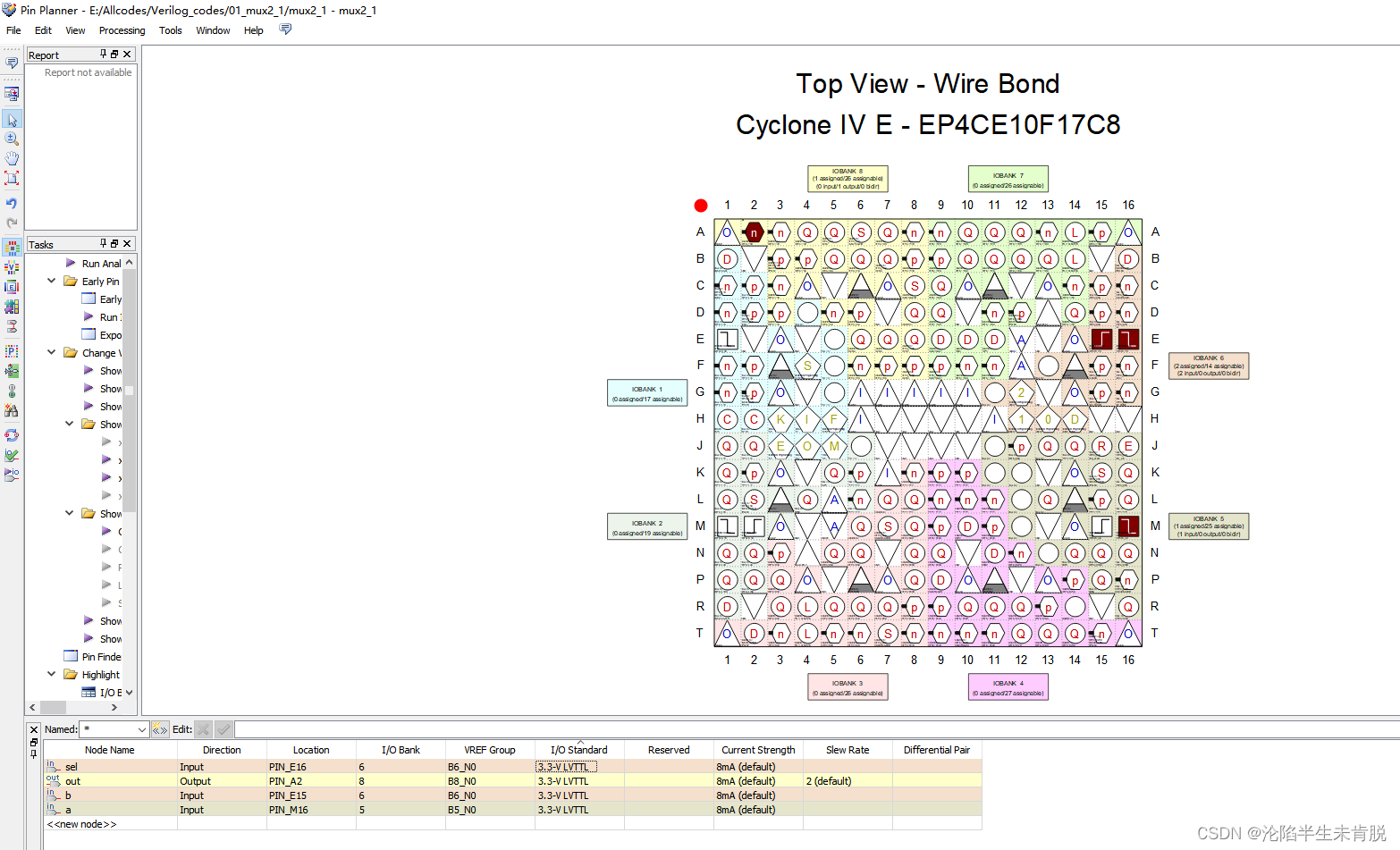

板级验证

Assignment–Pin planer 管脚分配页面

IO标准3.3LVTTL

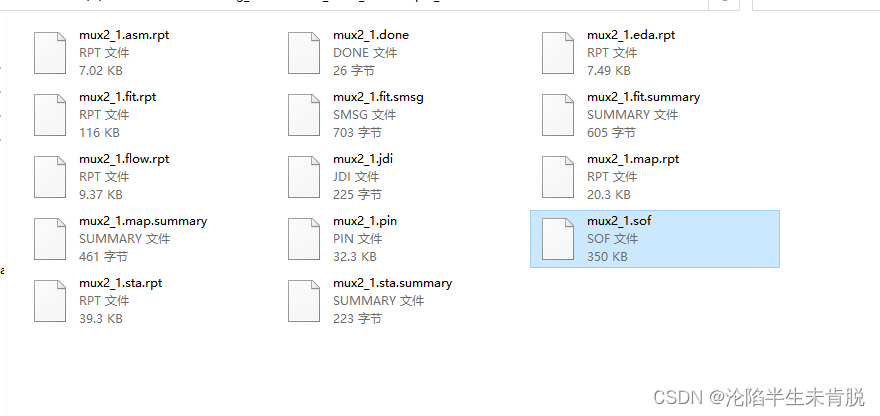

引脚分配后全编译 CTRL+L,全编译完成后,生成的sof文件位于工程存放目录下新生成的output_file文件夹下

.qsf文件包含了所有工程约束

下板操作

Tools --Programmer

硬件设置 USB blaster

add file – ouputfile --.sof文件

实际下板后对未使用的管脚都是分配高电平

在 Assignment --decices -unused pins ,默认是拉高。选择第一个

本文详细介绍了如何使用VerilogHDL设计一个2:1复用器模块,包括模块功能分析、电路图查看、功能仿真实现、管脚分配以及硬件下载流程。作者展示了从新建工程到实际下板操作的完整过程。

本文详细介绍了如何使用VerilogHDL设计一个2:1复用器模块,包括模块功能分析、电路图查看、功能仿真实现、管脚分配以及硬件下载流程。作者展示了从新建工程到实际下板操作的完整过程。

9629

9629

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?